6. SMT BGA设计与组装工艺: BGA封装的标准化

BGA封装的标准化涉及到一系列 的物理变量,包括每个焊球的直径、焊球在元 器件外形内实际位置的定位精度。

一、 BGA⾏业标准

对于更多封装变化的细节,包括机械特征尺寸和允许的物理公差,可参考如下JEDEC开发的BGA封装指南。

1、BGA封装

JEDEC 出版物JEP95,章节4.14定义了球栅 阵列(BGA)封装或者柱栅阵列(CGA)是节 距为1.50、1.27或1.00mm的底部分布有金属球或 圆柱的正方形或长方形封装,封装的本体有一 个带有金属化电路图形的绝缘结构。对于封装本体,半导体芯片安置在上面或下面。在绝缘 结构底部是金属化球/柱状阵列图形,这在封装 本体与配合特征(如印制板)之间形成机械或 电气连接。含有芯片一面可以用各种技术进行 密封以保护半导体。

2、密节距球栅阵列封装

JEDEC出版物 JEP95,章节4.5进行了如下定义:密节距球栅阵 列封装FBGA是节距减小(小于1.00mm)版本 的球栅阵列封装。封装载体有施加了绝缘结构 的金属化电路图形。一个或多个半导体器件连 接于绝缘结构的顶面或底面。在绝缘结构的下 面是金属球图形,以形成从封装本体到印制电 路板接触点的机械或电气连接。含有芯片一面 可以用各种技术进行封装以保护半导体材料。方形FBGA系列的标准允许三种可供选择的连接 节距:0.50、0.65以及0.80mm,同时也规定了四 种器件外形(高度)变化。已增加0.75mm触点 节距并被归纳入芯片级尺寸BGA(DSBGA)封 装指南,因此对于芯片级尺寸器件系列共提供了四种节距。

由元器件底座面至顶部测得的FBGA总外形高度 大于1.70mm。低外形密节距球栅阵列(LFBGA) 是FBGA外形高度降低后的版本。由元器件底 座面至其顶部测得的LFBGA的总外形高度不大于1.2mm。薄外形密节距球栅阵列(TFBGA)是 FBGA外形高度降低后的版本,由元器件底座面 至其顶部测得的总外形高度不会超过1.00mm。超薄外形密节距球栅阵列(VFBGA)是FBGA 外形高度降低后的版本,由元器件底座面至其 顶部测得的总外形高度小于等于0.80mm。

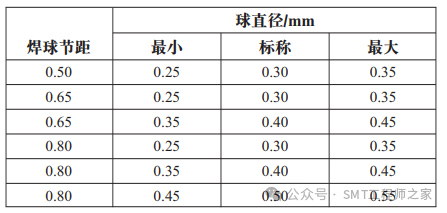

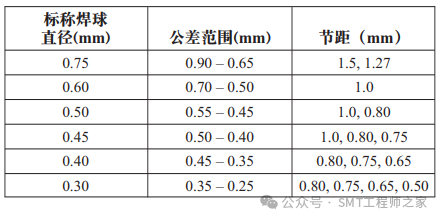

当焊球触点中心间距或节距增加时,JEDEC对于 FBGA的设计指南中允许制造商选择增加焊 球直径(如下表所示)。JEDEC提供的FBGA和 FRBGA设计指南并不支持0.75mm的节距;然而,业界已注册了一些与0.75mm节距不一致的器件,这些并不是JEDEC封装。

选择使用较大的焊球尺寸以适应刚性中介基板封装。较大直径的焊球可以在某种程度上弥补硅芯片和刚性印制电路板结构之间热膨胀系数 (CTE)宽幅不匹配。

3、密节距矩形BGA封装

JEDEC出版物JEP95,第4.6章定义了在封装底部有金属球阵列的密节距矩形球栅阵列(FRBGA)。封装载体或 基板在绝缘结构单面或双面施加有矩形金属化 电路图形。按照JEP95,第4.5章的通用说法来表述,FRBGA本体尺寸用D尺寸和E尺寸来定义。D尺寸是平行于封装主轴所量出的尺寸,而E尺 寸是平行于次轴所量出的尺寸。因此,对于矩形封装,D尺寸的值会比E尺寸大。

4、芯⽚尺⼨BGA封装

JEDEC出版物JEP 95,第4.7章中定义了芯片级尺寸球栅阵列封装 (DSBGA)。芯片尺寸球栅阵列在封装底部有金属化焊球阵列。封装的基板或载体在绝缘结构的 单面或者双面施加有方形或矩形金属化电路图 形。半导体芯片与绝缘结构的上表面相连接。在绝缘结构的底部,金属化焊球阵列图形为封 装本体连接到下一级元件如印制电路板提供了机械和电气连接。含芯片一面可用多种封装技 术对半导体进行保护。基板或载体的尺寸尽可 能接近芯片尺寸。

“芯片尺寸”球栅阵列(DSBGA)是一种本体 尺寸与 特定芯片尺寸尽可能接近的球栅阵列 封装。这种封装也被称为“真正芯片级尺寸” (Real chip-size)球栅阵列或者CSP,封装本体 的尺寸仅可适合特定大小芯片的组装,这些封装 体的尺寸会随着之后芯片大小变化时而变化。封装的外形可以是方形或者矩形;当封装需要 为了适应新的芯片尺寸而进行重新设计时,长 宽比也会发生变化。功能相同但来自于不同供 应商的器件可能有不同的长宽比。DSBGA封装 标准化的控制参数是球阵列的大小和长宽比。

D尺寸和E尺寸定义了DSBGA封装的本体大小。对于带有矩形焊球阵列的封装,阵列决定了尺 寸的方向。D尺寸是平行于焊球阵列主轴测得的 尺寸,而E尺寸是平行于焊球阵列次轴测得的尺 寸。因此对于矩形封装,没有必要如JEDEC JEP 95,4.6章节对FRBGA要求的那样,D尺寸大于E 尺寸。具有方形焊球阵列的DSBGA封装应遵循 通常的“D尺寸大于E尺寸”的JEDEC惯例。D尺 寸和E尺寸的最大值在JEDEC出版物95里定义了以 0.5mm作为递增量,这个数值是通过将DSBGA 的实际尺寸向上靠近下一个0.50mm整数倍获 得 。因此遵照这个规定,D尺寸和E尺寸的形式 通常写为y.00或者y.50。

DSBGA封装的阵列节距没有必要与D或E阵列尺 寸相同。当节距不相同的情况下,相关封装的 尺寸和公差由较小节距的焊球尺寸和公差来主 导。DSBGA封装焊球阵列的控制节距总是小于 1.0mm。JEP95,章节4.7中所描述的DSBGA触 点节距为0.80、0.75、0.65以及0.50mm。

二、焊球节距

BGA的节距主要可分为两组。第一组包括塑料和陶瓷封装外形,其触点节距为 1.50、1.27或1.00mm。第二组为密节距或芯片尺寸 BGA序列,密节距焊球触点节距为0.80、0.75、 0.65、0.50、0.40、0.30 mm,对于芯片尺寸BGA 来说,节距是0.25mm。由于需要将球栅阵列尽 量做小以应对形状参数方面的压力,如今很少有制造商还在提供节距为1.5mm的器件。同时, 尽管允许有节距为0.4mm或更小的焊球,但由于加工困难传统的表面贴组装可能会受到限制。

节距在各种组合的焊球直径选择中起到了重要作用。下表展示了节距在0.5-1.5mm的塑封球栅 阵列的焊球特征;而表3展示了将来DSBGA对于 焊球可能的规格参数。

尽管并非强制,非对称焊球图形在组装过程中 关于方向自动化检测方面有额外的优势。非对 称图形的典型例子为在原本对称的阵列中去除 其中一个位于角落的焊球。

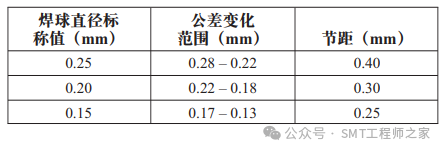

1、未来的焊球触点尺⼨条件

尽管下表中 BGA没有这些尺寸,但未来可预期中的焊球尺寸如下表3所示。

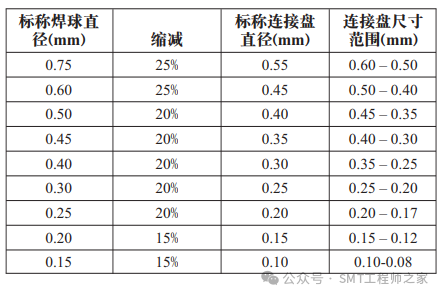

2、连接盘图形的近似算法

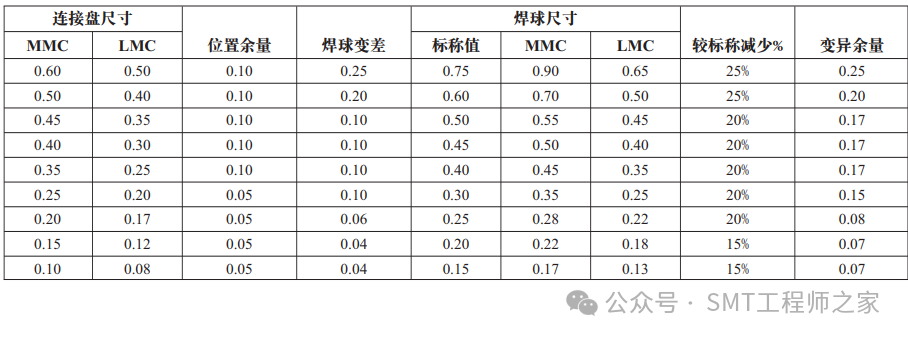

元器件基板 (连接有焊球)的连接盘图形和贴装结构(印 制板)的连接盘图形的直径应该越接近越好。元器件制造厂商认为印制板连接盘或元器件上 焊盘应该略小于焊球直径。连接盘尺寸的减少 量取决于原始焊球尺寸,这常用来确定连接盘 的平均尺寸。在确定标称特性值之间关系时, 应确定连接盘尺寸制造余量,即当焊球直径大 于等于0.40mm时,最大实体条件(MMC)与最 小实体条件(LMC)之差为0.1mm,当焊球直 径小于0.40mm时,该余量也应相应减小。

下表提供了关于连接盘图形的数据及9个焊球直 径的变化。

许多元器件制造商使用阻焊膜限定连接盘(见 6.2.2)。在运用这项技术时,连接盘直径的标称 值应该加上阻焊膜在连接盘上的侵入距离(通常为0.1mm)。阻焊膜开窗大小就可认为是将要连 接的焊球直径,不过实际的连接盘尺寸应略大 以适应阻焊膜限定的概念。需要注意的是由于 连接盘尺寸变大,布线密度相应地就减小了。

三、BGA封装外形

球栅阵列的本体尺寸可分 为以下两种系列外形:方形和矩形。方形封装系 列的尺寸范围为4mm×4mm至50mm×50mm。对于密节距变化,封装尺寸以1.0mm的步长增 加。若尺寸大于21mm×21mm,封装尺寸以2.0mm 至2.5mm的步长增加,并且节距在通常范围之内。当封装尺寸大于21mmX21mm时,几乎没有密节 距器件。矩形BGA系列的尺寸范围为4.0mm至 50mm,随着不同的应用而变化。相比于方形系 列,矩形系列的变化更加丰富。矩形尺寸通常 没有固定的增长步长。该系列通常受到存储器 器件应用的驱动,并且在尺寸上会与芯片尺寸 相近。矩形尺寸对小型应用的特定类别通常是 标准化的。节距小于等于0.8mm的密节距BGA 元器件的本体尺寸通常很少超过21mm。

密节距球栅阵列(FBGA)是节距为0.5至0.8mm 的焊球阵列封装,它有固定尺寸“D(长)”和 “E(宽)”。FBGA更多是之前提到的有固定尺寸 的塑料和陶瓷BGA系列。尽管FBGA通常会在外 形尺寸上只比芯片大20%,但不会每当芯片收缩 时它的外形就改变。

芯片尺寸球栅阵列封装(DSBGA)是节距在0.30 至0.50mm之间的焊球阵列封装,它有可变封装 尺寸“D(长)”和“E(宽)”。DSBGA封装的外形为长方形,与芯片相同,目前广泛应用于闪 存和动态随机存储器件。矩形芯片尺寸(RDS) 外形的“D”尺寸和“E”会随着芯片的缩小而变化。

四、焊球尺⼨关系

整个系统总变差需考虑三个主要问题:定位、焊球公差以及基板公差, 将这三种属性叠加在一起的可得出最差情况分析;然而,因为本标准中有其它连接盘图形,统计意义上的平均值用均方根的值来确定。高引脚数IC以及小外形封装这两种趋势使得厂商 能够同时改进产品的功能和性能。下表可帮助 用户计算各种BGA应用中的连接盘图形尺寸变差,并各自对本标准识别的9个焊球尺寸显示出系统总变差。如前面所提到的,焊球触点直径的 标准标称尺寸为0.15、0.20、0.25、0.30、0.40、 0.45、0.50、0.60以及0.70mm。阵列封装的焊球 触点尺寸会受到总体封装高度、焊球触点节距以及想要的最大焊点可靠性限制的影响。

五、叠装BGA

叠装(PoP)创新技术正优先 用于大量单列直排封装(SIP)应用中。厂商已认识到如果半导体能够各自进行预封装并在装 联之前进行测试,复杂的混装技术能以较高的 良率和更为经济的方式进行生产。PoP应用最常见的解决方案是利用围绕现有的JEDEC FBGA标准阵列封装格式设计的封装分标准(见图4-5)。因为单个封装体在叠装前都进行过完整的测试,所以预封装芯片叠加的风险较小。

决定是否在PCBA级组装前或组装中进行封装叠 装,可能会受到制程中配置灵活性需要的影 响。举例来说,底部封装的供应商为“A”,叠加封装的存储器则可分别由供应商“B”、“C”或 “D”提供。毕竟,存储器功能可以从更多的来源获得,且存储器测试也是有些专业的。此外, 承担的整体质量和可靠性的担忧可以有所减轻。逻辑器件供应商负责逻辑运算功能,存储器件制造商负责各自的存储器功能,板组装厂仅需负责这两者的表面贴装连接。这种供替代的选择有两个好处,它使用户可以指定多种变化(不同的存储器功能、数据传输速率等等)以及可选择第二供应商。

六、共⾯度

表面贴封装的一个关键问题是 触点共面度的局限。BGA封装与其它引线框封装的表面贴元器件的共面度要求有很大不同。 任何BGA的共面度是指元器件触点面高出底座面的距离。 因此简而言之非共面度就是当封装放置在完全平坦的平面时,最高触点与最低触点间的最大距离。该定义表示座落在印制板上的一个封装至少有三个位置与印制板接触。

共面度公差定义了封装最高点到底座面的距离。此尺寸包括间隙高度、封装本体厚度和盖 子厚度(若有)。测量时不包括附属物如散热片 或其它元器件,但是集成的散热块不被认为是附属物。如果封装刚好是层压板基BGA,由于 有要适应较大基板并在公差内维持平面性相关 的问题, 预期会带来额外的共面度问题。这就是 为什么塑封BGA封装的共面度要求是150μm的 部分原因。大多数供应商所希望的BGA共面度 的适用值大约为200μm,但是用户则希望最大值不要超过100μm,不同种类的 BGA有不同的共面度要求。下表中提供了已在 JEDEC注册过的BGA外形的示例。

由于焊球金相结构不同,共面度的数值会随着 JEDEC外形的不同而变化。在低温条件下共晶 (熔点为183°C)焊球会在组装过程中会塌陷, 因此它的共面度要求不会像高熔焊球(熔点为 302°C)那样严格,因为它们在组装过程中不会塌陷。

本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。