天天说卡脖子,7nm体现在晶体管的哪部分你知道吗?

在我们谈到半导体制造的尖端工艺时,总在说 10nm、7nm,那么所谓的 10nm、7nm 究竟是指的晶体管的哪个部分呢?有人说是晶体管间距,有人说是晶体管栅的长度,事实真的是如此吗?

来自面包板社区的明星博主——欧阳洋葱就这一角度发表了自己的见解。

其实我之前发 的时候,就提到过:我们说 7nm 工艺,那 7nm 这数字究竟还存在毛意义?它大概除了用于表现在市场上某一个工艺节点,数字本身已经没有任何意义了。至少,台积电、三星的 7nm 节点上,晶体管并不存在任何一个物理参数是 7nm 的。那它有什么资格叫 7nm 呢?

原本针对这一点,我也挺想花时间去研究一下的。不过前一阵发现 Linus Tech Tips 对此专门发表了一则视频,我觉得讲的特别清楚。这则视频内容构成,也获得了 Intel 两名工程师的协助。作为一名称职的搬运工,我将此视频的内容做浓缩,有兴趣的还是也可以去看看原视频。

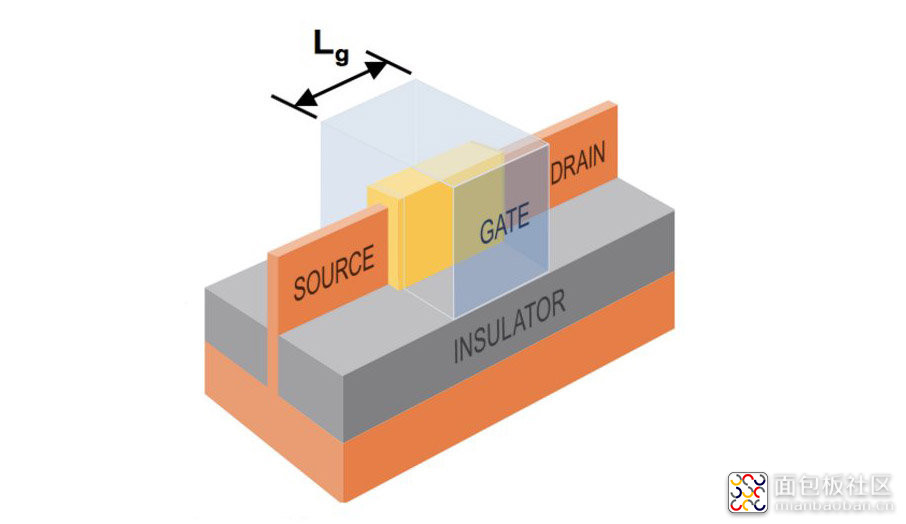

在 1997 年以前,几点几微米,或者几百纳米,那的的确确是指的晶体管上面的 gate 的长度(gate 在大陆叫做栅,在台湾叫做闸,我个人觉得闸是个明显更好的译法),注意是长度(图上标的 Lg,当然了,这已经是 FinFET 结构了,但大致意思不变)。

而在 1997 年以前,工艺数字的步进是以每代是上一代的 0.7 倍为节奏的,因为 0.7x0.7 约等于 0.5,也就是晶体管整体面积相比上一代缩小一倍——就是当年摩尔定律所说,工艺迭代面积小一倍,性能增一倍。当时的工艺在 350nm,也就是 0.35μm。

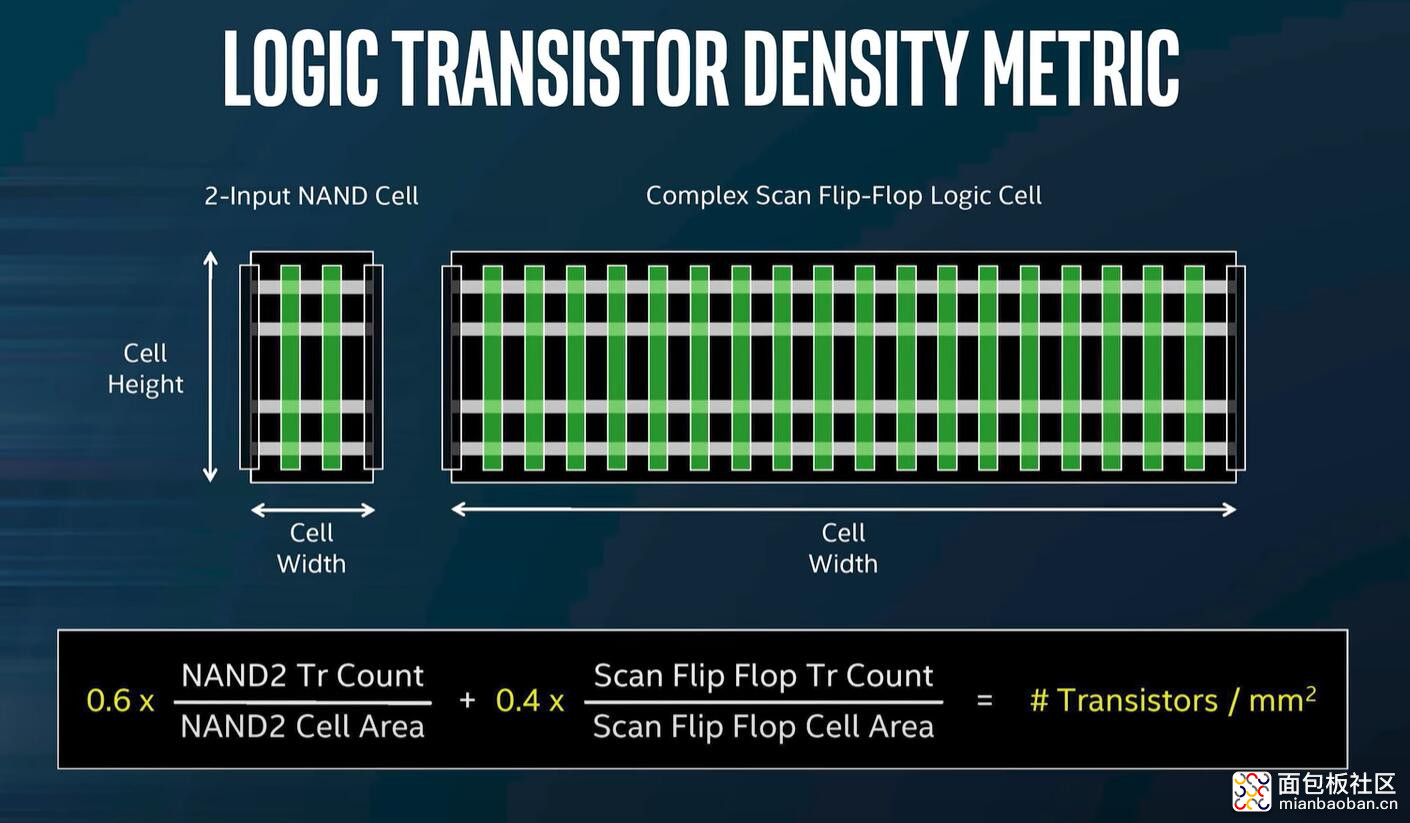

1997 年以后,gate 长度的缩减速度更快了——至少快于 0.7 倍步进这个节奏,但晶体管的其他部分尺寸却未能按照这么快的速度去减小。所以 gate 长度这个时候对于衡量晶体管尺寸的意义已经没那么大了。后续的工艺节点数字,命名开始逐步用于反映一组晶体管构成的单元尺寸(而且通常是最高密度单元库),即便单元本身的尺寸和这个数字相去甚远。

奔腾 3 处理器的 250nm 即是这种规则下的数字,这个数字本身实际上大约是上一代 350nm 的 0.7 倍。因为这代工艺的性能大约等于上一代的两倍——所以取 0.7 倍这个数字也是十分合理的(假装面积也小一倍)。但 250nm 节点的 gate 长度实则大约为 190nm,而不是 250nm。

2012 年,22nm 节点问世,随即而来的是一种新型的晶体管,也就是 FinFET。这种 3D 结构,要用一个数字来衡量尺寸的难度其实就更大了。但业界仍然在遵循 0.7 倍的命名原则,包括 14nm、10nm。到这一时期,这些数字就几乎不存在任何实际意义了——或者说,其实际意义显然已经不大了。

所以看我之前写的 7nm 工艺的文章中,你就会发现,现在的晶体管,并不存在任何一个组成部分的长宽高是 7nm。

而实际上,如果我们要追求晶体管上某部分参数的最小值,恐怕可以看一看 fin 宽度。比如 Intel 的 10nm 工艺,晶体管的 fin 宽度为 7nm——恐怕是整个晶体管上,与 10nm 这个名义上的值最接近的部分了。而其他组成部分的差距就比较大了,比如说相邻 fin 间距是 34nm,gate 长度是 18nm,gate 间距是 36nm 等等。

来源:Intel

不同芯片制造商,针对这个数字节点的态度是不一样的。所以台积电、Intel 之间的这个节点数字就不能直接比较,这个想必很多同学是知道的。比如我们一般认为 Intel 的 10nm 与台积电的 7nm 属于同代工艺;而三星规划中的 4nm 工艺,在晶体管密度上实则可能还比不上 Intel 的 7nm。

现在应该考虑一些更重要的参数,包括晶体管密度,以及材料方面的提升用以加强性能,还有结构上的提升,让电子通过地更快。这些其实在节点数字上不会表达出来,典型如 high-k metal gate、FinFET 结构本身之类的。

有关这部分,欢迎参考我整理的另一篇文章,能够更好地理解,不同半导体工厂在工艺宣传上的差别。

所以别再说出,14nm 是 7nm 两倍(或者面积是 4 倍)这种话了。

[1] 原视频: - Linus Tech Tips

[2] 更多参考: - AnandTech

*国际电子商情对文中陈述、观点判断保持中立,不对所包含内容的准确性、可靠性或完整性提供任何明示或暗示的保证。

本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。