随着先进工艺节点的出现,高性能人工智能 (AI) 处理器的功率不断上升,内核电压则在不断下降。这些发展给电源系统设计人员带来很大挑战,例如需要管理因为供电网络 (PDN) 阻抗压降不断上升的而引起大电流低电压处理器电源引脚间的电压梯度、瞬态性能规格以及功耗等难题。

本文引用地址:

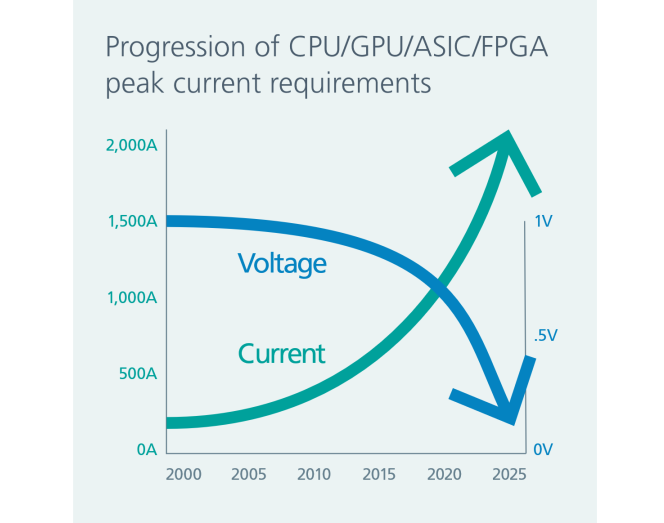

图 1:晶体管几何尺寸及核心电压的降低导致电流需求急剧上升。

以集群计算为例,紧密排列的处理器阵列可提高机器学习的速度和性能。PDN 的复杂性显著增加,因为电流传输必须从阵列的下方垂直进行。设计 PDN 时在负载点使用 分比式电源架构 (FPA™)和电流倍增器, 代替传统平均功率技术,可显著提高性能。这要归功于高品质的负载点 (PoL) 电源组件:高电流密度、组件数更少,而且更为重要的是高度灵活的布置。因此,PoL 电源组件可为 AI 处理器内核和存储器实现横向或垂直传输电流,是因为最大限度降低 了 PDN 阻抗。

现代 GPU 有数百亿个晶体管。增加处理器性能的代价是,呈指数级增长的电源需求。在大多数情况下,供电现已成了计算性能的限制因素。供电不仅涉及配电,而且还涉及效率、规模、成本和散热性能。

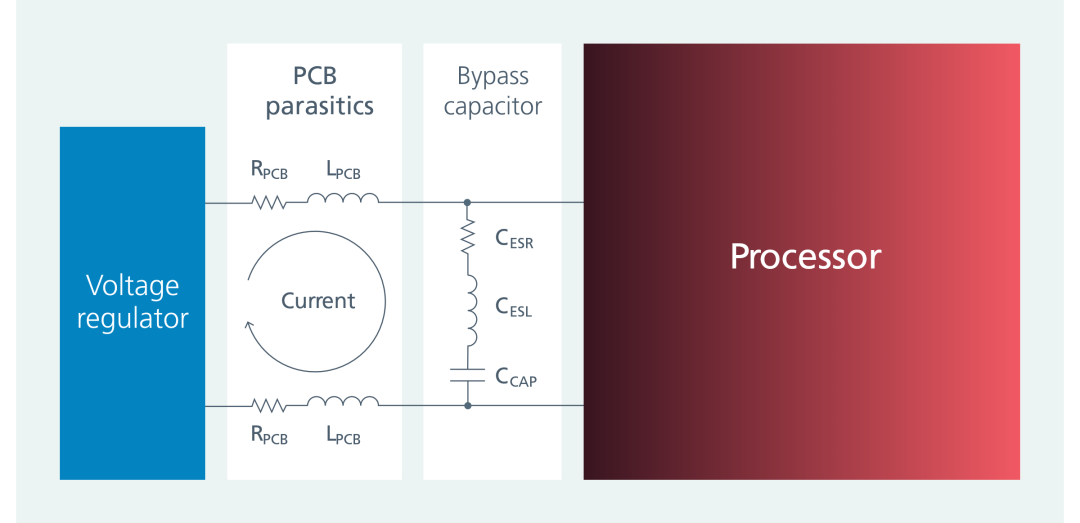

图 2:典型高性能处理器 PDN 的架构。

目前典型的 GPU 峰值电流的需求高达 2000A。为响应这些需求,一些 xPU 公司正在评估多路供电方案,将主要内核供电线路分成五组以上较小电流电源输入。每个线路的 PDN 在经历单独严格稳压的同时,仍须提供大电流,这为 PDN 的密度及其在加速卡上的物理位置带来了压力。

高度动态性的机器学习工作负载将导致持续数微秒的高 di/dt 瞬态,进一步增加了这种复杂性。这些瞬态将在高性能处理器模块或加速卡的 PDN 处理上产生很大挑战。

开放式计算项目 (OCP) 联盟的工作有助于建立基于机架及板卡的处理器开发标准框架。开放式机架标准 V2.2 为主要用于 AI 和机器学习工作负载的开放式加速器模块 (OAM) 定义了 48V 服务器背板和 48V 工作电压。为了保持与原有 12V 系统的兼容性,该标准规定了符合 12 至 48V 及 48 至 12V 要求的性能。

技术进步主要集中在电压值调节的下降趋势、对内核电压精度的要求更趋严格以及电流的上升趋势。在电路板层面,这些因素的影响以多种方式体现。

遇到的峰值电流密度对任何 PCB 都很极端。对能处理这些巨大负载的电源路径进行布线的任务需要格外注意。高动态工作负载会产生尖峰瞬态电压,这些尖峰电压对精密的处理器具有潜在的破坏性。然而,一个处理器电路板有数百个其它的无源组件、存储器以及对运行至关重要的 IC,它们也需要放置它们。

然后就是 I2R 损耗:电源路径长度一定要短,因此电源转换模块应该尽量靠近处理器,处理器就近取得电流并减少热量消耗。

分比式电源架构

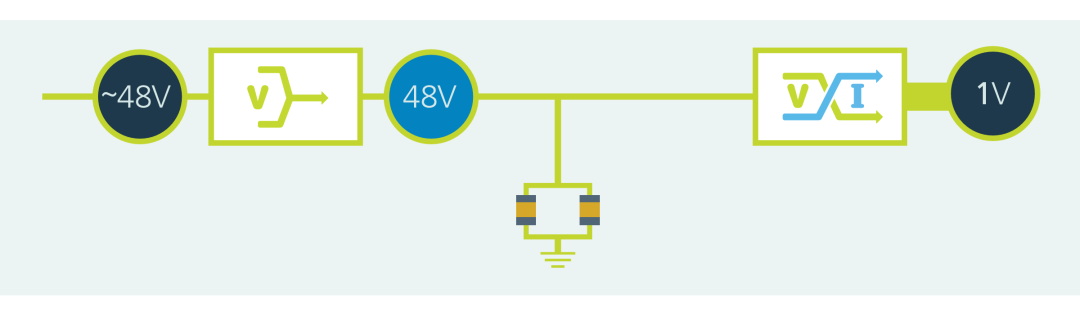

图 3:分比式电源架构 (FPA) 将电源分解为专门的稳压和变压功能。这两个功能都可以单独优化和部署,以提供高功率密度和高效率。

全新的理念、架构、拓扑和技术可提供一条通向更可靠的可扩展 PDN 的道路。 分比式电源架构 (FPA) 是为当下前所未有的高性能计算需求提供更高效电源的基础。

FPA 将电源转换器的任务划分为稳压和变压的不同专用功能。将这两种功能分开,可对其进行单独优化,以实现高效率及高密度。FPA与正弦振幅转换器 (SAC)拓扑共同支撑了多个创新的电源架构,帮助释放当前处理器的高性能。

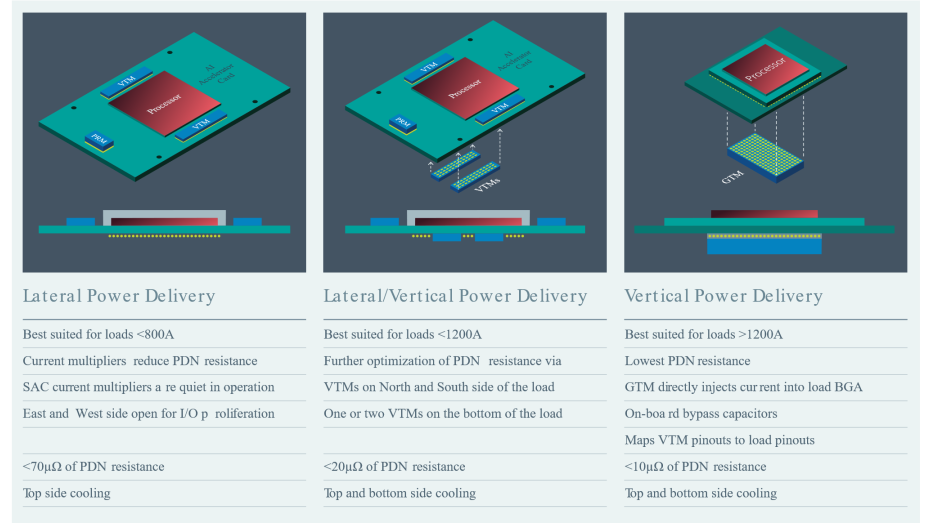

图 4:Vicor 利用 FPA,可通过横向供电 (LPD) 和 (VPDd) 最大限度降低“最后一英寸”电阻。在 LPD 中,两个电流倍增器(Vicor VTM 模块)位于处理器的南北侧或东西侧。该技术适用于标称电压为 0.8V 时约 800A 的负载电流,在 100°C 下,PDN 的相关电阻为 70μΩ。使用这些数字,我们可以计算大约 45W 的功耗。覆盖 2.8 毫米高的电流倍增器和处理器的散热器有助于散热。点击图片放大。

横向供电是一项创新技术,其中两个电流倍增器(Vicor VTM™ 模块)位于处理器的南北侧或东西侧。该技术适用于标称电压为 0.8V 时约 800A 的负载电流,在 100°C 下,PDN 的相关抗阻为 70μΩ。这种架构非常适合为图形加速卡(OAM 或其它产品)供电,并用于为超大规模数据中心或超级计算机机柜 的 ASIC 和 APU 联网。

横向-技术与横向供电技术相似,但也有一点差异:只有 70% 的功率是通过处理器侧面的电流倍增器横向传输的。处理器底部的另一个电流倍增器将剩余 30% 的负载电流直接传输至处理器 BGA。横向和纵向的混合可将 PDN 损耗锐减至原来的四分之一!此外,该技术还可释放电路板空间,以容纳电路板顶部处理器的次级大电流(aux) 轨或 HBM 存储轨。

另一方面,垂直- 横向供电还可通过增加处理器底部的电流倍增器数量来分担接近超过 50% 的负载电流。与横向-纵向方案相比,该技术可使 PDN 损耗再减一半。一个 1200A 的设计现在可实现仅 10µΩ 的 PDN 抗阻,从而可实现小于 14.4W 的功耗。在这种情况下,散热器可在空间允许的情况下为负载的顶部和底部散热。这种架构对于那些必须容纳来自电路板顶部 ASIC 外围的高速信号路由的应用特别有效,因此在那里无法放置更多电源组件,例如 CPO、NPO 以及网络/宽带通信器件。

是以最低 PDN 抗阻在处理器内核低电压下提供大电流的最终方式。在这种情况下,电流倍增器和旁路电容器一起堆叠,形成一个集成电源模块(Pin 针重新适配的变速电流倍增器),可取代旁路电容器组合,直接安装在处理器下面。Vicor GCM 是量身定制的器件,不仅可将电流倍增器插脚引线映射至 AI 处理器 BGA,而且还可提供模块本身所需的所有旁路电容器。这种技术使得那种需要处理器外围的 PCB 布满高速信号路由的应用更为方便,例如CPO(合封光学器件、网络处理器)和高速信号 ASIC 等应用可以利用这种供电技术。

Vicor 架构非常灵活,完全能够适应各种高性能计算场景。Vicor 架构可将主板抗阻锐降至 1/50,还可将处理器电源引脚数锐减至 1/10 以下。利用 FPA功率分比架构,Vicor 可通过将横向供电 (LPD) 和垂直供电 (VPD)完美结合,最大限度减少“最后一英寸”抗阻。所有这些均可帮助处理器实现以前无法实现的性能,为呈指数级增长的 HPC 处理需求提供有力支持。

FPA 架构在电流密度以及降低 PDN 功耗方面是无与伦比的。专有的架构、拓扑和小巧的模块尺寸在电源行业中独一无二。新一代处理器需要能够适应、扩展并能提供高密度电源的电源架构。在电源需求日新月异的动态系统中,结合创新拓扑、稳健而可靠的电源模块必不可少。为了满足这一永恒需求,不仅需要创新,而且还需要能够使用模块化电源来适应和扩展未来应用。

来源:Vicor

作者:Ajith Jain

相关文章

技术咨询

技术咨询 代买器件

代买器件 商务客服

商务客服 研发客服

研发客服