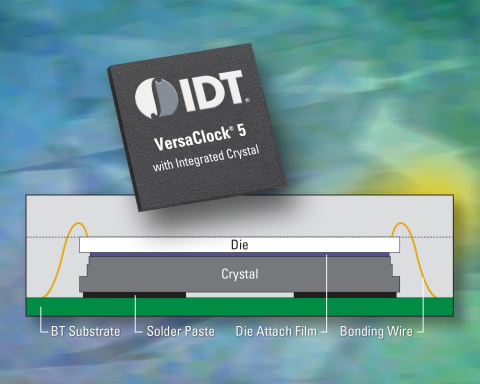

S加利福尼亚州圣何塞 - (BUSINESS WIRE) - 集成设备技术公司(IDT®)(NASDAQ:IDTI)今天推出其VersaClock®5个可编程时钟发生器的新版本,具有内置晶体更简单,更具成本效益的方法,以电子系统定时。该5P49V5933和5P49V5935提供的IDT的VersaClock 5个时钟发生器的创新功能,同时通过降低晶体的集成板空间和成本。通过内置的频率源,设计师不再需要将外部晶振在他们的设计,并不遗余力参与频率调谐的努力。

VersaClock 5可编程时序器件具有优异的抖动性能,在竞争器件一半的电力,并提供通用的输出对,可独立配置为LVDS,LVPECL,HCSL或LVCMOS双。多路输出计时解决方案整合系统组件具有超强的设计灵活性,使得它非常适合成本敏感,低功耗的消费类以及低抖动通信应用。晶体的积分有效地把设备到可编程晶体振荡器加利福尼亚州圣何塞 - (BUSINESS WIRE) - 集成设备技术公司(IDT®)(NASDAQ:IDTI)今天推出其VersaClock®5个可编程时钟发生器的新版本,具有内置晶体更简单,更具成本效益的方法,以电子系统定时。该5P49V5933和5P49V5935提供的IDT的VersaClock 5个时钟发生器的创新功能,同时通过降低晶体的集成板空间和成本。通过内置的频率源,设计师不再需要将外部晶振在他们的设计,并不遗余力参与频率调谐的努力。

VersaClock 5可编程时序器件具有优异的抖动性能,在竞争器件一半的电力,并提供通用的输出对,可独立配置为LVDS,LVPECL,HCSL或LVCMOS双。多路输出计时解决方案整合系统组件具有超强的设计灵活性,使得它非常适合成本敏感,低功耗的消费类以及低抖动通信应用。晶体的积分有效地把设备到可编程晶体振荡器,并且从设计的除去甚至更多的组件。

“通过集成晶体到我们最新的VersaClock 5的设备,我们已经开发了许多客户的利益了独特和创新的时机产品,”克里斯劳施,IDT的多市场时机部总经理说。 “设计团队获得原始VersaClock的所有优点5,出色的抖动和动力性能,再加上时间和成本的节约不处理的晶体。”

该5P49V5933最多可以生成两个输出频率,而5P49V5935产生多达四个。这些器件在紧凑4×4毫米的封装。令人印象深刻的700 FSEC RMS相位抖动性能使客户能够满足1G / 10G以太网和PCI Express第二代1,2,3的要求,以及其他高性能互连,并满足SoC和FPGA的时钟产生要求。该器件具有仅为30 mA的低核心电流消耗。,并且从设计的除去甚至更多的组件。

“通过集成晶体到我们最新的VersaClock 5的设备,我们已经开发了许多客户的利益了独特和创新的时机产品,”克里斯劳施,IDT的多市场时机部总经理说。 “设计团队获得原始VersaClock的所有优点5,出色的抖动和动力性能,再加上时间和成本的节约不处理的晶体。”

该5P49V5933最多可以生成两个输出频率,而5P49V5935产生多达四个。这些器件在紧凑4×4毫米的封装。令人印象深刻的700 FSEC RMS相位抖动性能使客户能够满足1G / 10G以太网和PCI Express第二代1,2,3的要求,以及其他高性能互连,并满足SoC和FPGA的时钟产生要求。该器件具有仅为30 mA的低核心电流消耗。