【芯片设计】异步电路碎碎念(四) 异步逻辑的处理方法

而后一个顺理成章的事情就是练习写写代码啦。再次汇总下之前提到的异步逻辑同步器结构:

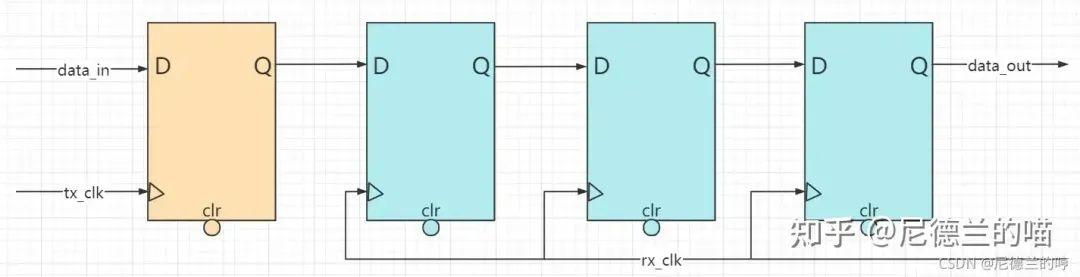

1.单比特电平打拍同步器;

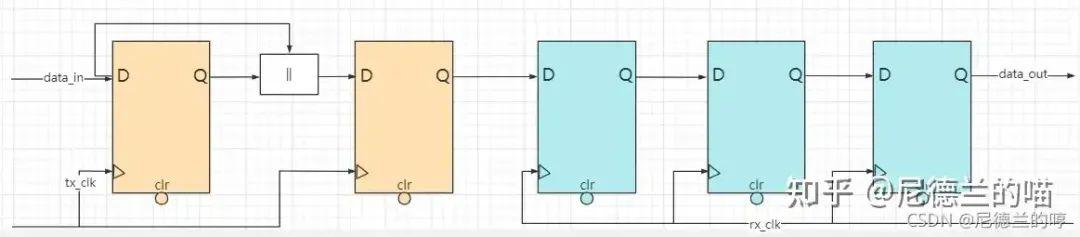

2.单比特脉冲打拍同步器;

3.多比特数据打拍同步器;

4.多比特电平使能DMUX同步器;

5.多比特脉冲使能握手同步器;

6.异步FIFO;

其中异步FIFO已经在前面的专栏中详细的写过代码了,因此就不在这里重复。这部分涉及到的代码位于:

【芯片设计】FIFO漫谈(七)异步FIFO从格雷码说起

单比特电平打拍同步器

单比特打拍同步器的代码很简单,不过其中有两点需要注意:

1.可配置性,主要包括打拍级数和在源时钟域是否需要打拍后输出;

2.专用同步打拍寄存器,实际交付的工程中同步器中的打拍寄存器可能会例化专用的模块,这是避免被工具优化或者做multi-bit,以及在设置sdc/cdc时方便统一匹配。

不过因为我们只是手撕代码练习,就不考虑专用打拍寄存器的事了。那么基于上述,手撕代码如下:

module async_1bit_delay #(

parameter DL = 2,

parameter FF = 1

)( /*AUTOARG*/

// Inputs

i_clk, i_rst_n, i_data, o_clk, o_rst_n, o_data

);

// ----------------------------------------------------------------

// Interface declare

// ----------------------------------------------------------------

input i_clk;

input i_rst_n;

input i_data;

input o_clk;

input o_rst_n;

output o_data;

// ----------------------------------------------------------------

// i_clk pipe

// ----------------------------------------------------------------

wire i_data_in;

generate

if(FF == 0)begin: NO_IN_DFF

assign i_data_in = i_data;

end //if(FF == 0)begin: NO_IN_DFF

else begin: IN_DFF

reg i_data_ff;

always @(posedge i_clk or negedge i_rst_n) begin

if(!i_rst_n)

i_data_ff <= 1'b0; else i_data_ff <= i_data; end assign i_data_in = i_data_ff; end //else begin: IN_DFF

endgenerate

// ----------------------------------------------------------------

// o_clk pipe

// ----------------------------------------------------------------

reg [DL -1:0]o_data_ff;

integer i;

always @(posedge o_clk or negedge o_rst_n) begin

if(!o_rst_n) begin

o_data_ff <= {DL{1'b0}}; end else begin o_data_ff[0] <= i_data_in; for(i=1; i

代码比较简单所以就不仿真了,反正后面还会反复调用这个模块的。

单比特脉冲打拍同步器

单比特脉冲打拍,核心的功能点就是脉冲展宽,一般需要覆盖接收域两拍时钟(或者三沿原则)。

所以就把时钟展宽的代码写一写好啦,下面是一种相对比较简单的脉冲拓展方式:

module async_pulse_widen #(

parameter TIMES = 2

)( /*AUTOARG*/

// Outputs

o_data,

// Inputs

clk, rst_n, i_data

);

// ----------------------------------------------------------------

// Interface declare

// ----------------------------------------------------------------

input clk;

input rst_n;

input i_data;

output o_data;

// ----------------------------------------------------------------

// Wire declare

// ----------------------------------------------------------------

localparam TIMES_W = 8;

// ----------------------------------------------------------------

// AUTO declare

// ----------------------------------------------------------------

/*AUTOOUTPUT*/

/*AUTOINPUT*/

/*AUTOWIRE*/

reg [TIMES_W -1:0]widen_cnt;

wire [TIMES_W -1:0]widen_cnt_d;

wire widen_cnt_en;

assign widen_cnt_en = (i_data && widen_cnt == {TIMES_W{1'b0}}) ||

(widen_cnt == TIMES) ||

(widen_cnt != {TIMES_W{1'b0}}) ;

assign widen_cnt_d = (i_data && widen_cnt == {TIMES_W{1'b0}}) ? widen_cnt + 1'b1 :

(widen_cnt == TIMES) ? 1'b0 :

widen_cnt + 1'b1;

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

widen_cnt <= {TIMES_W{1'b0}}; end else if(widen_cnt_en) begin widen_cnt <= widen_cnt_d; end end assign o_data = (widen_cnt != {TIMES_W{1'b0}}); endmodule // Local Variables: // verilog-auto-inst-param-value:t // verilog-library-directories:(".") // verilog-library-extensions:(".v") // End:

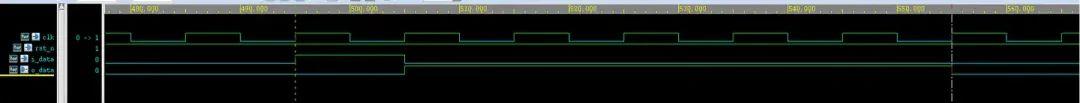

这里面的TIMES就是要展宽的倍数,这个代码的展宽结果输出是在脉冲使能的下一拍开始的,如展宽5倍:

同时如果在展宽过程中有下一个脉冲到达,那么是不响应的:

多比特数据打拍同步器

如果多比特数据没有使能信号,也就是说不关心正确数值同步过去的时间,只要同步过去就行,或者格雷码跨异步这种场景,那么可以选择多比特数据打拍同步器。多比特数据打拍同步器只需要例化若干单比特打拍同步器就可以了:

module async_nbit_delay #(

parameter DL = 2,

parameter WD = 1,

parameter FF = 1

)( /*AUTOARG*/

// Outputs

o_data,

// Inputs

i_clk, i_rst_n, i_data, o_clk, o_rst_n

);

// ----------------------------------------------------------------

// Interface declare

// ----------------------------------------------------------------

input i_clk;

input i_rst_n;

input [WD -1:0]i_data;

input o_clk;

input o_rst_n;

output[WD -1:0]o_data;

genvar i;

generate

for(i=0; i