摩尔定律由英特尔创始人之一戈登·摩尔在1965年提出,是指集成电路上可以容纳的晶体管数目在大约每经过18个月到24个月便会增加一倍。长期以来,“摩尔定律”一直引领着集成电路制程技术的发展与进步, 自1987年的1um制程至2015年的14nm制程,集成电路制程迭代一直符合“摩尔定律” 的规律。

本文引用地址:但2015年以后,集成电路制程的发展进入了瓶颈,7nm、5nm、3nm制程的量产进度均落后于预期。随着台积电宣布2nm制程工艺实现突破,集成电路制程工艺已接近物理尺寸的极限,摩尔定律明显放缓,行业进入了“后摩尔时代”。

2005年ITRS(International Technology Roadmap for Semiconductors)首次提出“More Moore”和“More than Moore”两种方向。

其中More Moore延续之前的整体思路,在器件结构、沟道材料、连接导线、高介质金属栅、架构系统、制造工艺等方面进行创新研发,继续沿着摩尔定律缩小数字集成电路的特征尺寸。

但是,随着工艺制程进入10nm以下,设计成本快速提高,数据显示16nm工艺的设计成本为1.06亿美元,到5nm增至5.42亿美元。侧重技术的More than Moore路径越来越被重视。

不断加高的“硅围栏”

在当前的国际地缘及行业发展环境下,企业研发尖端以及高性能服务器等设备的空间正变得日益逼仄。美国正在不断加高“硅围栏(Silicon Fence)”,想要通过芯片制造的管控手段实现对半导体发展进行遏制的目标:

8月12日,美国商务部BIS更新出口管制规则,限制3nm以下芯片设计EDA软件出口;10月7日,美国商务部BIS发布“史上最严出口管制”新规,近乎全面限制对华的先进芯片技术、设备和设计内核等。

12月14日,ARM确认对华禁售其最新的Neoverse V系列架构。这将会导致阿里等云计算企业后续芯片设计难以同步迭代,进而影响国内云计算、需要高精算力的超算以及人工智能等产业的发展。

在这样的环境背景下,一些芯片公司开始寻求采用日益复杂的开源芯片RISC-V,以取代ARM的设计。但国内业界还有待进一步采取有效对策,以实现技术及产业等发展突围。

什么是先进技术?

集成电路产业链包括集成电路设计、集成电路晶圆制造、芯片和测试、设备和材料行业。芯片封装测试环节是指芯片制造工艺完成后的封装测试环节,传统封装方式包括DIP、SOP、QFP等。

先进封装是相较于传统封装而言。随着电子产品进一步朝向小型化与多功能的发展,芯片尺寸越来越小、种类越来越多等,使得三维立体(3D)封装、扇形封装(FOWLP/PLP)、微间距焊线技术,以及系统封装(SiP)等先进封装技术成为延续摩尔定律的最佳选择之一。

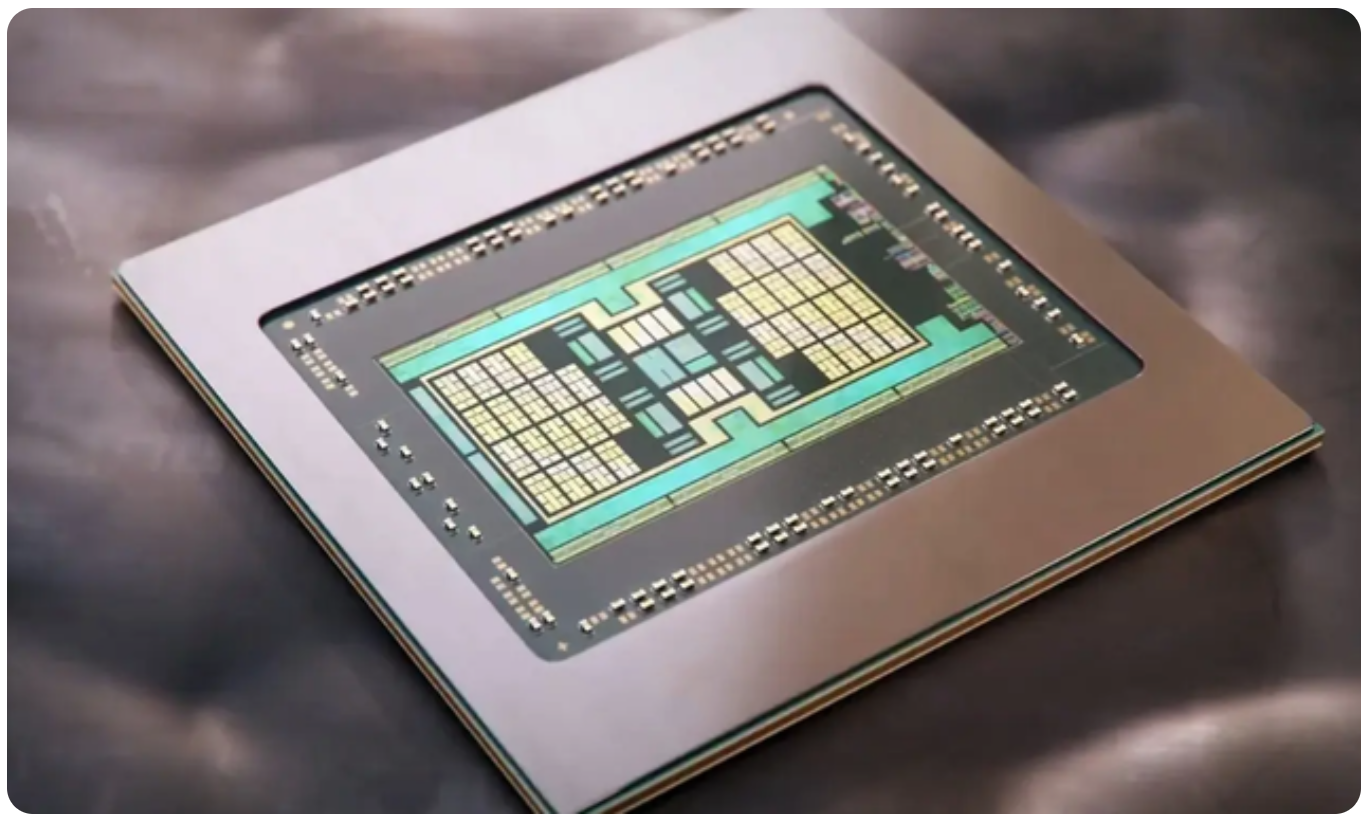

苹果的M1 ultra芯片采用台积电的CoWoS-S封装技术,将两颗M1 Max晶粒从内部进行互连,从而提升了芯片的性能水平;华为的芯片叠加专利也是如此,是将两颗14nm芯片合并成一颗芯片,从而拥有与7nm不相上下的性能水平。

先进制程工艺走到物理极限之后,未来芯片性能对于设计与封装的依赖就会变得越来越大。研究机构Yole的数据显示,2021年先进封装市场规模已经达到了约350亿美元,到2025年这一数字将上升至420亿美元。

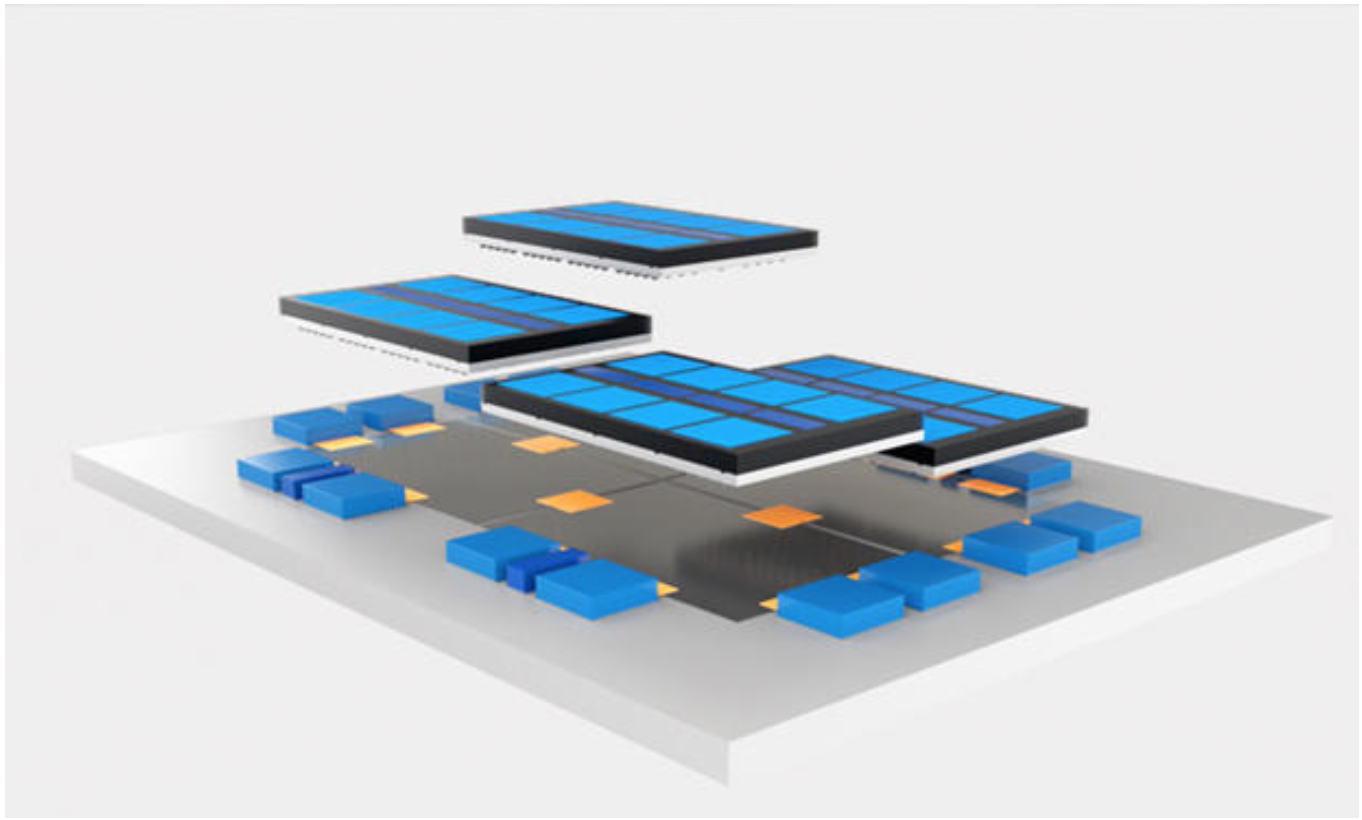

而Chiplet就是对传统SiP技术的继承与发展,属于先进封装的一种。其可将多种芯片(如I/O、存储器和IP核)在一个封装内组装起来,这样可以通过对不同功能模块的芯片选用合适的制程工艺,从技术方面实现各功能的最优化、成本的最小化、性价比的最大化、模块复用的灵活化。

简单来说,Chiplet技术是对原本复杂的SoC芯片的解构,将满足特定功能的裸片通过die-to-die内部互连技术与底层基础芯片封装组合在一起,类似于搭建乐高积木一般,最后集成为一个系统级芯片。

Marvell创始人周秀文在ISSCC 2015上就提出了类似的芯片架构概念 —— Mochi(模块化芯片);2018年,AMD公司率先将Chiplet应用于商业产品当中,其推出的“霄龙”型号处理器中就采用了小芯片架构设计,是当时功能集成度最高的芯片。

在数字经济趋势下,各种超大算力芯片将有望率先采用基于Chiplet的设计实现思路和工程实践方法。高性能服务器/数据中心、自动驾驶、笔记本/台式电脑、高端智能手机等将在未来几年成为Chiplet的主要应用场景,引领该市场增长。

可以从先进封装技术实现突破

2021年中国本土芯片产值占本土市场需求的比例仅16.7%,总部在中国的企业占比仅 6.6%。

在集成电路设计和制造环节,我国和世界顶尖水平差距较大,特别是在制造领域最为薄弱,而封测环节则为我国集成电路三大领域最为强势的环节。根据ittbank数据,2021年全球营收前十大封测厂商排名中,有三家企业位于中国大陆,分别为长电科技、通富微电和华天科技,分别排名第三、第五和第六。

长电科技去年提出从“封测”到“芯片成品制造”的概念升级,长电CEO郑力提到:“封测”这个词已经不能很好地表达先进封装的含义,以及高密度封装的技术需求和技术实际状态。所以以“成品制造”去描述更为贴切,可以反映当下的集成电路最后一道制造流程中的技术含量和技术内涵。

封装工艺对于“中国芯”的发展是具有积极意义的。在顶尖的封装工艺加持下,通过多芯片的重组堆叠,我们也能实现和高端芯片同样的性能水平。而这也将降低中国芯对光刻机的依赖,也算是“去美化“进程中的重要一步。

尽管Chiplet目前还不能替代以光刻机的演进为主要方向的传统集成电路的技术路线,但在一些特定的场景下,Chiplet设计方式结合成熟制程工艺,已经可以“小于等于”先进制程工艺。对于像数据中心等一些对芯片功耗和面积的要求并不高的场景,Chiplet是可以用来解决一些先进工艺不足的难题的。

此外,国内半导体创业企业中做CPU、GPU等“大芯片”的企业越来越多,随着功能集成要求更多,性能要求更高,设计面临的挑战也越来越大,Chiplet则可以实现不同功能模块的区隔,根据各自的最优迭代节奏分阶段演进,有效降低研发难度。

此外,先进的封装技术除了可以提升芯片的性能以外,还可以助力先进工艺的研发。台积电能做到今天领先全球的顶尖水平,也得益于其早期在封装业务领域的经验积累,通过封装业务外包,逐渐了解芯片构造,进一步研发技术,积累经验、培养人才,之后再进入芯片制造的领域。

中国首个原生Chiplet技术标准发布

12月16日,在“第二届中国互联技术与产业大会”上,首个由中国集成电路领域相关企业和专家共同主导制定的《小芯片接口总线技术要求》团体标准正式通过工信部中国电子工业标准化技术协会的审定并对外发布。

这是中国首个原生集成电路Chiplet技术标准,对中国集成电路产业延续“摩尔定律”,突破先进制程工艺限制,探索先进封装工艺技术具有重要意义。

其实在此之前中国就在着手准备小芯片的标准制定了,2021年5月,由中科院计算所、工信部电子四院以及国内多个芯片厂商,在工信部对《小芯片接口总线技术要求》正式立项。

如今这项标准终于发布,有助于行业的规范化、标准化发展,为赋能集成电路产业打破先进制程限制因素,提升中国集成电路产业综合竞争力,加速产业进程发展提供指导和支持。或许后续的目标就是完善生态建设,在标准的基础上定下长远的发展目标。

而在今年3月,在苹果公司发布M1 Ultra的前一周,英特尔、AMD、Arm、台积电、三星、日月光、高通、微软、谷歌云、Meta等十家巨头联合发起了一项Chiplet的新互联标准UCle。这几位成员中有全球顶级的芯片制造商,有全球最大的芯片封测商,也有领先的芯片设计企业。这次半导体产业链的集结,也被行业看做Chiplet标准推广普及的新起点。

除了各大巨头的追捧外,Chiplet能够互连的标准和统一的接口同样是生态和市场变强变大的重要因素。虽然Chiplet正展现出诸多好处和市场潜力,但是要充分发挥其效力,仍面临着一些需要解决的难题和挑战。

首先,解决互联标准只是第一步,未来随着Chiplet技术的发展终究会使小芯片间的互联达到更高的密度,要应对先进封装功能和密度的不断提升,散热、应力和信号传输等都是重大的考验。

其次,对于芯片设计来说,虽然依托Chiplet无需再去设计复杂的大芯片,但是将SoC分解Chiplet化,并将其整合到一个2.5D/3D封装当中,会带来系统复杂度的大幅提升,在系统设计方面存在较大挑战。

最后,在芯片测试层面,将一颗大的SoC芯片拆分成多个芯粒,相较于测试完整芯片难度更大,尤其是当测试某些并不具备独立功能的Chiplet时,测试程序更为复杂。

除了芯片设计、验证、封装与测试以外,Chiplet技术需要EDA工具从架构探索、芯片设计、物理及封装实现等提供全面支持,以在各个流程提供智能、优化的辅助,避免人为引入问题和错误。支持Chiplet芯片设计的EDA工具链以及生态是否完善,是否可持续发展,也是Chiplet技术成功所需要解决的关键问题。

相关文章

技术咨询

技术咨询 代买器件

代买器件 商务客服

商务客服 研发客服

研发客服