实验目的

实验任务

本实验的任务是描述一个电路,并通过STEP 开发板的12MHz晶振作为触发器时钟信号clk,拨码开关的状态作为触发器输入信号S,R,触发器的输出信号Q和非Q,用来分别驱动开发板上的LED,在clk上升沿的驱动下,当拨码开关状态变化时LED状态发生相应变化。

本文引用地址:实验原理

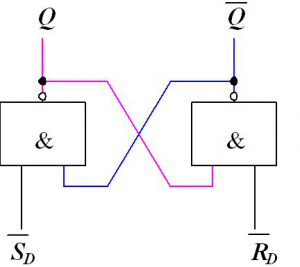

基本RS触发器可以由两个与非门按正反馈方式闭合构成。通常将Q端的状态定义为锁存器的状态,即Q=1时,称为锁存器处于1的状态;Q=0时,称锁存器处于0的状态,电路具有两个稳态。电路要改变状态必须加入触发信号,因是与非门构成的基本RS触发器,所以,触发信号是低电平有效。非Rd和非Sd是一次信号,只能一个个加,即它们不能同时为低电平,因为会有逻辑矛盾(Q == 非Q)。

建模描述

用数据流描述实现的RS触发器

程序清单rsff.v

<code verilog> module rsff

(

input wire clk,r,s, //rs触发器输入信号

output reg q, //输出端口q,在always块里赋值,定义为reg型

output wire qb //输出端口非q

);

assign qb = ~q;

always@(posedge clk)

begin

case({r,s})

2'b00: q <= q; //r,s同时为低电平,触发器保持状态不变

2'b01: q <= 1'b1; //触发器置1状态

2'b10: q <= 1'b0; //触发器置0状态

2'b11: q <= 1'bx; //r,s同时为高电平有效,逻辑矛盾,触发器为不定态

endcase

end

endmodule

</code>

仿真文件rsfftb.v

`timescale 1ns/100ps //仿真时间单位/时间精度 module rs_ff_tb(); reg clk,r,s; //需要产生的激励信号定义 wire q,qb; //需要观察的输出信号定义 //初始化过程块 initial begin clk = 0; r = 0; s = 0; #50 r = 0; s = 1; #50 r = 1; s = 0; #50 r = 1; s = 1; #50 r = 0; s = 1; end always #10 clk = ~clk; //产生输入clk,频率50MHz //module调用例化格式 rs_ff u1 ( //rs_ff表示所要例化的module名称,u1是我们定义的例化名称 .clk(clk), //输入输出信号连接。 .r(r), .s(s), .q(q), //输出信号连接 .qb(qb) ); endmodule

实验步骤

仿真结果和实验现象

文章来源于:电子产品世界 原文链接

本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关文章

实验12:边沿触发的D触发器(2023-10-10)

沿的驱动下,当拨码开关状态变化时LED状态发生相应变化。本文引用地址:

实验原理

从D触发器的特性我们知道,它的状态仅仅取决于时钟信号达到之前瞬间的D信号。为了防止SR锁存器的S、R被同时置1的情况,常采......

实验11:RS触发器(2023-10-10)

码开关状态变化时LED状态发生相应变化。本文引用地址:

实验原理

基本RS触发器可以由两个与非门按正反馈方式闭合构成。通常将Q端的状态定义为锁存器的状态,即Q=1时,称为锁存器处于1的状态;Q=0时,称锁存器处于0......

实验15:环形计数器(2023-10-11)

。

实验原理

将移位寄存器的输出q0连接到触发器q3的输入,并且在这4个触发器中只有一个输出为1,另外3个为0,这样就构成了一个。初始化复位时,给q0一个置位信号,则唯一的1将在环形计数器中循环移位,每4......

实验13:JK触发器(2023-10-11)

实验13:JK触发器;实验目的

(1)熟悉和掌握开发流程和软件使用方法;

(2)通过实验理解和掌握原理;

(3)学习用语言行为机描述方法描述电路。

实验任务

本实验......

实验16:扭环形计数器(2023-10-12)

实验16:扭环形计数器;实验目的本文引用地址:(1)熟悉和掌握开发流程和软件使用方法;

(2)通过实验理解和掌握原理;

(3)学习用行为级描述时序逻辑电路。

实验任务

设计一个右移。

实验原理

将移......

使用三相全控桥式整流的电路可以对直流电机进行调速控制吗(2023-08-21)

使用三相全控桥式整流的电路可以对直流电机进行调速控制吗; 三相桥式全控整流及直流电机调速实验原理

三相桥式全控整流电路可以使用触发器来控制整流器的导通,从而达到改变电流方向和大小的目的。在实验......

实验22 4位串行累加器(2023-10-16)

框图如图所示,在开关K处设置串行输入数据,在CP端输入8个脉冲,将完成一次,两个四位串行数据的相加,结果存D-A中。本文引用地址:

实验原理

根据上述电路框图,可以分割系统任务。

累加......

基于51单片机的直流电机调速实验(2024-08-29)

和之前LED呼吸灯(定时器实现),实验原理本质上是相同的,可以结合之前的文章进行理解学习,这里就不再赘述了。(下图引用LED呼吸灯实验)

二、关键代码

void Timer0_Routine......

实验14:移位寄存器(2023-10-11)

移并行输入、串行输出的。本文引用地址:

实验原理

如果将多个触发器级联就构成一个多位的,如下图所示,是以4位移位寄存器为例的逻辑电路图,其中的LD/SHIFT是一个置数/移位控制信号。当LD/SHIFT为1......

可创建小型组合与时序逻辑电路的PLU可编程逻辑单元(2023-03-14)

-config-tool

3.1 原理图配置

打开PLU配置工具,选择原理图设计,做一个简单的或运算与D触发器实验,如下:

点击菜单栏File-》Export-》PLU source file将其导出为C......

技术咨询

技术咨询 代买器件

代买器件 商务客服

商务客服 研发客服

研发客服