实验目的

实验任务

本实验的任务是设计一个7位右移并行输入、串行输出的。

本文引用地址:实验原理

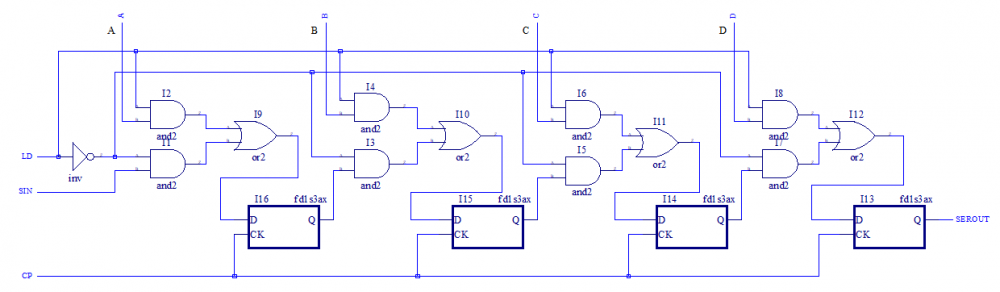

如果将多个触发器级联就构成一个多位的,如下图所示,是以4位移位寄存器为例的逻辑电路图,其中的LD/SHIFT是一个置数/移位控制信号。当LD/SHIFT为1时,在CP作用下,从输入端A、B、C、D并行接收数据;当LD/SHIFT为0时,在CP作用下,将寄存器中的数据顺序移出,空位由输入端SIN补充。这种寄存器常用来进行并行数据到串行数据的转换。

建模描述

7位移位寄存器程序清单 shift7.v

module shift7(input wire clk, //输入时钟input wire rst, //复位信号input wire [6:0] datain, //并行输入数据output wire dataout //串行输出数据); reg [6:0] data; always @(posedge clk) if(!rst) data <= datain; //同步复位,复位时并行数据存入变量data else begin data[6] <= 1'b0; //最高为补0 data[5] <= data[6]; data[4] <= data[5]; data[3] <= data[4]; data[2] <= data[3]; data[1] <= data[2]; data[0] <= data[1]; //右移一位 end assign dataout = data[0]; //串行输出 endmodule

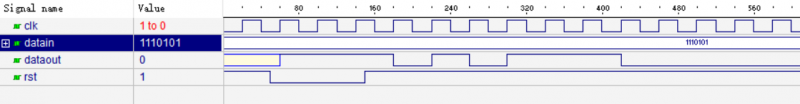

仿真文件shift_tb.v

`timescale 1ns/100ps //仿真时间单位/时间精度module shift7_tb; reg clk, rst; //需要产生的激励信号定义reg [6:0]datain; wire dataout; //需要观察的输出信号定义initial begin clk =0; rst =1; datain =7'b1110101; //所需移位数据 #50 rst =0; #100 rst =1; endalways #20 clk =~clk; //产生时钟信号 频率25MHz//module调用例化格式shift7 u1 ( .clk (clk), .rst (rst), .datain (datain), .dataout(dataout) );endmodule