JEDEC关于 BGA的设计指南中没有定义特定的材料和组装 方法。针对不同的应用,各供应商会使用不同 的基材。基底结构最可能是增强型有机层压 板,或为非增强型聚酰亚胺膜或陶瓷。以陶瓷为基材的BGA封装通常由熔点为302°C的高温焊 料(90%铅,10%锡)制成的非塌陷焊球组成。焊球尺寸随着焊球节距和封装大小而变化。较 大的封装通常会需要较大的焊球尺寸以提高其 可靠性。由于陶瓷封装相对比较平整且焊球直 径的公差非常小,共面度要求也相对严格。陶 瓷材质封装的供应商通常会对板级组装选择适用的焊膏成分提供建议。

为了研发新的连接方法,在上世纪90年代,一 项使用聚合物涂层焊球作为互连介质的专利得以完成。金属球是导电的,可用铜、银、金、 焊料等制成并在之后镀上一层导电聚合物。涂 覆方法取决于焊球制造商,且按应用所需涂层可能有不同厚度。开发这种新式的互连方法是 为了解决由于陶瓷中介基板和有机印制板之间 CTE(热膨胀系数)不同而引发的问题。已发 表有一些技术论文讨论关于界面发热以及导电 聚合物如何连接中介基板和印制板的连接盘。

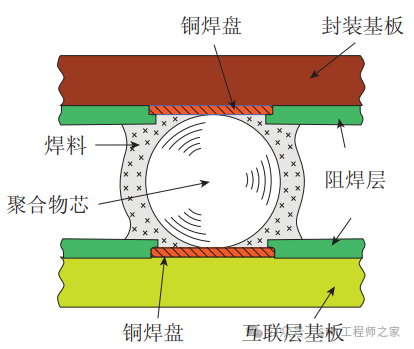

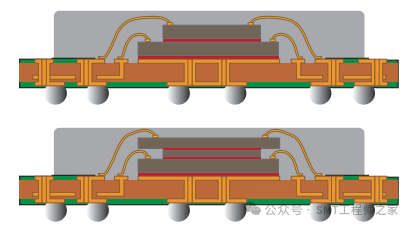

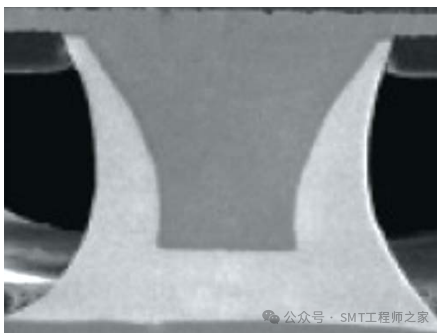

对安装在FR-4板上的陶瓷封装的传统焊球和聚合物芯焊球两者进行温度循环试验,并获得数 据,同时也进行了电气模拟以比较聚合物芯焊球和传统焊球。图4-6展示了这一工艺的概念。

层压板基BGA和聚酰亚胺膜基BGA是完全不相 同。层压板基的封装基本上是由高等级Tg的电 路板材料制成。BGA封装应用中被一些公司采 用的高等级 Tg 树脂系统是双马来酰亚胺三嗪 (BT)。增强聚酰亚胺以及聚酰亚胺膜有更高的 温度额定值并在BGA和FBGA中也被广泛使用。

一、焊球合⾦

焊球成分由总体印制电路组 装工艺(如锡铅或无铅)以及封装类型(如陶 瓷或层压基板)决定。增强层压板和聚酰亚胺 膜基BGA封装上选择的焊球触点合金成分差异 会很大。许多配置的是具有183°C(或对于含银 2%的共晶焊料,179°C)熔点(液相线)的锡/ 铅共晶焊料。通常仅需使用助焊剂然后在温度 215°C-220°C下再流完成连接工艺以将焊球触点 施加到封装基板上。

1、锡/铅技术合⾦

尽管没有在大多数商 业应用中广泛使用,锡/铅合金可适用于焊球及 焊接材料。一种常见的合金组成为Sn63Pb37共 晶合金,液相线温度为183°C。共晶含银合金成 分Sn63Pn36Ag2,液相线温度为179°C,是共晶 Sn63Pb37的可接受的替代选择。当使用锡/铅技 术时,陶瓷BGA通常使用Sn10Pb90高铅合金, 以提供所需的焊点可靠性,这种合金在锡/铅再流焊工艺期间不会熔化。用共晶Sn63Pb37与印 制电路板相连时可提供可靠的互连。

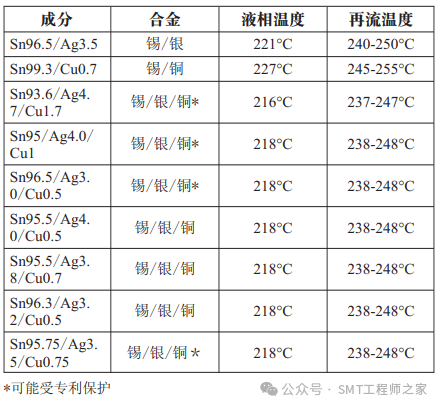

2、⽆铅技术合⾦

符合RoHS指令(关于在 电子电器设备中限制使用某些有害物质),对于 焊球触点和封装连接基板,电气及电子组件和电 子元器件的生产厂商必须使用无铅材料。尽管有 许多无铅合金可供使用,大多数制造商使用了将 锡作为主要成分的锡银合金或锡银铜合金。典 型的无铅合金的成分组成包括Sn96.5Ag3.0Cu0.5 (SAC305),Sn95.5Ag3.8Cu0.7(SAC387)和Sn95.5 Ag4.0Cu0.5(SAC405)。这些焊料的液相线温度在 217-227°C的范围之内,需要的再流峰值温度范围为240-260°C(取决于要加工组件的总质量)。取决于具体合金规定的成分,焊球液相点的变 化范围可以达到10°C。(见下表)

在锡银铜系统中,也建议加入其它的合金元素;然而这些添加物会影响焊料过冷度、各种金属间 化合物的构成以及不常见晶格性质和微结构变 化。在使用新合金到BGA以及将新合金的BGA 用于组装时必须要特别注意。除了锡银铜系统, 含有铋、铟、锑或锌等元素的合金系统也已被研发出来。每个系统冶金基础不相同,从而决定了相应的物理性质和机械特性并影响了组装 工艺参数和焊点可靠性。

二、焊球连接⼯艺

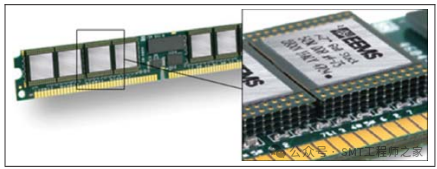

封装基板通常会被制成 包含多个封装的长条状(见下图)。

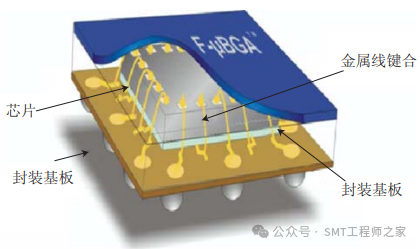

焊球置放 在金属线键合和塑封或压模工艺之后进行,对于批量BGA组装,会利用自动或者半自动置球 方式。所需尺寸的合金球体可以通 过成组的贴片机-采用自动化系统逐个放置, 或采用一个类似模板的夹具进行成批放置并连 接。对于研发用或者仅需小批量置球时,可以使用简单的模板夹具来对焊球精确定位,但是 所有焊球的连接工艺都是一样的。在开始阶段先将液态或者“粘性”焊膏助焊剂涂敷或印刷在触点图形上,再流焊期间助焊剂保持焊球定位。焊球再流焊接到基板上通常在氮气环境中进行。氮气环境可以保证焊球一致的质量同时 避免其表面在再流焊过程中被氧化。然而,封装与PCB再流焊连接时没有必要使用氮气。共晶焊球可以提供“可控塌陷”,从而在再流焊过程中提升自对准能力(弥补在组装过程中的一 些偏移)。

在使用塑封BGA时需要考虑一些问题。首先是湿敏问题。在返工过程中,要被拆除和替换的元器件周边的湿敏元器件必须事先进行烘烤和 /或避免它们在返工活动中受热。如果塑封BGA 需要重复使用,那么在封装从印制板组件上被取下之后需要特别小心进行BGA的重新植球。对于陶瓷基BGA所用的高熔点非塌陷焊球,湿敏问题并非如此;焊球在返工过程中也不会融 化。

当暴露于焊料连接所需的温度时,塑封BGA封装也容易翘曲。在再流焊焊接过程中,封装边 缘会上翘或者向下弯曲,进而严重地影响封装和印制板的电气连接界面。大封装比小封装更 容易翘曲。 封装翘曲是由基板结构、模封材料和内置硅芯片的热膨胀系数不匹配造成的。 当 芯片尺寸较大或BGA有散热片时,这种问题可能会更严峻。

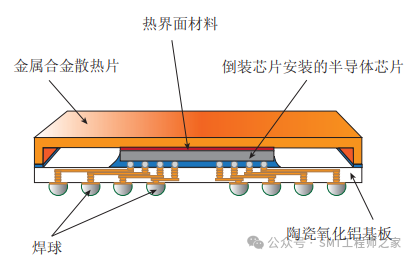

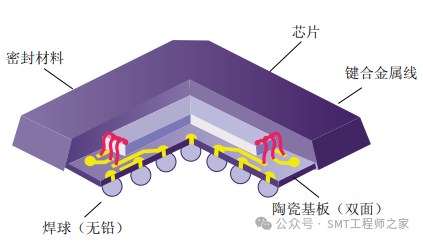

三、陶瓷BGA

陶瓷封装的内部连接方式可以是导线键合或芯片倒装。下图表示封装内部的倒装芯片键合。封装配置的芯片可安装在基板的上表面(腔体朝上)或基板的下表面(腔体朝下)。 下图1所示的典型陶瓷封装所用的焊球,是一种熔点为302°C的高温合金(90%铅和10%锡)。然而,焊球连接合金可以是共晶焊料(Sn63Pb37)

尽管聚合物灌封或包覆成型被广泛应用于芯片区域, 一些陶瓷基BGA封装的器件是密封的(不会吸收湿气)。 由于这些产品的焊球的熔点通常较高,所以在返工时不会塌陷。陶瓷BGA的缺点在于其高热容量,这与塑封集成电路有些许不 同,使得在开发再流焊温度曲线时的更困难。 由于陶瓷封装和电路板之间热膨胀系数的不匹 配,焊点需要进行物理加固。 在焊接和清洁工艺之后,通常会在陶瓷中介基板和有机印制电 路板之间加入环氧树脂基底部填充材料。

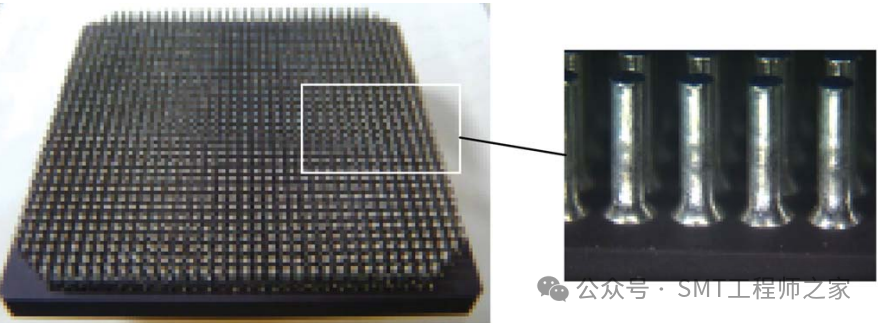

四、陶瓷柱栅阵列

下图所示为典型柱状焊料 触点,通常用于大型陶瓷封装(32mm至45mm)。这种封装与早期的针栅阵列类似但是触点节距较小且引线也更为脆弱(柱状)。柱状触点的直径大约为0.5mm,长度为1.25mm至2.0mm。柱状引脚可通过共晶焊料(Sn63Pb37)连接到封装或者用90%铅和10%锡的焊料铸造定位到封装。较长的柱状引脚通常能吸收陶瓷封装和印制板 之间大量热膨胀不匹配从而提高焊点可靠性。

另一方面,较长的柱子可能会减弱电气性能并 增加总体封装高度轮廓。焊料柱不如焊球触点 牢固,操作时容易损坏。

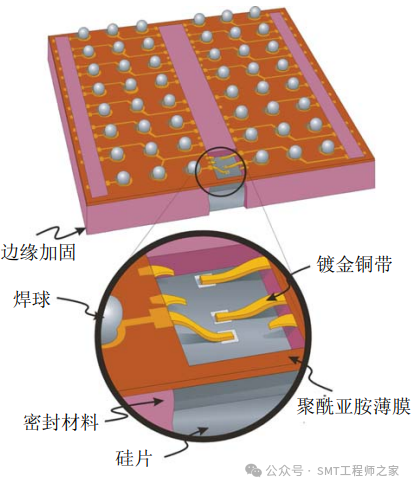

五、载带球栅阵列

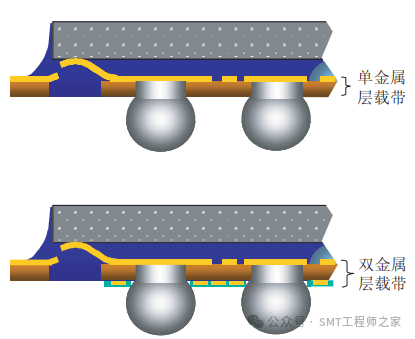

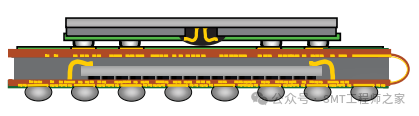

下图所示的载带(聚酰 亚胺膜)BGA可提供总体外形更低的封装。低电介质聚酰亚胺膜可提供一层或两层金属层以 便封装内电路的高密度布线。

对于下图1所示典型的聚酰亚胺中介基板BGA,热膨胀系数的不匹配并不是个问题,因为芯片连接粘 合剂和基板伸缩性会吸收封装结构中的应力。载带BGA可用于倒装芯片、金属线键合或者引线 键合以实现芯片与基板的互连。单金属层载带 基板通常用于低成本和低引线数封装应用,双金属层载带用于高引线数或性能驱动的应用。

例如,附加的铜层能提供有效的接地回路以显 著降低电感量和开关噪声效应。接地层效应会 影响噪音降低的程度,而接地层内电流阱的数 量也会影响电感量的水平。下图2中比较的双金 属层基板,不仅可提供较好的电气性能,也可以显著改善封装内部电路布线能力。

单金属层材料的电路布线限制在焊球连接位置 之间狭窄的介电间隙内。随着触点节距缩小至 0.5mm,触点外形之间的间距会减至75μm,可能只可布置单条线路。这个因素限制了单金属 层用于狭窄的低I/O数封装应用。

六、多芯⽚封装

对于高密度封装技术来说, 便携和无线电子产品代表了发展最为迅猛的领 域。在电路板制造和IC封装中,将最为复杂电 子功能压缩到一个更小、更轻的成品中的技术 仍在持续发展。

可携带和手持式是电子产品自然的目标。例如, 数码相机和便携式摄像机必须考虑易用性、较 轻的重量以及性能。手机、传呼机、个人通信 装置、掌上电脑、工业和汽车电子、个人全球 定位系统、医疗和诊断产品,都是可行的更高 效设备小型化的代表。

存储器件如Flash、SRAM、SDRAM是最早面市的商用产品类型以适应FBGA和CSP的大量需要。 然而, 数字信号处理器、控制器、CPU和任何专用集成电路器件也是多芯片封装的主要候选对象 。许多芯片封装适应简单的导线键合 工艺而将芯片互连到基板。然后灌封或包覆芯 片和导线键合区域以提供单封装外形。导线键 合解决方案能配置两个或更多芯片的叠加,但 是随着每一芯片层的增加,封装高度会显著增加。

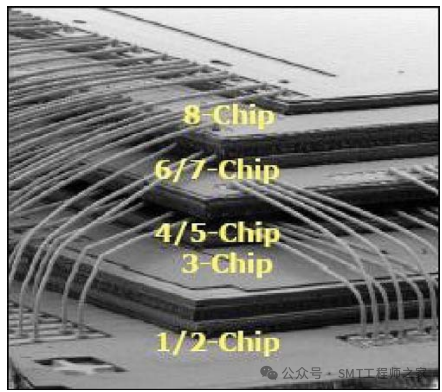

将两个或多个IC封装于单个封装外形,在尺寸 功能比方面更有效并且可能增强性能。多芯片封装可潜在地增加元器件密度并改善印制板上 元器件间的布线效率。某些多芯片封装方法是在单个基板上将一个芯片连接到另一个芯片的 上面,如下图所示。

以金字塔形叠加不同尺寸芯片是常见的,但是当芯片尺寸相同时,各有源芯片间要加入隔离片以消除键合线弧。

七、系统级封装(SiP)

厂商将大量相关功能单元合并至单个封装外形中以便为额外功能 提供空间。尽管一些厂商选择研发多功能芯片 (片上系统),但这个选择对于许多其它厂商来 说可能并不实际。由于开发带有混合功能能力 的定制芯片的时间跨度太长,大部分厂商发现 将已验证的芯片组合(叠加)在单个封装结构 内更为实际(见下图的芯片叠加示例)。

上图显示的八芯片配置包括两个1Gb的闪存芯片,两个256Mb的SDRAM,两个256Mb的闪存芯片,一个128Mb UtRAM以及一个64Mb UtRAM存储器的芯片。这是一个印象非常深 刻的芯片叠加应用。该公司作为大部分或所有 这种封装芯片的供应商,在封装成品上已取得 满意的良率。然而,由于制造工艺的变差以及 多种货源的芯片级别产品的潜在良率不同,对 某些器件来说,总封装级别的成本目标不是总 能达成的。为了保证未封装裸芯片的质量和可 靠性,在封装级组装前裸芯片必须通过一些电 性能测试挑选。ASIC、简单逻辑电路、某些处 理器以及线性电路在某一时间段趋于稳定,然 而测试是保证其质量和可靠性的唯一方法。比 如,将逻辑和存储器整合在单一封装上,会造 成非常实际的问题。这两种功能的测试有本质 上的不同,且将会进一步损害用户使用此产品时的信心。

八、3D折叠封装技术

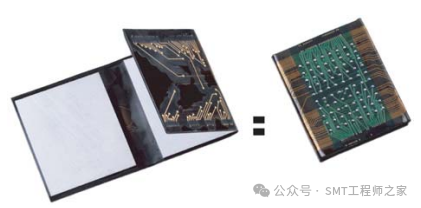

存储器芯片,如Flash或 SRAM,有比较高的生产良率。虽然在组装操作 或搬运中会发生损伤,但整体上存储器芯片的 封装工艺和测试有很高的合格率。挠性基板材 料可将几个芯片折叠并放置在单个FBGA封装外 形之内(此封装仅仅略大于芯片组中最大的一 个)。下图为常见的折叠挠性封装,将三个独立的存储器芯片合并在单封装外形中。

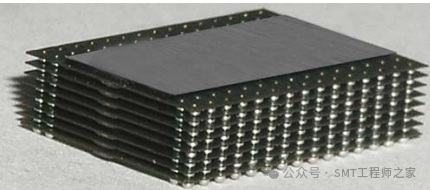

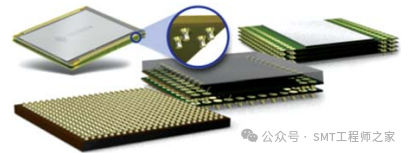

九、焊球堆叠,封装叠装

尽管不限于存储 器封装,一个主要的应用是DDR-SDRAM 芯片堆叠,它可使OEM和存储器模块制造商将存储器板密度增加至当前可用密度的八倍。将预先测试的FBGA封装芯片堆叠是存储器的一种理想应用。联接前对存储器的测试、挑选和分级可 保证最终器件配置提供其全部的潜在性能。下图展示了将几个焊球堆叠封装为一个整体组件 的案例。

顺序堆叠预测试过的FBGA封装使元器件密度和功能急剧增加。作为当前应用的一个实际例子, 要考虑在标准单面SO-DIMM(小外形双排直列 存储器模组)上动态和潜在的存储容量,如下图所示。

十、折叠和堆叠的封装组合

由于处理器和 ASIC晶圆制造良率不像存储器或低复杂度功能 的集成电路那样可预测,因此必须在封装组装 前对每一个芯片进行预测试。另外,将两种良率差距较大的产品置于同一成品封装中风险是非常大的。为了将风险最小化,顺序叠加多芯片封装的理念变得很有吸引力。

由于将几个功能组合在单个封装的最终目标仍是可行的,在最终整合之前对单独器件进行组 装和测试是比较理想的。与合成良率和测试相 关的问题可以较容易地通过堆叠单个封装来解 决。一个例子是在两段格式存储功能模块中各 自封装和测试ASIC,典型地如同下图所示。

带有存储器的底部和顶部封装组件会在折叠和合并操作之前进行处理和测试。通过折叠和表面 贴装连接处理,这两个预测试过的分区成为单 个、高良率的多功能元器件。除此之外通过在 ASIC封装顶部上提供通用阵列状接口,一些不 同的存储功能块可以直接焊接在底部封装上。

十一、叠装封装

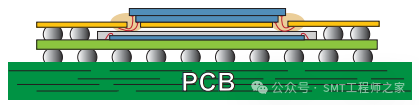

在单个封装外形内封装多个芯片单元的解决方案已有迅速发展。对于许多高密度存储应用来说,在单个半导体封装基板上将数个半导体芯片进行垂直叠加已证明是有效的。但是将一些较新的多功能处理器和控制器产品与一些较成熟的高良率存储单元混合时, 总的封装良率不是总能满足预期。经验证明一个更有效的解决方案是 叠加封装(PoP)方式 , 其设计是将已完全封装和经过预测试的分立逻辑和存储器件垂直组合在各自独立的阵列配置封装基板上,它们相互对齐并上下堆叠,典型地如下图所示。

封装叠加方式对于需要多功能、高性能和较小连接盘图形的各种应用证明是理想的:将经过预测试的封装分区做叠加给设计人员带来高度的灵活性,几乎允许任何组合的存储器与任何 逻辑芯片组相结合。将分立的逻辑器件和存储 封装以垂直布局的方式进行组合,不仅节省了在电路板上的空间,而且一般也会减少引线数 量,简化系统集成度并使性能得到加强。很多 产品包括如:无线耳机、数码相机、便携式游 戏机和GPS产品已经开始利用这种多芯片封装方案的优点。

十二、多芯⽚封装的优势

多芯片封装的主要 优势是元器件密度急剧增加。产品的尺寸和重 量可能会减小,但其功能却得到了增强。功能的增强是通过集成几个不同类型器件来实现的。其它的优点包括减小了电路板复杂性、通过更 高的可靠性改善了产品质量以及降低了产品进 入市场的风险。多渠道采购已验证的成熟的芯 片,可使上市时间和拥有成本最小化。研发多芯片产品的任务并不是没有障碍,一些关键问题为:

十三、极密节距阵列封装解决⽅案

已开发出可行的方案给单芯片和PoP封装应用提供更密节距和更高接触密度。相比更传统的焊球或凸点接触,这种独特的中介基板制造工艺配置了实 心铜接触点的阵列。

用以描述这种独特触点外形命名为 “μPILRTM ” , 它可提供非常小的接触点特征和0.40那样的较密 节距变化,典型例子如下图所示。

当μPILR触点外形与更常见的焊球连接相比,其触点几何形状在直径和高度两方面明显偏小, 使得其有更低的成品封装外形。下图所示的实铜芯触点形状略呈锥形并且涂覆了与共晶或无铅焊接工艺兼容的镍/浸金合金(ENIG)。

μPILR封装器件的电路板组装采用最常见的表面贴装工艺,从焊膏印刷开始,经过贴片和再流 焊接。成功用于印刷的模板为100μm厚的不锈钢薄板,上有激光切除的270μm的方形开孔。由于模板开孔很小,这种应用的焊膏型号推荐使用5号尺寸的焊粉。节距为0.40mm的元器件的精确贴装也非常关键。当贴装超密节距阵列器件时, 机器的贴装精度必须满足±20μm的范围以保证所有连接点有合理均匀的焊料填充。