1 简介

1.1 LPC1752及AT24C08C简介

LPC1752是NXP推出的一款Cortex M3的芯片,最高运行频率可达80M

AT24C08C是Atmel的一款I2C串行EEPROM,代替原来的型号AT24C08B及AT24C08A。共有8K(1024*8 bit)、1024字节的存储单元。可进行1百万次的写操作,数据可保存100年。

1.2 连接方式

AT24C08C是通过LPC1752的I2C2连接的,连接图如下:

图1 LPC1752连接图

1.3 AT24C08C设备地址

The 8K EEPROM only uses the A2 device address bit with the next twobits (P1, P0) being for memory page addressing. The A2 bit must compare to itscorresponding hardwired input pin. The A1 and A0 pins are not connected.

根据连接图可得知AT24C08的地址为0xA0。

图2 AT24C08CDevice Address

1.4 I2C运行时钟频率

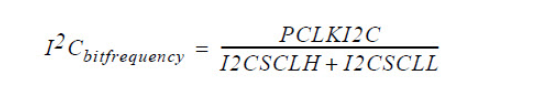

主机模式下必须通过对I2SCLH和I2SCLL寄存器进行设置来选择合适的总线速率和占空比。I2SCLH定义SCL高电平所保持的PCLK_I2C周期数,I2SCLL定义SCL低电平的PCLK_I2C周期数。位频率由下面的公式得出(PCLK_I2C是外围总线APB的频率):

选用的I2SCLL和I2SCLH值必须确保得出的总线速率在I2C总线速率的范围之内。I2SCLL和I2SLH的值都必须大于或等于4。表1给出了根据PCLK_I2C频率和I2SCLL和I2SCLH值计算出来的I2C总线速率的示例。

表1 I2C时钟速率的实例

2 函数介绍

2.1 初始化函数i2c2_init

按照LPC1752用户手册(UM10360)中第三章的介绍进行初始化,步骤如下:

a)。 电源:在寄存器PCONP中置位PCI2C2。

b)。 时钟:在寄存器PCLK_SEL1中选择PCLK_I2C2。

c)。 引脚: 通过寄存器PINSEL0使能I2C2引脚。通过寄存器PINMODE来配置I2C2引脚模式。

d)。 时钟频率:向I2SCLH和I2SCLH寄存器加载频率值来定义串行时钟频率(主机模式)。

e)。 中断:在NVIC中置位I2C2_IRQn寄存器使能I2C2中断。

f)。 向寄存器I2CONSET写入0x40来置位I2EN位。

2.2 中断函数I2C2_IRQHandler

通过读取I2STAT寄存器的值判断I2C总线上的状态,并进行下一步操作。

中断函数只处理了主机接收模式与主机发送模式。

1)I2C进入主机进入发送起始条件时,串行中断标志(SI)置位,状态寄存器(I2STAT)中的状态代码为0x08。此时将从机地址和数据方向位(SLA+W)装入I2DAT,同时复位I2CON的STA,STO和SI。

2.3 I2C总线进入开始状态i2c2_start

可通过置位STA位进入主机发送模式。一旦总线空闲,I2C逻辑会马上测试I2C总线并产生一个起始条件。

2.4 I2C停止函数i2c2_stop:

I2C结束时发送停止条件并释放总线。

a)向I2CONSET写入0x14来置位STO和AA位;

b)向I2CONCLR写入0x08来清除SI标志;

2.5主机发送函数i2c2_write

启动主机发送功能,向从机发送数据,通过建立缓冲区、指针和数据计数然后发启起始条件便可执行主发送操作。

a)初始化主机数据计数器;

b)建立数据将被发送到的从机地址,并且添加写位;

c)向I2CONSET写入0x20来置位STA位;

d)在主发送缓冲区内建立要发送的数据;

e)初始化主机数据计数器来匹配正在发送的信息长度;

f)退出。

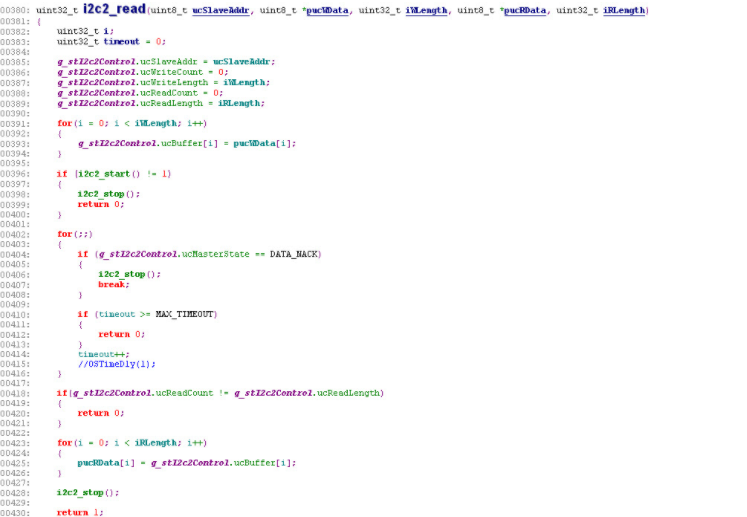

2.6主机接收函数 i2c2_read

启动主机接收功能,接收从机发出的数据。

通过建立缓冲区、指针和数据计数然后发启起始条件便可执行主接收操作。

a)初始化主机数据计数器;

b)建立数据将被发送到的从机地址,并且添加读位;

c)向I2CONSET写入0x20来置位STA位;

d)在主接收缓冲区内建立要发送的数据;

e)初始化主机数据计数器来匹配正在发送的信息长度;

f)退出。

3 测试

通过向0x00地址写入并回读固定数据验证有效性。

测试结果比较

第一次读取

第二次读取

经验证可以正常使用。