博通重磅产品发布,引领PCI-e交换机和重定时器市场

如果我们有两年甚至四年更长的时间暂停向机器添加更快的计算引擎,那么服务器设计的情况将会好得多。 这样,我们就可以让内存子系统和 I/O 子系统赶上并更好地利用这些计算引擎,并且还需要更少的内存组和 I/O 卡来满足这些计算引擎的需求。

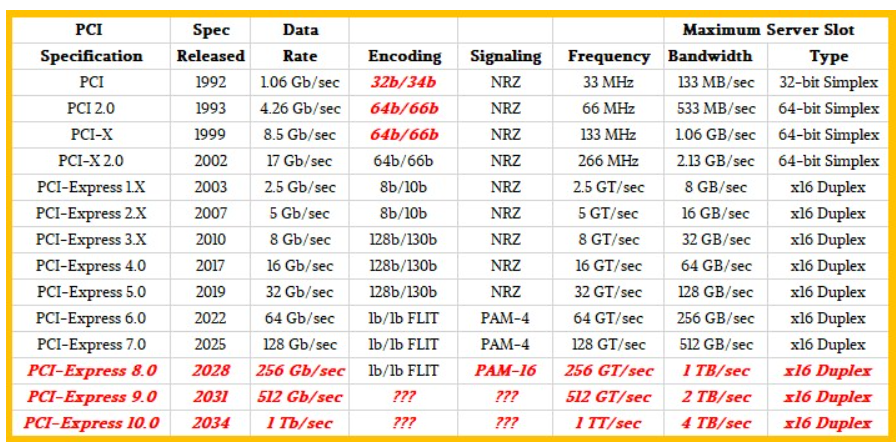

事实上,从 8 Gb/秒 PCI-Express 3.0(其规范于 2010 年发布)到 16 Gb/秒 PCI-Express 4.0 互连(本应在 2013 年发布)的转变延迟了四年,直到 2017 年才进入该领域。主要原因是计算引擎真正需要的 I/O 带宽与 PCI-Express 互连可以提供的带宽之间造成了阻抗不匹配。

这种不匹配一直延续下去,导致 PCI-Express 永远落后。 这反过来又迫使公司为其加速器提供自己的互连,而不是使用通用的 PCI-Express 互连,后者可以开放服务器设计并提供公平的 I/O 竞争环境。比如,Nvidia 创建了 NVLink 端口,以及 NVSwitch 交换机,再到NVLink Switch 结构,将 GPU 集群上的内存连接在一起,并最终将 GPU 连接到其“Grace”Arm 服务器 CPU。 AMD 也创建了 Infinity Fabric 互连来将 CPU 连接在一起,然后将 CPU 连接到 GPU,该互连标准也已在CPU内部用于连接小芯片(Chiplet)。

我们听说英特尔在十多年前的一些 Xeon 处理器上出现集成 PCI-Express 3.0 控制器问题后,在 PCI-Express 4.0 上犹豫不决。但我们认为,公平地说,必须承认,向 PCI-Express 4.0 的过渡还有其他技术问题需要解决,就像以太网路线图在 10 Gb/s以上存在问题,无法直接跳跃到 100 Gb/s一样,必须先采用 40 Gb/s的循序渐进的方式,然后在超大规模提供商和云构建商(以及包括 Broadcom 和 Mellanox等芯片商)说服 IEEE 采用更便宜的 25 Gb/s 通道信令。

事情发生了,PCI-Express 路线图就是其中之一。 正如您从我们去年对 PCI-Express 7.0 规范工作启动的报道中看到的那样:

我们认为外设卡、重定时器和交换机的 PCI-Express 路线图的节奏需要与计算引擎版本的节奏相匹配,根据规范,我们确实需要 PCI-Express 7.0,该规范甚至要到明年才会获得批准。 但考虑到 PCI-Express 6.0 是第一代使用 PAM-4 信令和 FLIT 低延迟编码的技术,因此可以从具有完善的 NRZ 信令的 PCI-Express 5.0 直接跳转到 PCI 预期的更快的 PAM-4/FLIT 组合。

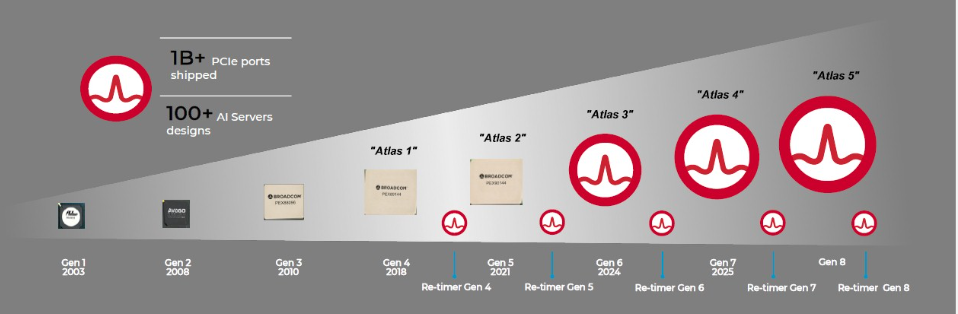

没有人比 Broadcom 更了解总线,由于 Avago 于 2014 年 6 月收购了 PLX Technologies,以及 Avago 于 2015 年 5 月收购了 Broadcom,Broadcom 生产 PCI-Express 交换机和重定时器,可扩展插入其中的铜线范围。 公司正在准备其“Atlas 3”代 PCI-Express 交换机和重定时器,它们基于实现 PAM-4 信令的“Talon 5”SerDes 系列。 Talon 5 SerDes 与“Peregrine”PAM-4 SerDes 相关,但又有所不同,“Peregrine”PAM-4 SerDes 用于“Tomahawk 5”和“Jericho 3-AI”系列以太网交换机 ASIC,这是因为 PCI-Express 是绝对无损的协议,因此有更严格的低延迟要求。

为了帮助服务器制造商和外围设备制造商朝着同一个方向努力,Broadcom 开始发布其 PCI-Express 交换机和重定时器路线图。

有趣的是,Broadcom 本来打算退出重定时器业务,但被其客户和合作伙伴拉回了该业务,从技术上讲,这个故事是为了揭示 PCI-Express 重定时器 Vantage 5 和 6 系列的一些细节。

Broadcom 数据中心解决方案集团副总裁兼总经理 Jas Tremblay 告诉 The Next Platform:“我们一直希望重定时器成为交换机的配套芯片。我们相信 PCI-Express Gen 5 重定时器将成为一种商品,并且将有三到四家供应商成功地将这些产品推向市场。 因此我们将全部精力集中在交换机和其他更高复杂性的 PCI-Express 5.0 产品上。 但我们完全错了。 客户回到我们这里是因为重定时器太多比任何人想象的都难。 当然,我们必须确保交换机和重定时器工作,并且它们非常可靠,但我们实际上必须确保它经过检测,以便我们可以帮助系统提供商和云提供商查明设备中发生的情况。 ”

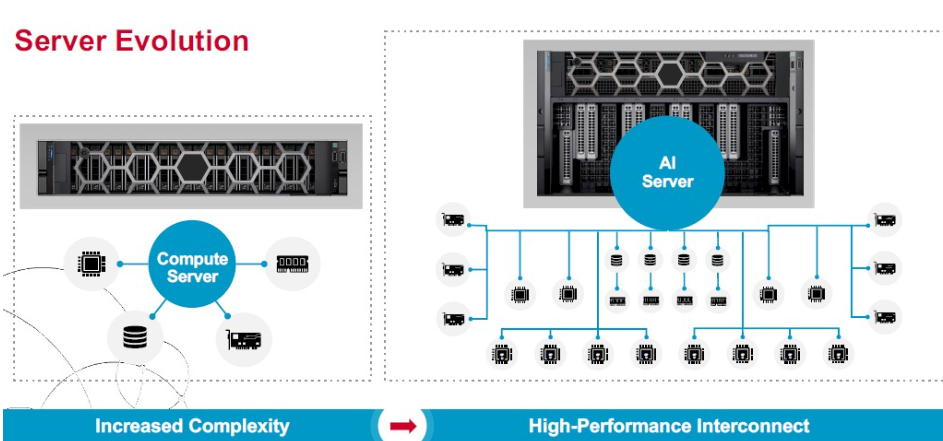

重定时器是 PCI-Express 硬件和固件堆栈中日益重要的一部分。 首先,服务器正变得比二十年前更加复杂,当时 PCI-Express 3.0 统治了世界,而我们所需要的只是更多的通道而不是更快的通道(根据英特尔的说法)。 当涉及到节点内部的 PCI-Express 互连时,看看通用服务器和 AI 服务器之间的区别:

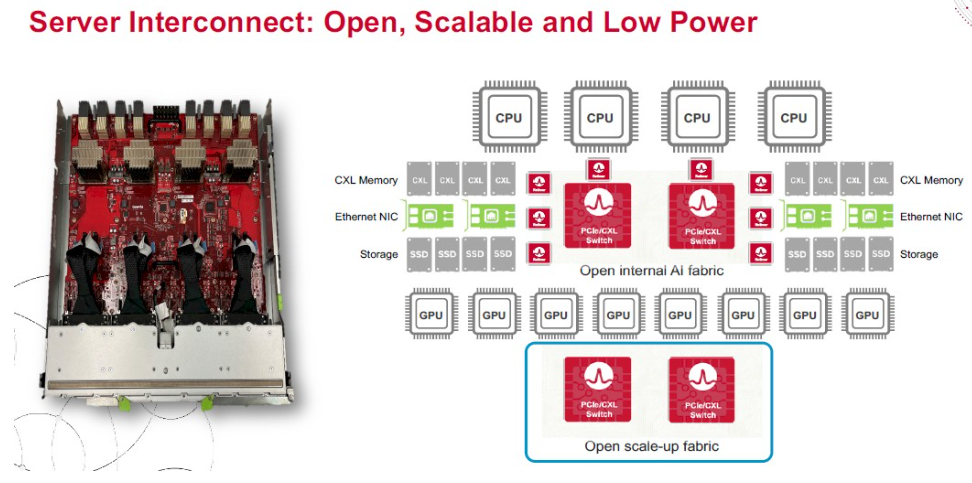

我们已经从与少数设备(一个或两个磁盘控制器、一个网络控制器,也许还有一些其他专用外围设备)的点对点互连(挂在 PCI-Express 总线上)转变为相当于 PCI-Express 交换结构的设备,用于将 CPU 连接到加速器、网络接口、闪存以及即将推出的 CXL 扩展内存。也许有一天,我们可能会看到通过 PCI-Express 链路链接的 CPU 运行 CXL 协议,而不是专有的 NUMA 互连,或者更有可能的是,专有覆盖运行在 PCI-Express/CXL 之上,因为看起来 AMD 和 Broadcom 正在致力于未来的 CPU 和 GPU。

但还有另一个问题,这就是重定时器的用武之地。

带宽每增加一倍,PCI-Express 信号通过铜线传输的距离就会减半。 重定时器用于延长铜线的长度; 电线越长,需要的重定时器就越多。 由于延迟问题以及 PCI-Express 用作 CPU 总线的扩展这一事实,尽量不要让线缆变得太长。 但是,如果您想将 PCI-Express 结构扩展到多个机架,甚至一整排机架上,那么随着 PCI-Express 的发展,带宽越来越高,重定时器的需求将会越来越大。

Broadcom 最新的 Vantage 5 和 Vantage 6 重定时器仅增加 6 纳秒的延迟来延长 PCI-Express 6.0 信号的长度,考虑到这种 PCI-Express 结构将消除对 InfiniBand 或以太网的需求,这似乎是相当低的开销。 Broadcom 作为 Ultra 以太网联盟的创始成员,致力于使以太网比 InfiniBand 更好,其 Jericho 3-AI 深度缓冲交换机 ASIC 是这一努力的第一步,希望在节点内实现 PCI-Express 交换,以太网可以更好的横跨机架,PCI-E则可连接服务器内部。但这很大程度上取决于重定时器和用于构建集群的交换机级别,以及 PCI-Express 结构与 InfiniBand 和以太网相比的总体成本。

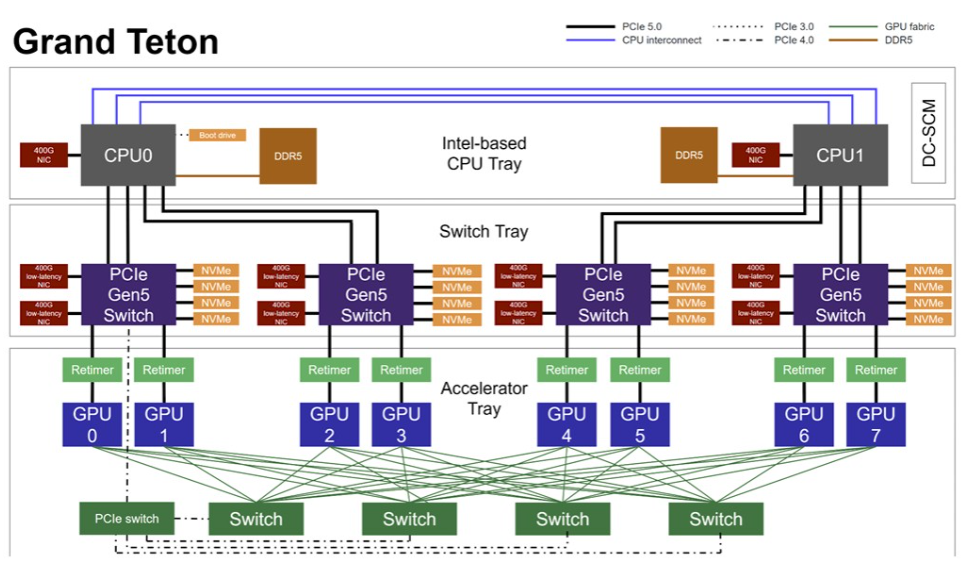

现代人工智能服务器的内部结构如下所示:

这是“Grand Teton”人工智能服务器的框图,Meta Platforms 早在 2022 年 10 月就将其作为开放计算项目设计推出。

在该 Grand Teton 服务器中,有一对 PCI-Express 交换机,用于将四个 CPU 连接到以太网 NIC、闪存和 CXL 内存,并通过重定时器增加外设和交换机之间的连接长度。 还有另一对 PCI-Express ASIC 用于互连八个 GPU,以便它们可以共享内存。 Grand Tetons 基于 PCI-Express 5.0,即 Vantage 重定时器和 Atlas 2 交换机 ASIC。 这些 ASIC 中的每一个都有 114 个 PCI-Express 5.0 信号通道,可在所有设备上产生 57 TB/秒的聚合带宽。

这是一个不同的(也许更准确)框图,显示了 Grand Teton 系统中如何使用开关和重定时器,该框图来自其 OCP 规范:

这些规格在 2022 年 10 月尚未提供。

正如您所看到的,重定时器实际上用于扩展 PCI-Express 交换机和 GPU 之间的链接,而其他外设则直接链接到 PCI-Express 交换机。 这并不完全是博通图表所暗示的。 交换机和重定时器的数量相同,但拓扑结构不同。 此外,NVSwitch 互连仍然用于将 GPU 相互链接,尽管有一个辅助 PCI-Express 4.0 交换机将 GPU 连接到其中一个 PCI-Express 5.0 交换机,可能作为管理互连或作为一种手段 将数据发送回 CPU,而无需通过重定时器返回。 这是一个有趣的示意图。

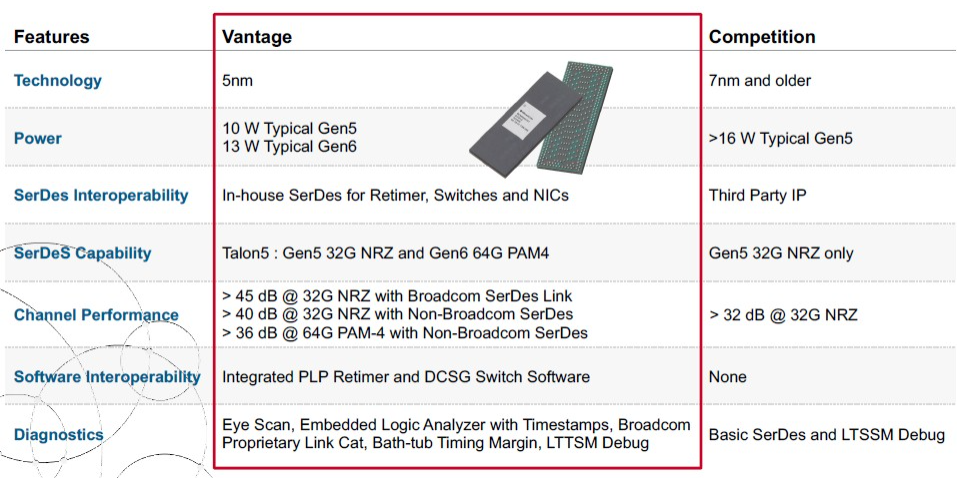

回到重定时器。 以下是与 PCI-Express 5.0(“Atlas 2”)和 PCI-Express 6.0(“Atlas 3”)交换机 ASIC 搭配使用的 Vantage 5 和 Vantage 6 重定时器的显着特征:

因为它们驱动 64 Gb/秒 PAM-4 信号Vantage 6 重定时器的运行温度比 Vantage 5 重定时器稍高,后者仅执行 32 Gb/秒 NRZ 信令。 两个重定时器都使用相同的 Talon 5 SerDes,支持任一信号发送方法,并且两个 Vantage 芯片均采用台积电的 5 纳米工艺。

目前尚不清楚为什么 Vantage 6 在使用 64 Gb/秒 PAM-4 信令连接到 Broadcom SerDes 时没有通道性能规格。 也许博通暂时隐瞒了这些信息。 显然,Broadcom 希望为客户提供端到端连接,甚至希望尝试在某些设计中取代 NVSwitch,一旦 PCI-Express 能够完成这项工作,超大规模提供商、云构建商以及世界各地的 HPC 中心都希望这样做 。

Tremblay 表示,在重定时器和交换机上使用 Talon 5 SerDes 时,其芯片的组合可将覆盖范围扩大 40%,从而提供比 PCI-Express 5.0 规范要求的信号好 12DB的信号。 Talon 5 SerDes 架构与5 纳米的工艺相结合(与竞争对手的 PCI-Express 交换机和重定时器的 7 纳米工艺相比),功耗也降低了 50%。

顺便说一句,Broadcom 确实考虑过从 PCI-Express 6.0 直接迁移到 PCI-Express 8.0,完全跳过 PCI-Express 7.0,试图让计算和 I/O 恢复更好的平衡。 但有很多计算引擎制造商、服务器制造商和外围设备制造商需要与博通一起实现这一跨越,但这是不可能的。 如果 Broadcom 采用这种策略,客户就会将 PCI-Express 7.0 的设备插入 PCI-Express 8.0 插槽中,并以较慢的兼容模式运行它们。

本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。