近日,鸿芯微纳研发副总裁肖勇和高级研发总监冯春阳受邀参与校企合作单位之一上海交通大学微纳电子学系“2022年春季校企共建课程第七讲”上半场的主讲。

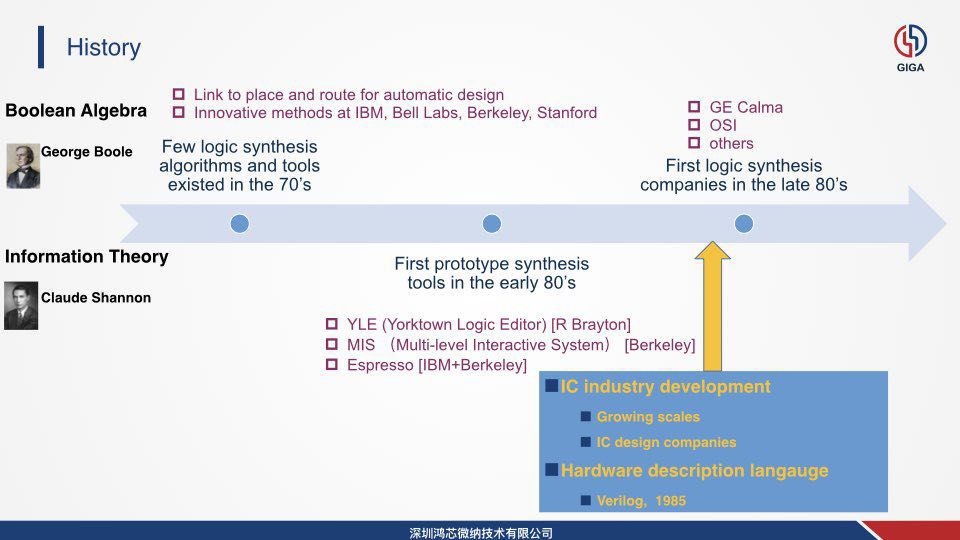

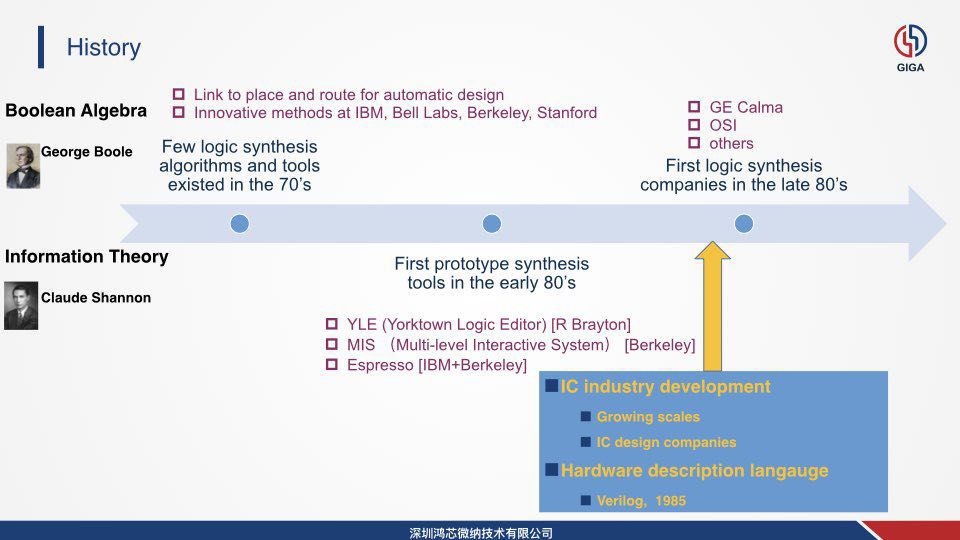

副总裁肖勇使用图解的方式,详细地介绍逻辑综合在IC设计领域的重要性,并按照时间顺序梳理逻辑综合工具的发展历程。随后介绍逻辑综合的基本流程,包括HDL编译、High-level & Datapath优化、逻辑优化、时序分析和优化等,并总结目前逻辑综合工具发展存在的一些挑战和未来的发展趋势,如将逻辑综合和物理综合相统一、将机器学习的预测和分类功能应用于逻辑综合等。

近日,鸿芯微纳研发副总裁肖勇和高级研发总监冯春阳受邀参与校企合作单位之一上海交通大学微纳电子学系“2022年春季校企共建课程第七讲”上半场的主讲。

副总裁肖勇使用图解的方式,详细地介绍逻辑综合在IC设计领域的重要性,并按照时间顺序梳理逻辑综合工具的发展历程。随后介绍逻辑综合的基本流程,包括HDL编译、High-level & Datapath优化、逻辑优化、时序分析和优化等,并总结目前逻辑综合工具发展存在的一些挑战和未来的发展趋势,如将逻辑综合和物理综合相统一、将机器学习的预测和分类功能应用于逻辑综合等。

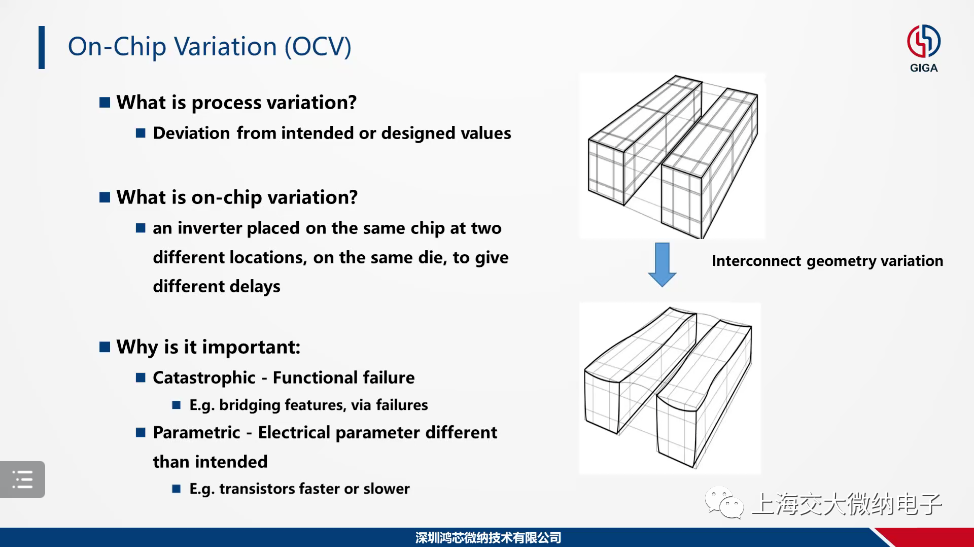

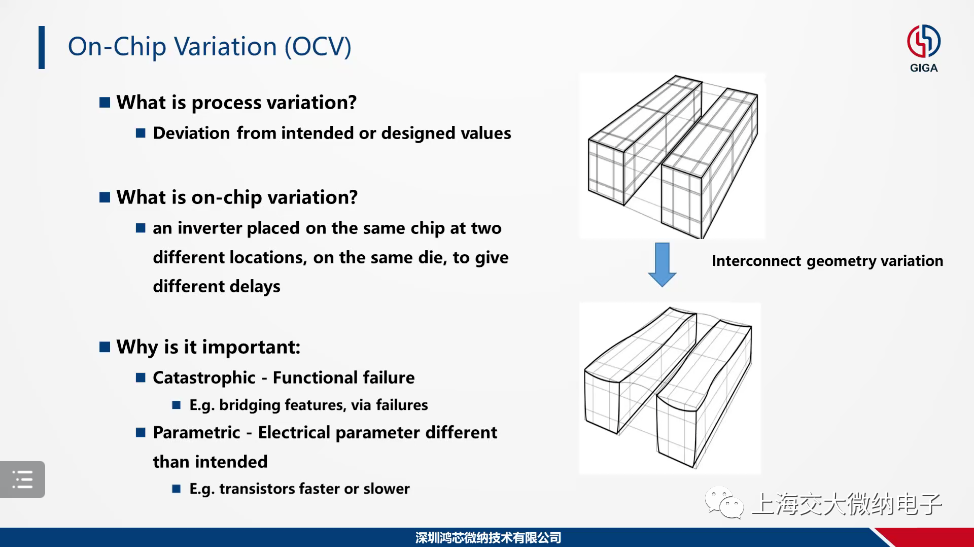

此后,高级研发总监冯春阳针对时序分析中片上偏差建模,展开课程讲授。首先从原理的角度,介绍什么是工艺偏差(On-Chip Variation)、工艺偏差的来源以及工艺偏差在时序分析中的重要性。同时介绍针对该偏差的相关修正方法,如使用PSM、OPC等光学矫正技术对光刻引起的系统性偏差进行优化等,并针对随机性偏差,详细介绍OCV-Margins、Advanced OCV、Statistical OCV等方法,从而对线路延迟进行降低,优化片上偏差。

本次讲座以线上方式举行,内容充实,干货满满,现场互动积极,气氛热烈。该讲座是与上海交通大学校企合作的项目之一。为了培养EDA人才,鸿芯微纳自成立开始便积极谋求与高校的合作,目前已与清华大学、上海交通大学、中国科学技术大学、西安电子科技大学、南方科技大学、宁波大学等众多高校建立合作。未来鸿芯微纳将与更多的高校一起,合作共赢,为产业培养人才,为国产EDA做贡献。

责编:Johnson Zhang

此后,高级研发总监冯春阳针对时序分析中片上偏差建模,展开课程讲授。首先从原理的角度,介绍什么是工艺偏差(On-Chip Variation)、工艺偏差的来源以及工艺偏差在时序分析中的重要性。同时介绍针对该偏差的相关修正方法,如使用PSM、OPC等光学矫正技术对光刻引起的系统性偏差进行优化等,并针对随机性偏差,详细介绍OCV-Margins、Advanced OCV、Statistical OCV等方法,从而对线路延迟进行降低,优化片上偏差。

本次讲座以线上方式举行,内容充实,干货满满,现场互动积极,气氛热烈。该讲座是与上海交通大学校企合作的项目之一。为了培养EDA人才,鸿芯微纳自成立开始便积极谋求与高校的合作,目前已与清华大学、上海交通大学、中国科学技术大学、西安电子科技大学、南方科技大学、宁波大学等众多高校建立合作。未来鸿芯微纳将与更多的高校一起,合作共赢,为产业培养人才,为国产EDA做贡献。

责编:Johnson Zhang