版权声明:本文由半导体行业观察翻译自Semiconductor Engineering ,如您觉得不合适,请与我们联系,谢谢。

这些年来,一个承担起缩小晶体管尺寸,延续摩尔定律的设备——EUV光刻让行业都头疼,在行业巨头投入了数量庞大的基金和资源研发数年之后,依然是没见到大规模投入使用,显而易见的问题,业界在EUV光刻这里碰到问题了。

但看起来EUV光刻离第一次大规模应用脚步更近了。Intel和三星已经把EUV光刻写进了他们的Roadmap,分别是在2018和2019年。除此之外,三星也希望把EUV应用大1Xnm级别的DRAM上。

但并不是每一个芯片制造商都把希望寄托在EUV光刻上,TSMC表示在7nm的时候会依赖于193nm沉浸式光刻和多重pattern,去到5nm的时候才会寄望于EUV。GlobalFoundries也有同样的规划。

当然,这些Roadmap并不是一成不变的,是可以根据实际情况做修改了。尤其是过去一两年,EUV已经让人失望了很多次。现在EUV离真正投产似乎还有一段时间,业界也有一些人开始对其有所怀疑了。

无论如何,芯片制造商基本上一致认同,到7nm和5nm的时候,半导体对EUV的需求是很迫切的。

“从现在的状况看来,业界似乎都在做好两手准备,预防EUV最终流产,并在先进制程上依赖于沉浸式光刻”。三星半导体晶圆业务高级VP HongHao表示。

在过去几年,芯片制造商还可以依靠于沉浸式和多重pattern将工艺制程从16nm/14nm推到10nm甚至7nm,但是到了7nm之后,这些技术就不能保证工艺可以向前推进了。从技术上来看,我们可以使用一种叫做八倍pattern的技术去延伸传统光刻,但这种方式具有不确定性,同时有点得不偿失。

“但一切皆有可能”,光刻专家Chris Mack表示。如果价格在某一个能接受的范围,没有什么是不可能的,他补充说。

这是一个有争议性的话题。

但有一点需要肯定的是,没有EUV光刻,芯片不能按照摩尔定律那样约定俗成去降低尺寸,甚至会逐渐停止缩小尺寸,到时摩尔定律就真正失效了。

EUV 碰到的问题

事实证明,EUV比想象中难控制。纵观整个IC产业的发展,EUV光刻算得上是迄今为止碰到最难解决的问题。

EUV的电源将等离子体转换成13.5nm波长的光线,然后经过镜子的几重反射之后,再打落到晶圆上。现在的EUV可以在晶圆上“打印”一些小功能,但现在EUV碰到的主要问题是电源。现在的电源并不能产生足够的功率让EUV大幅度提高效率,且不能满足经济可行性。也因为这个重要原因,EUV的面世时间从上一个节点延误到现在。

从eBeam Initiative最近的一个调查中可以看出,事情似乎正在转变,业界对EUV的信心似乎正在逐渐提升。光刻机的主要供应商ASML似乎也在电源问题上取得了重大进展。光刻胶和光罩似乎也取得了长足进步。

但关于EUV的讨论依然没有停止,现在关注的问题转移到工具价格、运行时间和随机现象。

很多人都在声称,EUV将会在2018或者2019年大批量投产。如果真的是这样,业界肯定会热烈拥抱这个技术。但我们也要对EUV抱有悲观态度,毕竟任何事都有可能发生。

为什么要用EUV?

关于EUV技术可以溯源到20世纪70年代,那时候业界刚好开发出X光光刻,那是一种依赖于大型同步回旋加速器的技术。但由于X光光刻比较高,最终在上世纪80年代,宣告失败。

然后X光光刻转变成一种叫做软性X光,或者称作EUV的技术。通过使用多层的镜子,让这个技术变得更实际。于是从上世纪80年代开始,业界就投入到了EUV光刻的研发,但直到21世纪出,这个技术才取得了业界认可的突破性进展。也就是在那时,芯片制造商表示,传统光刻将会在65nm或者45nm的时候遇到障碍,由此亟需下一代的光刻技术,去缩小晶体管的规模,延续摩尔定律。

多年以后,EUV已经成为下一代光刻技术中的佼佼者,其他的竞争技术,如自组装技术、电子束直写和纳米打印技术都现实不见了。

业界指望下一代光刻技术能给业界带来新的颠覆,但从目前的状况看来,似乎还没准备好。

传统的光刻技术开始逐渐违背物理定律了,但无奈地还得充当Fab的主流技术。现在应用在Fab的先进光刻技术,就只有193nm沉浸式光刻,但也只能在晶圆上打印一下细小的功能部件,并不能大规模应用。

按理说,193nm光刻在80nm的时候就会碰到瓶颈。但芯片制造商通过应用分辨率增强技术(RETs),将193nm光刻技术应用在远低于这个波长的场景。

有了RETs,光刻机在28nm的时候只需要一次的光刻曝光就可以实现了。但到了22nm/20nm,单次曝光有时候就不能给临界层提供足够的分辨率。芯片制造商就通过多重pattern的方式解决问题。这也就是增加了一个简单的两步流程。

应用材料的VP Uday Mitra表示,现在的pattern也就需要两个基本的操作。第一步就是line/space;第二步是cut。

第一步就是光刻机在设备上刻下很小的线。Mitra还表示,现在的公司都在使用line/space,之后还会继续使用基于spacer的SADP和SAQP多重pattern技术。

这当中的主要的挑战就是刻这些细线图案。为了达到目标,芯片制造商只好使用双重pattern技术。在这个步骤里会需要两次光刻和刻蚀步骤去确定一个单层。这就是我们声称的LELE技术。

使用这种双重pattern技术,可以节省30%的pitch,而三重pattern则需要三次曝光,也就是需要三次刻蚀步骤(LELELE),当然,SADP和SAQP也可以在刻的时候应用上。

除此之外,业界在10nm和7nm还会碰到其他问题。在45nm和40nm的时候,设计的时候需要用到40层光罩,而到了14nm和10nm,光罩的需求量则上升到60层。“如果没有EUV,只是靠沉浸式去实现三倍甚至四倍pattern,那么我们认为在7nm的时候,光罩数量会上升到80到85层之间”。三星的晶圆制造资深主管Kelvin Low表示。

光罩层数的增加,也就代表着成本的水涨船高。同时覆盖物也将会成为Fab的灾难。覆盖物需要把光罩层有秩序的精确地放置在彼此的身上。而随着mask的增加,覆盖层也就会成为噩梦。如果没对齐,覆盖层问题就够你喝一壶了。

另外,现在做一层光罩需要1到1.5天,在7nm的时候使用多重pattern,那就需要差不多五个月的时间才能做好晶圆。

但不妨碍很多人把EUV当做现代半导体的救星。

有了EUV,你就不需要那么多层,ASML的产品市场主管Applied’s Mitra说。届时你会把光罩的层数降到60左右,而晶圆的出厂时间也会缩短到一个月。

同时我们要明白到,并不是每层光罩都需要EUV,沉浸式/多重pattern在很多场景下都能用得上。

虽然已经投入了那么多去研发,但现在看来EUV还没准备好。在正式投产之前,EUV还需要获得更多的信息,去推动发展。EUV也有另外的路径,但改善率不高,没有很明显的优势,也不能满足大型芯片制造商的需求,因此EUV需要进一步发展,满足需求。

我们也要明确一点,并不是所有的层都会用到EUV,沉浸式/多重pattern也会在很多功能件上用到。

我们也要明白这一点,对于未来的某些功能,只有EUV才能做到,因为其他方案还没能实现,比EUV更不堪。

通过八倍pattern去扩展光刻是很有问题的。这事你会面临很多问题,最大的挑战则是cut。

在过去的几年,ASML已经推出过几个版本的EUV光刻机,但目前来说,这些光刻机都是只能用于研究,ASML也将其光源功率共80瓦提升到123瓦特。而工作效率也提升到60~85wph。

业界希望EUV在正式投入使用之前,能够用上250瓦特的光源。届时生产效率就提高到125wph。

现在EUV工具的可用性是70%到80%,这离业界宣传的的90%甚至以上的可用性目标还有一段距离。

如果ASML真如他们所说,在明年推出其首个量产机器NEX:3400B,那么会面临很大的考验。它的数控直径是0.33,分辨率是13nm,ASML也将其电源功率提升到200瓦特。

EUV 工作原理

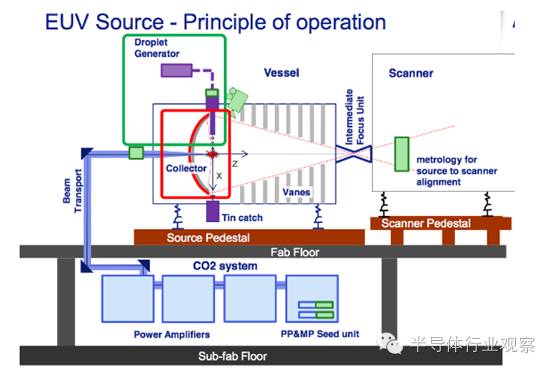

所有的关键就是它的“源”,基于激光等离子体的EUV“源”包括几个部分,当中有二氧化碳laser,通过它给“源”提供能量,在实际使用中会被放置到Fab的地板下面。

Laser包括了两部分,一个是seed laser(前脉冲和主脉冲),另一个是功率放大器。现在的EUV“源”使用一个20千瓦的laser。

现在EUV的“源”都是被放置到FAB地板下面,而回到EUV扫描器,“源”包括液滴发生器,采集器和一个真空室。EUV的生产步骤是在真空环境中进行的,因为几乎所有的东西都能够吸收EUV光。

液滴发生器是一个小的容器,在实际的使用过程中,锡被装载入发生器里,然后被加热。然后一系列的液态锡会从发生器中流出来,经过一个过滤器,然后进入“源”的真空室。液滴的直径是25微米,而下降的速率也高达50000次/秒。

在容器里面,有一个摄像头。液滴经过真空室某个位置的时候,摄像头会告诉Fab底下的seed laser发一个激光脉冲到真空室里面。这个就叫做前脉冲。

然后就到了最难的一部分。前脉冲激光击中圆形锡液体,将其变成薄饼型。然后激光单元又会激活,这就是主脉冲。然后主脉冲就会集中薄饼形的锡液滴,并将其气化。

ASML的Lercel表示,他们希望在将来,前脉冲和主脉冲能够击中锡液滴2次,同时每秒钟能够击50000次。

这时候,锡蒸汽就会变成等离子体,然后等离子体会发射13.5nm波长的EUV光线。

所以关键就是准确地集中锡液滴。因为这决定了有多少激光的能量可以转变为EUV光线。我们把它叫做转换效率(CE)。现在,ASML的电源转换效率大概是5%。“随着我们改变锡液滴的形状和提高集中液滴的效率,我们才能比过往拿到更好的表现”。Lercel表示。

与此同时,一旦EUV光线生成了,光子就会打到一个叫做采集器的多层镜子上。光就会再采集器中反弹,然后穿过中间焦点单元,进入扫描器中。

EUV的原理

EUV的原理

随着时间的流逝,飞溅的锡和采集器收集的材料会对转换效率造成影响,这时候就需要换一个新的采集器,这是一个耗时且昂贵的过程。

诚然,ASML正在定位这些问题:

(1)更好的液滴发生器

液滴发生器可以连续工作1400小时,自去年以来,得到了五倍的提升。未来的目标是提升发生器的可预测性。

(2)采集器清洁

采集器每三个月就要置换一次。未来的目标是一年换一次。此外,ASML为采集器推出了一种现场清洁系统,但这个系统还在完善当中。

采集器是只是EUV保养中的一个问题。

由于EUV是工作在真空黄牛的系统,刻蚀和沉积都是在真空完成的,因此你需要抽空环境。然后你打开真空室,去解决一些潜在的问题。而抽空一个EUV 真空管是一个头疼的问题,因为这也会导致故障。

光刻专家Ben Eynon表示,没有任何人谈过这个问题。我觉得我们需要谈一下这些采集器的预计上线时间和购置花费等问题。

(3)250瓦特“源”

ASML和Gigaphoton正在努力解决这个问题,但预计到2019年才能克服这个额外难题。

(4)薄膜

EUV薄膜是必须的,ASML和合作者正在这些领域进行努力。

扫描晶圆

上面提到,经过了一系列的路径以后,EUV光会进入扫描器,在扫描器内,光会走过一段10个平面的复杂组合,或者走过一个多重镜子组合。

首先,光会经过一个可编程发光器。它形成了一个瞳孔形状,把适当亮读的光打向了EUV 光罩。

然后EUV光会在光罩上“走”过,在投影光刻里,它会反射多达六层的镜子,然后光会以6%的角度打在晶圆上。

准确的反射光线

准确的反射光线

每一个多层镜子会反射70%的光。基于多样的计算,EUV扫描器的传输率只有4%。

在经历过这一系列的动作以后,晶圆就被加工了。

首先,光打在晶圆的光刻胶上。抗蚀剂则是光感材料。将其暴露在光纤之下,就会在平面上形成一个团。

现在,EUV抗蚀剂的敏感度为每平方里面31微焦耳,这比期待目标低了不少。

如果我们的抗蚀剂敏感度能够达到每平方厘米20微焦耳,那么成本就会和沉浸式的三次pattern的成本差不多。格罗方德的高级Fellow Harry Levinson表示。

如果抗蚀剂的敏感度是30mJ/cm2,在125瓦的电源的下,EUV光刻机的工作效率会达到70wph。但在实际应用中,实际效率只有50%左右,或者说每天只能加工840片晶圆。

相同抗蚀剂的情况下,如果电源升到250瓦,那么效率就可以提到90wph。

EUV抗蚀剂也会面临其他问题。

在EUV,光子的散射噪音会引起随机现象、刻线边缘粗糙度和接触口粗糙度等困扰,并最终会对产能造成影响。光刻专家Mack表示。

半导体刻线边缘粗糙度(LER)是EUV的一个重要问题。LER是线宽问题的变种。Lam Research 的CTO Dve Hemker表示。

我们还会碰到其他的问题。如果我们把这些问题都解决了,我们就可以真正用上EUV。

EUV 的实际使用

很庆幸,现在的芯片制造商在16nm/14nm和10nm制程的时候还可以使用沉浸式和多重pattern技术。

但在7nm的时候,对每个制造商来说都是一个困难的挑战。

三星方面表示,如果在7nm的时候没有EUV,会带来很多技术和成本的挑战。具体来说在晶圆、光罩、设计和开发时间上面,都需要很高的时间和金钱成本。

而TSMC为了更快的将产品推向市场,计划将沉浸式和多层pattern推向7nm,并期望在7nm的时候打败其竞争对手。

这就给晶圆厂带来了困难的选择。

如果你想学TSMC那样,那么你在芯片设计上就多了很多限制。它改变了你设计芯片的方法。

如果你选择EUV,你会开启一个全新的设计,你需要看到两三年前技术细节,因为这正是芯片设计的周期。

如果EUV真的到来了,那么芯片制造商会将其应用到哪里呢?

首先,它必须要有经济意义。

我们知道,7nm对EUV的渴求比任何时候都强,但我们只会在其到来之后才用。我们在应用EUV的时候一定要小心,因为我们毕竟要用它去替代三层的193nm光罩。

其他人也同意这个观点。

在7nm的时候,我们或多或少会接触到EUV。我们或许会在fin、栅极切割和Mx切割上用到,还可以在过孔的地方使用这个技术。

所以说EUV并不会被应用到所有位置。

当然,EUV还会很多困扰,例如EUV用到的是13.5nm技术,而现在芯片制造商提到的是7nm芯片,因此在这个情况下,是否需要两次的pattern?

简单来说,7nm是市场的选择。但还需要面临各种各样的挑战。我们何事才能看到呢?

【关于转载】:转载仅限全文转载并完整保留文章标题及内容,不得删改、添加内容绕开原创保护,且文章开头必须注明:转自“半导体行业观察icbank”微信公众号。谢谢合作!

【关于投稿】:欢迎半导体精英投稿,一经录用将署名刊登,红包重谢!来稿邮件请在标题标明“投稿”,并在稿件中注明姓名、电话、单位和职务。欢迎添加我的个人微信号MooreRen001或发邮件到 jyzhang@moore.ren

点击阅读原文加入摩尔精英