三星拟新设至少10台EUV光刻机:展露要当世界第一的野心

最新消息显示,尽管全球经济将放缓,但仍计划扩大DRAM与晶圆代工的晶圆产能,明年在其P3晶圆厂新设至少10台极紫外光刻设备(),用于生产最新的12nm级内存芯片,而目前仅有40台。

本文引用地址:是全球第一大DRAM内存芯片公司,并从14nm级别的内存芯片开始引入。

据悉,三星在韩国的内存工厂主要是位于平泽市的晶圆厂,其中P3晶圆厂目前的产能是每月2万片晶圆,三星已经计划扩大投资,增加内存生产设备,将产能提升到每月7万片晶圆。

据了解,目前三星在韩国有5家半导体工厂,分别位于器兴、华城、平泽、温阳和天安。此外,在中国苏州、天津和西安还运营有三家芯片工厂,在美国得克萨斯州奥斯汀也有一家芯片工厂。

三星最大的半导体工厂便是平泽的P3工厂,该工厂从2020年年底开始建设,历时近两年建成,从今年7月份开始生产最尖端的NAND闪存芯片,未来可能还会生产应用处理器和其他半导体。

三星2022年第三季度财报显示,其运营利润为10.85万亿韩元,同比下滑31.4%,环比下降23%;净利润为9.39万亿韩元,同比下滑23.6%。

由于需求下降和芯片供应过剩,各大厂商纷纷缩减投资。但三星在今年10月份表示,他们不会有意削减芯片产量,这与整个行业削减产量以满足中长期需求的趋势相反。

三星的半导体野心

在全球晶圆代工行业,台积电、三星两家率先进入到了10nm以下制程,都实现了7nm和5nm工艺的量产,并且还都在向更先进的3nm工艺冲击。

台积电的芯片代工市场份额占到全球的半数以上,差不多在54%左右;而三星全球第二,但市场份额也只有18%左右,仅仅是台积电的三分之一。台积电在市场份额和技术上一直领先,但三星也一直在努力追赶。

三星制定了2030年重回半导体第一的目标,为此开始大举投资建厂,但还需要更多的关键制造设备 —— 那就是ASML的EUV。

为争取更多的EUV光刻机,三星高层去年就到ASML总部争取 。今年6月14日,三星副会长李在镕造访ASML荷兰总部,拜会了ASML首席执行官Peter Wennink等高管,广泛讨论半导体技术的未来、市场前景及EUV设备的供应,并取得“额外”的EUV光刻机设备,不过三星未详细说明此次获得的“额外”EUV设备内容。

报道称,今年ASML的EUV光刻机出货量估计为51台,此次三星若能争取到更多EUV机台,则今年至少可获得18台,台积电则至少确保22台。业界此前传出,去年ASML的EUV设备年度出货量为48台,其中15台由三星夺得,20台由台积电包办。

ASML是全球唯一的高端芯片制程设备制造商,EUV设备的稳定供给,是三星超车台积电、抢下全球半导体龙头的关键。三星2000年代开始与ASML在半导体制程与设备开发方面进行合作;2012年,三星入股ASML强化双方伙伴关系。

对新一代High-NA EUV光刻机的争夺

另外,三星还与ASML达成协议,争取到了下一代高数值孔径极紫外光刻机(High-NAEUV)光刻机,据ASML最新披露,High-NA EUV设备将于明年年底推出初始版本,量产型号将于2024年底或2025年初推出。

相比DUV浸没式光刻机采用193nm波长的深紫外光,EUV光刻系统中使用的极紫外光波长仅为13.5nm。EUV单次曝光就可以替代DUV的多重曝光步骤,可以帮助芯片制造商继续向7nm及以下更先进的工艺推进,同时提升效率和降低曝光成本。

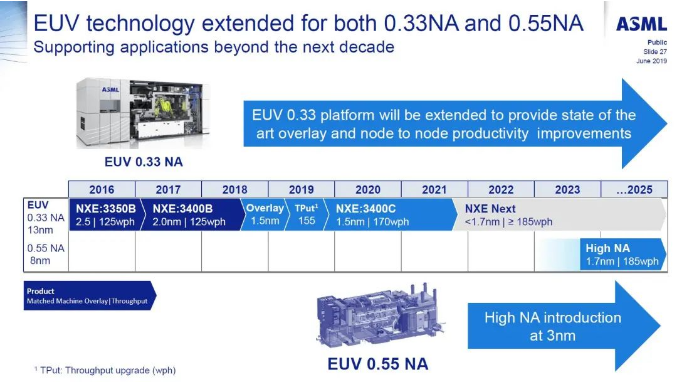

然而,目前芯片制造商已将制造工艺推进到3nm左右,如果要继续推进到2nm制程甚至更小的尺寸,就需要更高数值孔径(NA)的High-NA EUV。相比目前的0.33数值孔径的EUV光刻机,High-NA EUV光刻机将数值孔径提升到0.55,可以进一步提升设备的分辨率(根据瑞利公式,NA越大分辨率越高),通过多重曝光技术可支持2nm及以下芯片工艺的制造。

目前虽然三星宣布了3nm率先量产,但是3nm的新工艺还存在风险,良率和功耗都还表现不佳,导致还没有获得任何一家美企的订单。而台积电沿用老工艺, 之前还表示各项数据优于三星 。

三星、台积电都在使用EUV光刻机生产制造3nm芯片,但实际上已经有点力不从心了:三星采用了全新的GAA工艺,性能和功耗提升明显,但良品率成了最大的问题;台积电采用传统工艺,良品率得到了保证,但性能和功耗提升欠缺。并且,无论是三星的GAA工艺还是台积电的传统工艺都面临成本高的问题。

High-NA EUV光刻机交付后,更为先进的技术能够在单元面积中内置更多晶体管,从而进一步提升性能、降低功耗和成本,也能够加速2nm芯片的到来。

值得注意的是,三星在5/4nm时代因良率不佳导致订单落后于台积电后,希望通过下一代的产品技术革新扭转局面。这种背景下获得了新一代EUV光刻机的消息,有助于在跟台积电的竞争中优势进一步提升,就看谁能率先利用起来。

目前,为了满足高性能计算的需求,台积电、三星、英特尔三大芯片制造商正在大力投资更先进的3nm、2nm技术,所以EUV的放量及新一代High-NA EUV的入场成为了争夺的关键。

未来的芯片设计会更加多样化

人类在芯片制造技术探索了半个世纪,从最初的微电子处理器到如今的高端纳米制程工艺,可以说实现了从地面到天上的飞跃。伴随着芯片制造技术的提升,一些半导体设备,制程工艺都在持续突破。

用EUV光刻机造高端芯片成为了行业常识,只有EUV光刻机的极紫外光源才能达到7nm、5nm等制程所需的分辨率和精度。

但是获取EUV光刻机是有难度的,一方面价格昂贵不是所有厂商都能买得起,另一方面EUV光刻机产能有限,制造商ASML每年只能生产四五十台左右的EUV光刻机。

芯片巨头开始摆脱EUV光刻机的依赖,探索新工艺、新方向。

美光科技绕过了EUV光刻机,在DUV光刻机的支持下采用1β(1-beta)制造工艺的DRAM内存芯片LPDDR5X-8500,将内存产品能效提升15%,内存密度提升35%。

据悉,美光已将其送样给部分手机制造商、芯片平台合作伙伴进行验证,并做好了量产准备。如果不出意外,要不了多久应该会进入商用阶段。

1β工艺之所以能得到较大的能效,密度提升,其实是用DUV光刻机进行多重曝光,不仅实现了技术突破,而且绕开EUV光刻机之后还能节省额外的设备成本费用。

根据美光对1β采用的制造工艺的介绍,这种设计在复杂度上远超三星、海力士等同类产品。因为目前DRAM的先进性很大程度上取决于每平方毫米晶圆面积上集成半导体数量的能力,主要DRAM厂商目前基本上都是通过不断缩小电路面积提高继承度来进行竞争的。

芯片制造商们不断挖掘DUV光刻机的潜力,克服DUV光刻机的性能和EUV存在差距,把存在于理论的多重曝光用在了现实。

而在华为海思芯片代工受阻后,曾提出过通过芯片的分层叠加工艺,可以实现14nm工艺达到7nm的芯片集成度。思路和美光在DRAM上的思路有异曲同工之妙:设计芯片的焦点不再是紧盯光刻机的蚀刻纤细程度,而是转向了用设计来抵消EUV带来的更高精度。

事实上,近些年来芯片领域在先进封装技术、碳基芯片、光子芯片等领域都实现了突破。一旦芯片设计的多样化手段进入实际应用阶段,光刻机的发展前景将不再一枝独秀。

并且摩尔定律束缚的不仅仅是芯片的物理极限,还有半导体设备的技术天花板 —— ASML透露“下一代的NA EUV光刻机可能是最后一代NA,当前半导体光刻技术之路或已走到尽头,不过正在研究其它可行性替代技术。”

本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。