PCB走线角度为90度到底行不行?

现在但凡打开SoC原厂的pcb Layout Guide,都会提及到高速信号的走线的拐角角度问题,都会说高速信号不要以直角走线,要以45度角走线,并且会说走圆弧会比45度拐角更好。

事实是不是这样?PCB走线角度该怎样设置, 是走45度好还是走圆弧好?90度直角走线到底行不行?

大家开始纠结于pcb走线的拐角角度,也就是近十几二十年的事情。上世纪九十年代初,PC界的霸主Intel主导定制了PCI总线技术。

(很感谢Intel发布了PCI接口,正是有了PCI总线接口的带宽提升,包括后来的AGP总线接口,才诞生了像 3DFX VOODOO 巫毒这样的显卡,在当时也次体验到了古墓丽影 劳拉 的风采,还有暴爽的飞车2、经典的雷神之锤等等,回想起来,正是有了3D游戏等多媒体应用的市场需求,才促进了PC的技术的发展,包括后来的互联网及智能手机的普及。)

似乎从PCI接口开始,我们开始进入了一个“高速”系统设计的时代。

20世纪90年代以后,正是有了一帮这样的玩家对3D性能的渴望,使得相应的电子设计和芯片制造技术能够按照摩尔定律往前发展,由于IC制程的工艺不断提高,IC的晶体管开关速度也越来越快,各种总线的时钟频率也越来越快,信号完整性问题也在不断的引起大家的研究和重视。比如现在人们对4K高清家庭影音视频的需求,HDMI2.0传输标准速率已经达到了 18Gbps !!!

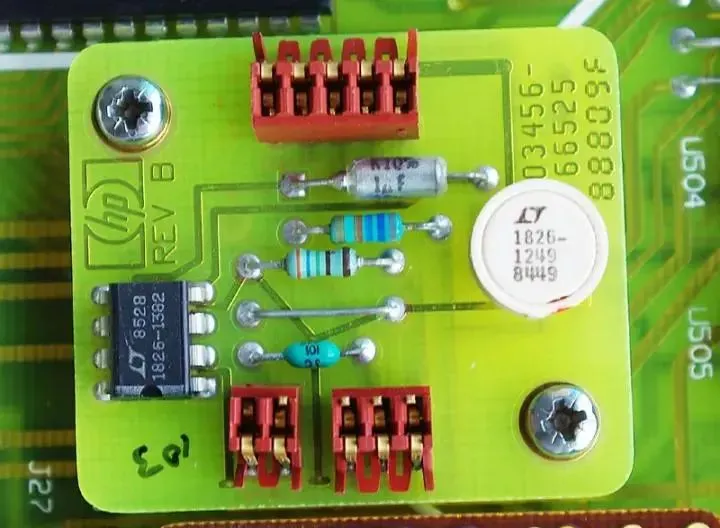

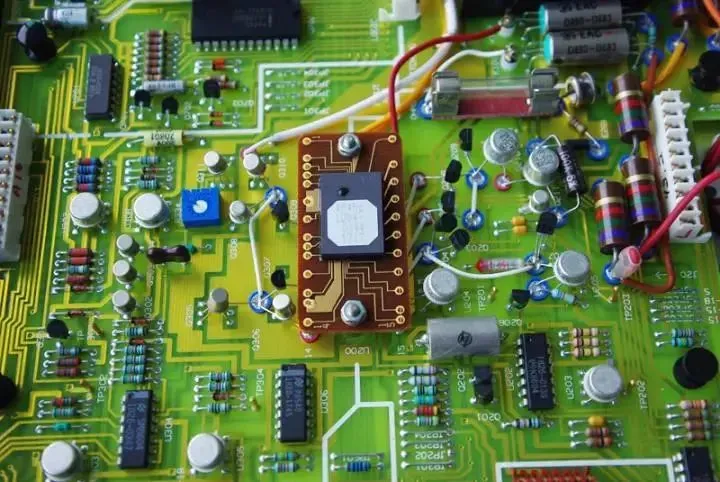

在我诞生之前,pcb拉线菌应该还是比较单纯的同学,把线路拉通,撸顺,整洁美观即可,不用去关注各种信号完整性问题。比如下图所示的 HP 经典的 HP3456A 六位半万用表的电路板所示,大量的90°角走线。

HP3456A 没有泪滴,几乎是故意走的直角(某些地方本来一个斜角走完,它偏要连续走几个直角),绝大多数地方没有铺铜。

右上角,拐直角不止,线宽还变小了?

直角、搭桥、铺铜,模拟就真的不能铺铜吗?

直角,45度斜线,任意角度斜线,方焊盘,圆焊盘,唯独不见泪滴。

高速信号线拐一下90°真的会怀孕?狮屎是不是这样的?老wu这里以自己肤浅的撸线姿势,跟大家探讨一下关于高频/高速信号的走线拐角角度问题。我们从锐角到直角、钝角、圆弧一直到任意角度走线,看看各种走线拐角角度的优缺点。

PCB 能不能以锐角走线?

PCB能不能以锐角走线,答案是否定的,先不管以锐角走线会不会对高速信号传输线造成负面影响,单从PCB DFM方面,就应该

避免出现锐角走线

的情形。

因为在PCB导线相交形成锐角处,会造成一种叫酸角“acid traps”的问题,啥?酸豆角?好吧,挺喜欢酸豆角拌面,但是这里的pcb上的酸角却是个令人讨厌的东西。在pcb制板过程中,在pcb线路蚀刻环节,在“acid traps”处

会造成pcb线路腐蚀过度,带来pcb线路虚断的问题

。

虽然,我们可以借助CAM 350 进行DFF Audit自动检测出“acid traps”潜在问题,避免在PCB在制造产生时产生加工瓶颈,如果pcb板厂工艺人员检测到有酸角(acid trap)存在,他们将简单地贴一块铜到这个缝隙中。

很多板厂的工程人员他们其实并不懂layout的,他们只是从PCB工程加工的角度进行了修复酸角(acid trap)的问题,但这种修复会不会带来进一步的信号完整性问题便不得而知了,所以我们在layout是就应该从源头去尽量避免产生酸角(acid trap)。

怎样避免拉线时出现锐角,造成acid trap DFM 问题?现代的EDA设计软件(如Cadence Allegro、Altium Designer等)都带有了完善的Layout走线选项,我们在layout走线是,灵活运用这些辅助选项,可以极大的避免我们在layout时产生产生“acid trap”现象

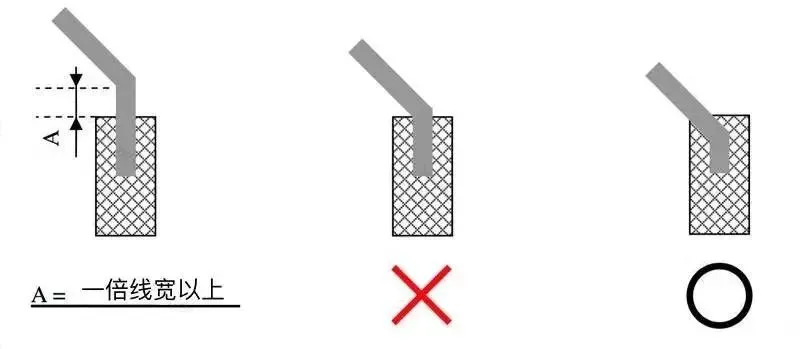

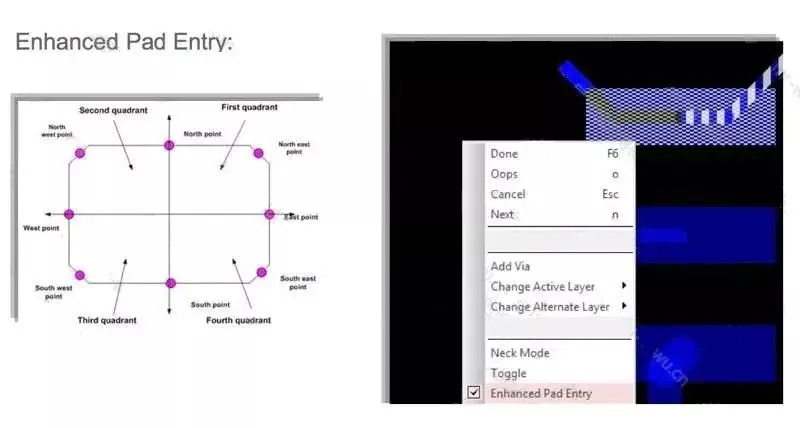

焊盘的出线角度设置 避免导线与焊盘形成锐角角度的夹角。

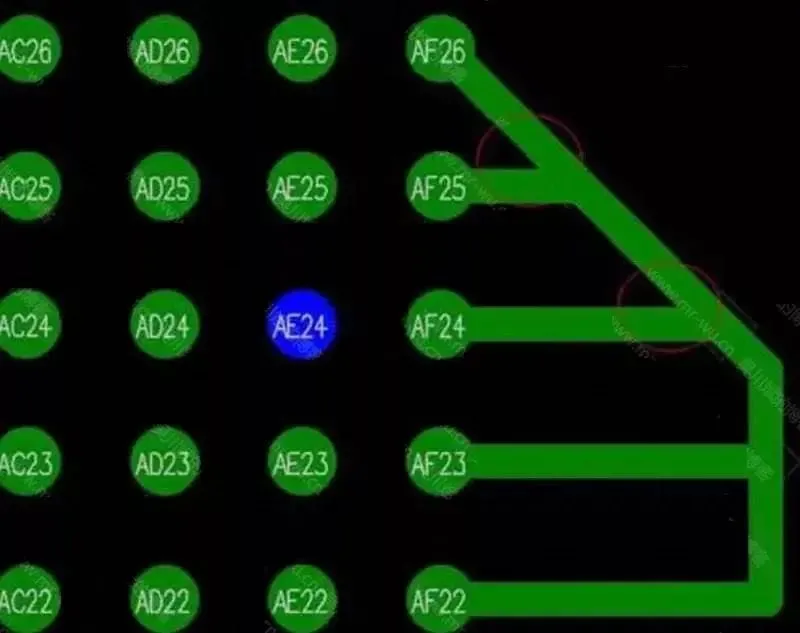

利用 Cadence Allegro 的 Enhanced Pad Entry 功能能够让我们在layout时尽可能的避免导线与焊盘在出线时形成夹角,避免造成“acid traps”DFM问题。

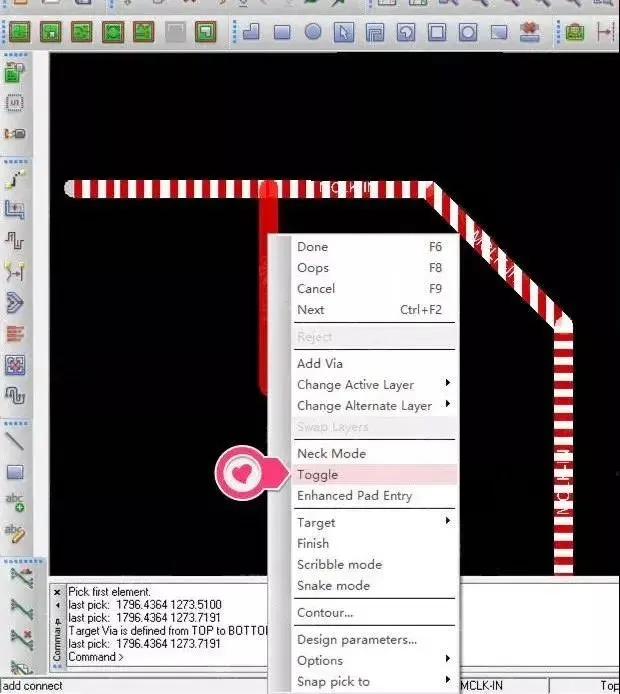

避免两条导线交叉形成锐角夹角。

灵活应用 Cadence Allegro 布线时切换 ” toggle “ 选项,可以避免导线拉出T型分支时形成锐角夹角,避免造成“acid traps”DFM问题。

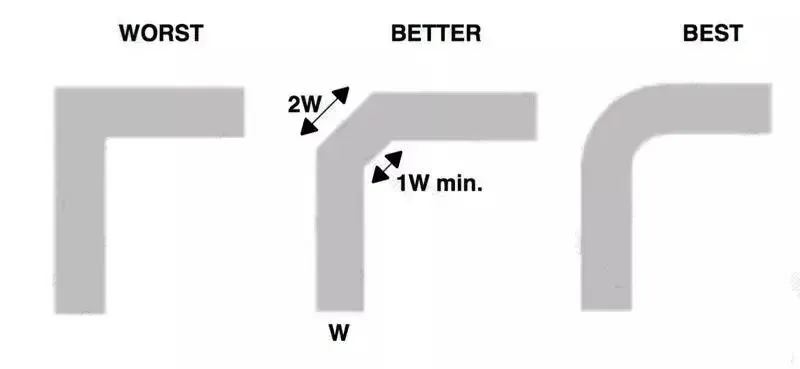

pcb layout能不能以90°走线

高频高速信号传输线应避免以90°的拐角走线,是各种PCB Design Guide中极力要求的,因为高频高速信号传输线需要保持特性阻抗一致,而采用90°拐角走线,在传输线拐角处,会改变线宽,90°拐角处线宽约为正常线宽的 1.414倍,由于线宽改变了,就会造成信号的反射,同时,拐角处的额外寄生电容也会对信号的传输造成时延影响。

当然,当信号沿着均匀互连线传播时,不会产生反射和传输信号的失真,如果均匀互连线上有一个90°拐角

本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。