【导读】当存储三巨头(SK海力士、三星、美光科技)围绕HBM进行升级、扩产的那一刻,意味着蛰伏十年之久、发展至第六代的HBM终于甩去“成本高昂”的束缚,以强悍性能步入存储市场,搅动风云:SK海力士市值突破千亿美元、台积电CoWoS先进封装产能告急、DRAM投片量面临挤压……

存储器件王位“易储”,HBM新君登基。

2023年年中以来,生成式人工智能浪潮叠加产业周期变化,半导体细分产品纷纷打起“翻身仗”。受算力驱动,HBM存储器优势凸显,在AI时代迅速击落GDDR、LPDDR在内的竞争对手,价格狂飙、需求暴增:美光 CEO Sanjay Mehrotra 在2023年年底的财报会议上透露,其2024年的HBM产能预计已全部售罄;SK海力士副总裁 Kim Ki-tae 表示,虽然2024年刚开始,但旗下的HBM已全部售罄。

当存储三巨头(SK海力士、三星、美光科技)围绕HBM进行升级、扩产的那一刻,意味着蛰伏十年之久、发展至第六代的HBM终于甩去“成本高昂”的束缚,以强悍性能步入存储市场,搅动风云:SK海力士市值突破千亿美元、台积电CoWoS先进封装产能告急、DRAM投片量面临挤压……

但必须警惕的是,若只将HBM视作存储领域的一项新兴技术而在战术上亦步亦趋,若只瞄准ChatGPT、Sora等生成式人工智能而忽视背后痛点,是要犯战略错误的。我国半导体从业者需清晰认识到,倘若HBM在内的存储领域受到长期遏制,我国相关产业发展将继先进制程、GPU后,再失先手。正如电子科技大学长三角研究院(湖州)集成电路与系统研究中心副主任黄乐天所说:“就好像一把枪,子弹供应跟不上,射速再快也没用。无法解决HBM问题,我国算力就难以提升,人工智能在内的诸多产业发展就将受限。”

HBM,一场无声的暗战。

“带宽之王”狂飙,HBM无敌手

狂飙的HBM究竟有何魔力?HBM(High Bandwidth Memory ,高频宽存储器)属于DRAM(动态随机存取存储器)中的一个类别,具有高带宽、大容量、低延迟的DDR DRAM组合阵列。

AI时代,算力可以轻松破T(TOPS,每秒万亿次运算),但存储器带宽破T(TB/s,每秒万亿字节带宽)则异常艰难。在需要高算力又需要大数据的应用场景下,存储数据吞吐能力的不足被无限放大,出现所谓的“存储墙”。

图源:Rambus

想要增加带宽,最简单粗暴的方法是增加数据传输线路的数量。当前,HBM由多达1024个数据引脚组成,其内部数据传输路径随着每代产品的发展而显著增长——以SK海力士推出的HBM3E为例,其作为HBM3的扩展(Extended)版本,最高每秒可以处理1.15TB数据;三星的HBM3E“Shinebolt”经初步测试,最大数据传输速度预计达1.228TB/s。鉴于如此强大的带宽性能,市面上大部分存储器产品都难以在该领域击败HBM,唯一的胜出者只能是下一代HBM。

HBM技术自2013年在半导体市场崭露头角以来,已扩展至第一代(HBM)、第二代(HBM2)、第三代(HBM2E),目前正步入第四代(HBM3)、第五代(HBM3E),而第六代(HBM4)也已蓄势待发。

业内判断,HBM作为今后AI时代的必备材料,虽然在内存市场中比例还不大,但盈利能力是其他DRAM的5~10倍。日前,市场调研机构Yole Group发布的数据进一步印证了这一点。Yole预计,今年HBM芯片平均售价是传统DRAM内存芯片的5倍。而考虑到扩产难度,HBM价格预计在相当长一段时间内将保持高位。

鉴于HBM目前无可撼动的市场地位,以及紧张的产能和昂贵的价格,业界是否可以通过牺牲某项性能而另寻方案,譬如使用潜在替代者GDDR、LPDDR?事实上,英伟达较早期的GTX 1080、GTX 2080Ti、GTX 3090也的确采用了GDDR技术。

一位国内芯片企业负责人接受集微网采访时指出,HBM紧缺的产能令其价格一直维持在高位,但随着大模型训练成熟,逐渐进入大规模推理部署阶段,将不得不面对性价比的问题。推理场景中,算力成本至关重要,事实上目前各个大模型厂商也均在探索更高性价比的推理方案。譬如使用GDDR或LPDDR等方案获得更高的性价比,英伟达及国内厂家的推理板卡也不同程度上使用GDDR方案作为替代。

“GDDR本身存在颗粒容量不足的顾虑,在模型参数规模日渐增长的趋势下,如果单卡或者单节点无法提供足够的显存容量,反而会降低单卡的计算效率。但随着GDDR7(其更加兼顾AI场景对带宽和颗粒容量密度的需求)逐步商业化,预计HBM价格也将伴随产能释放而逐步下降,未来在过渡期内还将是多方案共存的状态。”该人士表示。

HBM走俏,CoWoS吃紧

HBM的大火正快速推高市场规模以及预期。市场调查机构Gartner预测,2022~2027年,全球HBM市场规模将从11亿美元增至52亿美元,复合年均增长率(CAGR)为36.3%。高盛甚至给出了翻倍的预期,预计市场规模将在2022年(23亿美元)到2026年(230亿美元)前增长10倍(CAGR77%)。

在催动先进封装的同时,HBM的产能却显得捉襟见肘。

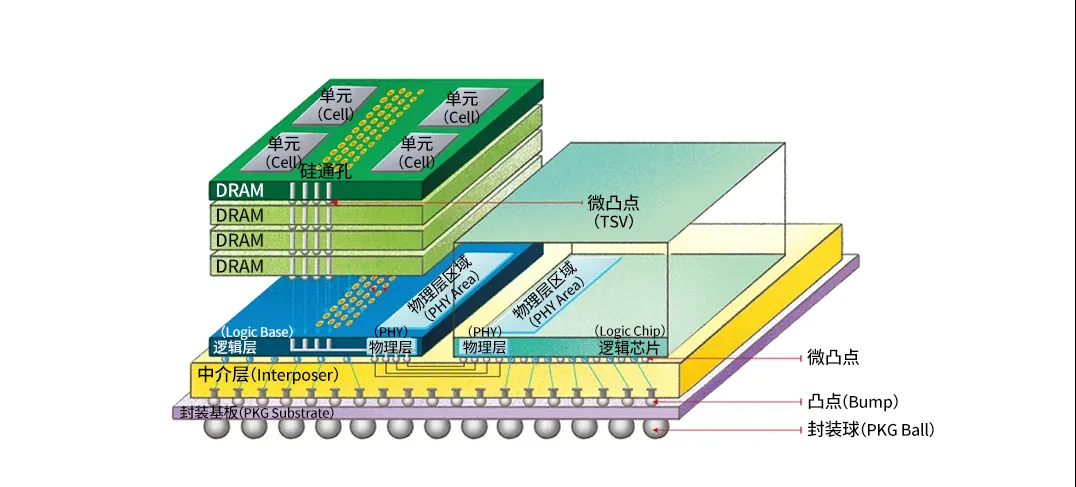

具体地看,HBM由多个DRAM堆叠而成,利用TSV(硅通孔)和微凸块(Microbump)将裸片相连接,多层DRAMdie再与最下层的Basedie连接,然后通过凸块(Bump)与硅中阶层(interposer)互联。HBM与GPU、CPU或ASIC共同铺设在硅中阶层上,再通过CoWoS等2.5D封装工艺相互连接,硅中介层通过CuBump连接至封装基板上,最后封装基板再通过锡球与下方PCB基板相连。

图片:使用HBM的2.5D封装

由此,台积电的CoWoS技术成为目前HBM与CPU/GPU处理器集成的理想方案。HBM高焊盘数和短迹线长度要求需要2.5D先进封装技术,目前几乎所有的HBM系统都封装在CoWoS上,而高端AI服务器也基本使用HBM。这样看起来,几乎所有领先的数据中心GPU都是台积电封装在CoWos上的。黄仁勋在NVIDIA GTC 2024大会期间更是直白喊话,英伟达今年对CoWos的需求非常大。

产业人士指出,CoWoS封装所需中介层材料,因高精度设备不足和关键制程复杂,中介层材料供不应求,牵动CoWoS封装排程及AI芯片出货。

2022年以来,ChatGPT为代表的人工智能带动AI芯片抢购潮,英伟达、AMD为代表的国际大厂纷纷下单,并均采用台积电CoWoS先进封装。大厂“分食”之下,CoWoS产能吃紧。

台积电总裁魏哲家在1月的法说会上称,计划今年将CoWoS先进封装产能增加一倍,并计划在2024年进一步扩充。相关数据显示,去年12月台积电CoWoS月产能已经增至1.4万~1.5万片,预估到今年第四季度,CoWoS月产能将大幅扩充至3.3万~3.5万片,这与魏哲家“产能增加一倍”的说法基本吻合。而最新消息,台积电将在嘉义科学园区设两座CoWoS先进封装厂,首厂预计5月动工,2028年量产。

良率低、散热难,HBM“妥协”

市场调研机构集邦预估,2024年底HBM产值占整体DRAM比重有望攀至20.1%的水平。集邦科技资深研究副总经理吴雅婷表示,在相同制程及容量下,HBM颗粒尺寸较DDR5大35%~45%;良率(包含TSV封装良率),则比起DDR5低约20%~30%;生产周期(包含TSV)较DDR5多1.5~2个月不等。

HBM在市场上“攻城略地”的同时,也面临良率低、散热难等方面问题。

首先是低良率遏制产能。HBM制造过程中,垂直堆叠多个DRAM,并通过 TSV将它们连接起来,由高层向下打孔,通过整个硅片做信号通道;一般技术是信号引脚从侧面左右两边拉下来,而HBM是从中间直接打孔,在极小的裸片上打1000多个孔,并涉及多层;封装过程中,由于线路多且距离近,封装时的干扰、散热等问题均有可能影响线路。这意味着,上述任何阶段的失败都可能导致一枚芯片的废弃。此前有传闻称三星HBM3芯片生产良率仅10%~20%,三星予以坚决反驳,称“这不是真的”。

其次是散热之困。“85℃左右它开始忘记东西,125℃左右则完全心不在焉,”这是业界对DRAM在热量面前尴尬表现的调侃。黄乐天认为,这种说法并不是很客观。存储器相对于处理器等逻辑电路,无论从峰值功耗还是功率密度而言都不算高,之所以存在散热问题,是由于3D-IC堆叠造成的。无论是哪种芯片,只要使用3D堆叠的方式就不可避免有热量聚集,如同多条电热毯堆在一起,热量自然无法散发。

“事实上,散热问题是影响3DIC商用化的主要问题。3DIC早在20年前就被提出,但由于解决不好散热,只能在某些可以不计成本加入微流道能强力散热机制的场景中应用。HBM可视作在2D和3D之间寻求妥协,采用存储器件3D、逻辑器件2D的方式,尽量避免热量集中。”黄乐天告诉集微网。

存储大厂起干戈,走向技术分野

2013年,SK海力士与AMD合作开发世界上的首个HBM,率先“挥师入关”。有数据显示,2023年SK海力士市占率预计为53%,三星市占率38%、美光科技市占率9%——令人不禁感慨,AI的风口还是吹到了韩国。

进入HBM3E时代后,尽管有市场份额的差别,但三大存储厂鼎足而立的格局并未打破,SK海力士、三星和美光科技的技术路线也不尽相同。

图源:SK中国

2023年8月,SK海力士宣布开发HBM3E。仅7个月后,SK海力士即宣布率先成功量产HBM3E,并将在3月末开始向客户供货。其表示,该产品在速度方面,最高每秒可以处理1.18TB(太字节)的数据,其相当于在1秒内可处理230部全高清(FHD)级电影。

据悉,SK海力士在新产品上采用Advanced MR-MUF最新技术,散热性能与前一代相比提升10%。(MR-MUF:将半导体芯片堆叠后,为保护芯片和芯片之间的电路,在其空间中注入液体形态的保护材料,并进行固化的封装工艺技术。与每堆叠一个芯片时铺上薄膜型材料的方式相较,工艺效率更高,散热方面也更加有效。)

图源:三星

2月27日,三星电子宣布成功发布其首款12层堆叠HBM3E DRAM——HBM3E 12H,这是其目前为止容量最大的HBM产品。从性能指标上看,HBM3E 12H支持全天候最高带宽达1280GB/s(约1.25TB/s),产品容量也达到36GB。相比三星8层堆叠的HBM3 8H,HBM3E 12H在带宽和容量上大幅提升超50%。

公开资料显示,HBM3E 12H采用先进的热压非导电薄膜(TC NCF)技术,使得12层和8层堆叠产品的高度保持一致。三星一直在努力降低其非导电薄膜(NCF)材料的厚度,并实现芯片间的间隙最小化至7微米(µm),同时消除层与层之间的空隙。值得一提的是,三星非导电薄膜技术曾引起外界争议,认为这是导致其良率不高的主要原因。

图源:美光科技

美光科技作为HBM领域“后来者”,已于3月宣布开始量产其HBM3E高带宽内存解决方案。英伟达 H200 Tensor Core GPU 将采用其8层堆叠的24GB容量HBM3E内存,并在第二季度开始出货。其HBM3E 引脚速率超9.2Gb/s,提供超1.2TB/s 的内存带宽。

技术路径上,美光科技利用其1β(1-beta)技术、先进的硅通孔(TSV)和其他实现差异化封装解决方案的创新技术开发出业界领先的 HBM3E 设计。

存储三大厂厮杀激烈、各祭法宝的另一面,是国内存储行业在企业体量、技术实力等方面均有不足,围绕HBM研发工作较为困难的现实,但诸多信号显示它们并未将该市场拱手相让。日前,武汉新芯发布《高带宽存储芯粒先进封装技术研发和产线建设》招标项目,这一举动显示其对HBM市场的看重。

黄乐天认为,HBM技术的攻克尽管困难,但依然要着手准备。中美芯片竞争经历数个回合的拉扯,已经发生根本性变化,相较于数年前的乱打一气,美国对我国芯片产业正形成定点遏制的倾向。其遏制的焦点在于阻止我国高端芯片尤其是大算力芯片的研制和生产,通过阻止我国算力提升来拖慢人工智能等数字产业的发展,存储带宽受限将直接阻碍芯片乃至整个计算系统算力提升。

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理。

推荐阅读: