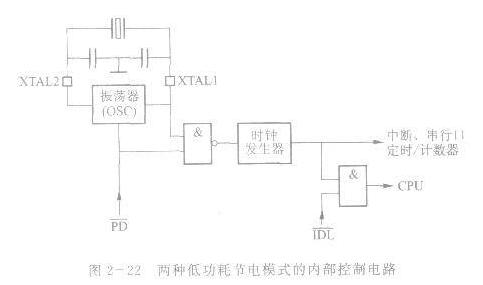

AT89S51有两种低功耗节电工作模式:空闲模式(Idle Mode)和掉电保持模式(PowerDown Mode),其目的是尽可能低降低系统功耗。在掉电保持模式下,VCC可由后备电源供电。图2-22为两种低功耗节电模式的内部控制电路。

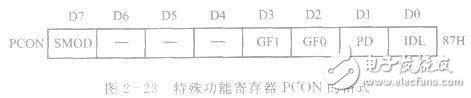

AT89S51的两种低功耗节电模式可通过指令对特殊功能寄存器PCON的位IDL和位PD的设置来实现。特殊功能寄存器PCON的格式如图2-23所示,字节地址为87H

PCON寄存器各位的定义如下:

SMOD:串行通信的波特率选择位

一:保留位,未定义。

GF1、GFO:通用标志位,供用户在程序设计时使用,两个标志位用户应充分利用。

PD:掉电保持模式控制位,若PD=1,则进入掉电保持模式。

IDL:空闲模式控制位,若IDL=1,则进入空闲运行模式。

空闲模式

1.空闲模式的进入

如果用指令把寄存器PCON中的IDL位置1,由图2-22可见,则把通往CPU的时钟信号关断,单片机便进入空闲模式。这时虽然振荡器仍然运行,但是CPU进入空闲状态。此时,所有外围电路(中断系统、串行口和定时器)仍继续工作,SP、PC、PSW、A、PO~P3端口等所有其他寄存器,以及内部RAM和SFR中的内容均保持进入空闲模式前的状态。

2.空闲模式的退出

系统进入空闲模式后有两种方法可退出,一种是响应中断方式,另一种是硬件复位方式。

在空闲模式下,若任何一个允许的中断请求被响应时,IDL位被片内硬件自动清0,从而退出空闲模式。当执行完中断服务程序返回时,将从设置空闲模式指令的下一条指令(断点处)开始继续执行程序。

另一种退出空闲模式的是硬件复位。当使用硬件复位退出空闲模式时,在复位逻辑电路发挥控制作用前,有长达两个机器周期的时间,单片机要从断点处(IDL位置1指令的下一条指令处)继续执行程序。在这期间,片内硬件阻止CPU对片内RAM的访问,但不阻止对外部端口(或外部RAM)的访问。为了避免在硬件复位退出空闲模式时出现对端口(或外部RAM)的不希望的写入,系统在进入空闲模式时,紧随IDL位置1的指令后面的不应是写端口(或外部RAM)的指令。

掉电运行模式

1.掉电模式的进入用指令把PCON寄存器的PD位置l,单片机便进入掉电模式。由图2-22可见,在掉电模式下,进入时钟振荡器的信号被封锁,振荡器停止工作。由于没有了时钟信号,内部的所有功能部件均停止工作,但片内的RAM和SFR原来的内容都被保留,有关端口的输出状态值都保存在对应的特殊功能寄存器中。

2.掉电模式的退出掉电模式的退出有两种方法:硬件复位和外部中断。硬件复位时要重新初始化SFR,但不改变片内RAM的内容。当Vcc恢复到正常工作水平时,只要硬件复位信号维持lOms,便可使单片机退出掉电运行模式。

掉电和空闲模式下的WDT

掉电模式下振荡器停止,也就意味着WDT停止计数。用户在掉电模式下不需要操作WDT。

掉电模式的退出有两种方法:硬件复位和外部中断。当用硬件复位退出掉电模式时,对WDT的操作与正常情况一样。中断方式退出掉电模式时,应使中断输入保持足够长时间的低电平,以使振荡器达到稳定。当中断变为高电平之后,该中断被执行,在中断服务程序中复位寄存器WDTRST。在外部中断引脚保持低电平时,为防止WDT溢出复位,在系统进入掉电模式之前先对寄存器WDTRST复位。

在进入空闲模式之前,应先设置特殊功能寄存器AUXR中的WDIDLE位,以确认WDT是否继续计数。当WDIDLE=O时,空闲模式下的WDT保持继续计数。为防止复位单片机,用户可设计一定时器。该定时器使器件定时退出空闲模式,然后复位WDTRST,再重新进入空闲模式。

当WDIDLE=1时,WDT在空闲模式下暂停计数,退出空闲模式后,方可恢复计数。