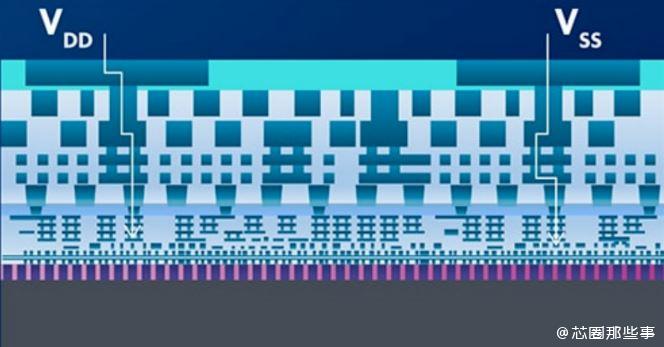

【导读】芯片供电网络(Power Delivery Network, PDN)的设计目标是以最高效率为芯片上的主动元件提供所需的电源(VDD)与参考电压(VSS)。一直以来,业界都是利用后段制程(BEOL),在晶圆正面布线,透过这些低电阻的导线来供应电力给芯片。但也因为如此,芯片内的供电网路与讯号网络(即芯片内的讯号线)必须共享相同的元件空间。

随着制程节点往前推进,把电源网络视作在芯片正面,遇到越来越多挑战,使得业界开始探索把供电网络转移到背面的可能性,从而让背面供电(Backside PDN)成为热门的技术议题。本文将先从传统PDN所遇到的挑战谈起,进一步探讨背面供电技术的优势,以及这项技术未来的发展重点。

传统PDN布线面临诸多挑战

为了将电力从封装传输至芯片中的晶体管,电子必须经由金属导线和通孔,穿越15~20层BEOL堆叠。然而,越接近晶体管,线宽和通孔就越窄,电阻值也因而上升,这使得电子在向下传输的过程中,会出现IR压降现象,导致电力损失产生。

除了电力损失之外,PDN占用的空间也是一个问题。当电子快到达晶体管,例如抵达标准元件层时,电子会进入由BEOL制程所制造Mint金属层,进而分配给负责提供工作电压与接地电压的电源轨。然后,这些电源轨会通过互联网络,连接到每一个晶体管的源极与漏极,完成供电任务。但这些电源轨会占用元件周围及标准单元(Standard Cell)之间的空间。

然而,随着制程技术世代交替,传统后段制程的组件架构难以跟上晶体管的微缩速度。如今,芯片内部的电源线路,在布线复杂的后段制程上,往往占据了至少20%的绕线资源,如何解决讯号网络跟供电网络之间的资源排挤问题,变成芯片设计者所面临的主要挑战之一。此外,电源线和接地线在标准单元设计上占了很大空间,使得组件很难进一步微缩。就系统设计而言,因为功率密度和IR压降急剧增加,从稳压器到晶体管的功率损失就很难控制在10%以下,带给工程师严峻挑战。

背面供电,互连制造

Imec 的 BPD 方法使用细间距 nanoTSV(200 纳米间距,320 纳米深)从metal-0向下延伸并落在具有严格覆盖控制的掩埋电源轨上。他们使用 finFET 测试设备实现了这一点,方法是将正面粘合到载体晶圆上,减薄晶圆,然后蚀刻和填充 TSV。通过结合背面去耦电容器(metal-insulator-metal capacitor),IR 压降进一步降低。该设计可扩展到 2nm 节点之外,因为 TSV 不占用标准单元区域。

BPD 可以减少标准单元(standard cells)中的轨道数。除了 imec 的方法外,还有另外两种背面功率传输方案,工艺复杂度不断提高。这三者都面临将晶圆减薄至 ̴10µm 的挑战。他们需要将背面与正面连接对齐,并且担心串联电阻——尤其是在堆叠芯片的情况下。但是,一旦背面配电网络建立起来,芯片制造商现在就有了另一个自由度,可以在背面整合无源或有源器件。

也许互连密度最引人注目的变化与混合键合有关。事实上,混合键合正被用于实现背面配电。混合键合涉及铜连接和周围电介质的键合,每单位面积的连接数比铜微凸块多 1,000 倍。

晶圆到晶圆(W2W:Wafer-to-wafer)混合键合比芯片到晶圆(D2W:die-to-wafer)混合键合更成熟。EV Group 首席技术官 Thomas Uhrmann 表示:“芯片到晶圆的对齐要复杂得多,因为您要管理芯片四个角的位置,而不是两个晶圆的整体位置。” 晶圆对晶圆键合最常用于将像素阵列键合到相机图像传感器中的底层芯片。“混合键合在 2010 年改变了图像传感器的游戏规则。长江存储是第一家做混合键合的NAND供应商。事实上,今天大多数进行混合键合的 NAND 闪存公司首先在图像传感器中有过混合键合的经验,”他补充道。

混合键合的关键工艺步骤包括电镀 (ECD:electroplating)、CMP、等离子活化(plasma activation)、对准、键合、分割和退火。尽管这些工具已经成熟,例如,用于制造双镶嵌铜互连和倒装芯片键合,但需要完善这些工艺以满足混合键合的需求。其中包括 <100 纳米的对准精度、芯片到晶圆键合和分离工具的清洁度达到新水平、具有 0.5 纳米 RMS 粗糙度的出色 CMP 平面度以及用于实现最佳键合的电镀。

虽然晶圆厂正在将几乎完成的器件相互键合,但芯片制造商已经期待在晶体管级别使用混合键合,例如,允许在硅上组合 GaN。

“当你开始达到使用混合键合来组合晶体管的地步时,这会变得非常有趣,因为现在你所处的间距比我们正在寻找的封装要紧密得多,”行业分析师Dean Freeman 说。“英特尔和其他公司已经完成了将 GaN 与硅相结合的工作,这非常有趣。这是 RF 在通信设备中的一个很好的机会,因为现在,您已经将逻辑与 GaN 的速度相结合——或者最终是碳化硅,甚至可能是另一种材料——将其通信方面的工作纳入太赫兹波长范围,然后开始将毫米波从我们目前的 5G 技术所获得的水中吹出来。”

走向背面供电的代工巨头

即便当前“背后供电”技术还未成熟,但在技术优势的吸引之下,英特尔、台积电等晶圆制造巨头自然不会错过,纷纷开始押注布局。

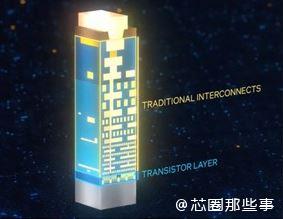

英特尔在去年7月的Intel Accelerated上公告了两项创新技术,一个是RibbonFET,其实就是在文章开头提到的GAA晶体管,另外一个就是背面供电技术,英特尔将其命名为PowerVia。

据了解,英特尔的PowerVia技术是业界首创的解决方案。英特尔公司逻辑技术开发部高级副总裁兼联席总经理Sanjay Natarajan 博士表示,PowerVia可以解决困扰硅架构数十年的互连瓶颈问题。

在Sanjay Natarajan 博士看来,使用 PowerVia,可以实现信号线和电源线的分离。而信号和电源则会使用英特尔的另一项创新技术连接到晶体管层,即纳米硅通孔 (TSV),这类TSV 比当今最先进的 IC 封装中使用的 TSV 小 500 倍。

英特尔 RTL 设计工程师 David Kanter 指出,“我们相信 PowerVia 具有重新调整行业的潜力,并且与 2001 年从铝到铜的转变一样具有里程碑意义”。这句话足以证明PowerVia技术的重要性。

目前,关于PowerVia技术的应用,关键的转折点或许将从2023年开始的A系列工艺节点出现。英特尔方面表示,其20A工艺(相当于2nm),从2024年中期开始,将使用RibbonFET和PowerVia这两种突破性技术,而这两项技术也将共同确保英特尔继续成为全球领先的芯片供应商。

从这方面来看,PowerVia技术或许已经成为了英特尔在晶圆代工领域逆风翻盘的“关键武器”之一。

再看台积电方面,在6月初首次推出其N2(2 纳米级)工艺技术时,台积电透露了其2nm节点的两大显著优势,同英特尔一样,也是纳米片栅环 (GAA) 晶体管和背面电源轨。

不过与英特尔不同的是,台积电并不打算在其 N2 工艺技术的第一代中同时使用 GAA 晶体管和背面电源轨,第一代 N2 将仅采用GAA,而背面供电技术则会在更高版本的N2节点中实现。

虽然台积电方面并没有过多地说明不将背面供电应用在其初始 N2 节点的具体原因,但是其也曾透露,由于背面供电技术最终将增加额外的工艺步骤,在首次尝试 GAAFET 时更希望能避免这些额外的步骤。

由此可以看出,台积电对于N2 的的创新还是采取较为谨慎的态度,与N3E 节点相比,台积电第一代N2性能预计提升10% 到 15%,但在相同的速度和复杂性下,功率却下降 25% 到 30% 。

从台积电透露的时间表来看,其第一个N2节点预计将于2024年或2025年推出,与英特尔20A工艺时间相差无几。不过如此谨慎的态度是否影响台积电的发展步伐,而没有背面供电技术的GAA工艺在与英特尔对撞时,又是否会处于劣势地位?

这一切,或许还需要时间给我们答案。

写在最后

虽然“背面供电”与GAA的碰撞能给芯片性能带来怎样的提升我们还未曾知道,不过可以预见的是,在未来,背面供电技术或许会成为通往先进制程不可缺少的必经之路。

来源:贤集网

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理。

推荐阅读: