1.引言

DFSDM 全称为 Digital filter for sigma delta modulators。顾名思义,其作用主要是对外部 Σ∆调制的数字信号进行滤波。STM32L462xx 系列支持最多 4 个外部串行通道,2 个数字滤波器,最大可达到 24bit 的 ADC 分辨率。并且支持 SPI 接口和曼切斯特编码 1-wire接口。

2.问题分析

客户使用 STM32L462xx 的 DFSDM 连接数字麦克风,将麦克风的 PDM 信号转化为 PCM 信号,并采集数据。使用的参数为 16KHz 采样,2M 左右的时钟驱动数字麦克风,能够正常读取麦克风数据。了解到他们所使用的数字麦克风可以使用 768K 时钟驱动,从而达到更低功耗的状态,但是客户无法配置出合适的时钟,即使勉强配置到了768K 附近,通过 DFSDM 采集到的数据也是混乱的,完全无法解析。

了解到基本需求后,我们需要对 DFSDM 的时钟有一定了解。从 RM0394 参考手册中可以找到如下内容:

DFSDM 可以提供一个时钟用于驱动外部 sigma delta 调制器,并且时钟来源可以是DFSDM 时钟或者 Audio 时钟,其中 Audio 时钟就是 SAI1 的时钟。

在处理和时钟相关的配置问题时,强烈建议使用 CubeMX 的时钟配置界面进行配置。我们先来看下客户用于驱动外部数字麦克风的时钟配置。

从图中可以看出,DFSDM 的时钟为 36MHz,来自 PCLK2。SAI1 的时钟约为 34.29MHz来自 PLLSAI1P。

这是关于 DFSDM 输出时钟的代码片段,可以看到使用了 AUDIO 的时钟作为输出,并且使用 17 分频,那么最终驱动数字麦克风的时钟为 34.29/17≈2.02MHz。

再来看看滤波器部分参数的设计:

其中,使用了 4 阶 SINC 滤波,过采样参数为 128,那么 2.02MHz/128≈16KHz。也就是说这种配置参数下,可以接近 16KHz 的采样率来对音频数据采样。

客户想要将麦克风驱动时钟重新配置为 768K,但只考虑修改 Divider 和 Oversampling 参数是配置不出来的。

3.问题解决

我们可以反过来推,要想获得 16KHz 采样率,768KHz 的时钟,首先需要满足以下公式:768K/ Oversampling = 16K, 那么 Oversampling=48。Oversampling 这个参数是比较好确定的,而 768K 来自于 CLK_SAI1/Divider, 这两个参数目前无法确定,其中 CLK_SAI1 又来自于 PLLSAI1P,它由 PLLSAI1_N, PLLSAI1_P 两个系数决定。也就是说要想获得 768K 的时钟,需要把这些参数都配置为合适的值。到这一步,实际上没有直接的公式可以求下去了,只能自己测试并调整,建议可以先将 Divider 定好,然后通过 CLK_SAI1/Divider=768K 就可以求出CLK_SAI1 的值,将这个值手动输入到 Cubemx 的时钟配置界面可以自动求出合适的

PLLSAI1_N, PLLSAI1_P 系数,这样可以大大减少调整时间。如果无法求出合适的值,CubeMX也会进行提示,那么只能重新换 Divider 来测试了。

最终调试下来的值如下图所示:

我选择的 Divider=50,那么可以算出CLK_SAI1=50*768K=38.4MHz,输入到上图界面中可以得到 PLLSAI1_N=12, PLLSAI1_P=5。

至此,已经可以正确得到 768KHz 的时钟驱动麦克风了,但是目前仍然无法获取到准确的音频数据。

由于前面修改了 Oversampling,该参数会影响采样值。在参考手册中可以找到下表:

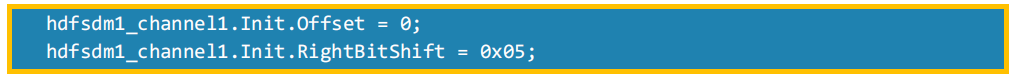

从表中可以看到,之前是 FOSR=128,Sinc4,对应的数值为+/-268435456,但是DFSDM 的数据寄存器只有 24bit,2^23<268435456 的,也就是说需要进行移位,只能以损失精度为代价进行转换。客户代码中有以下配置:

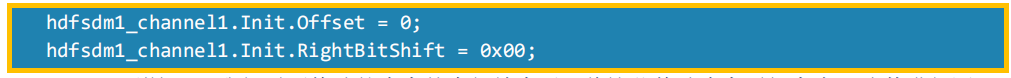

数据需要右移 5 位保存到数据寄存器,那么现在我们的 FOSR 修改为了 48,对应上表可以看到数值是比较小的,不需要移位处理,所以改为:

到这里,我们需要修改的内容就全部结束了。将这些修改内容通知客户,让其进行测试,测试结果也比较满意。

小结

DFSDM 在数字音频应用中比较常见,主要用于将数字麦克风的 PDM 信号转换为PCM 信号,如果没有DFSDM 外设,就只能使用软件库进行转化,效率比较低。当然,也可以用于一些模拟信号的采集,需要外部 Sigma Delta 调制器调制好之后再进行滤波,这样得到的 ADC 精度要比通用的 ADC 精度更高,在要求高精度 ADC 的场合,不失为一种较好的方案。