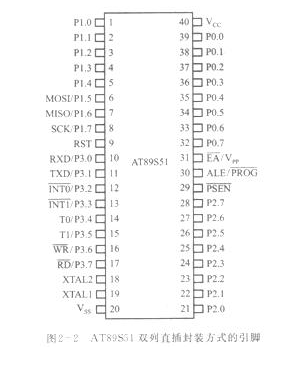

掌握AT89S51单片机,应首先了解AT89S51的引脚,熟悉并牢记各引脚的功能。AT89S51与80C51系列中各种型号芯片的引脚是互相兼容的。目前AT89S51单片机多采用40个引脚的双列直插封装(DIP)方式,如图2-2所示。此外,还有44个引脚的PLCC和TQFP封装方式的芯片。

40个引脚按其功能可分为如下3类:

(1)电源及时钟引脚——VCC、Vss;XTAL1、XTAL2。

(2)控制引脚——PSEN(的反)、ALE/PROG(的反)、EA(的反)/Vpp、RST(即RESET)。

(3)I/0口引脚-PO、Pl、P2、P3,为4个8位I/O口的外部引脚。

下面结合图2-2介绍各引脚的功能。

电源及时钟引脚1.电源引脚电源引脚接入单片机的工作电源。

(1) Vcc(40脚):接+5 V电源。

(2) Vss(20脚):接数字地。

2.时钟引脚(1) XTAL1(19脚):片内振荡器反相放大器和时钟发生器电路的输入端。当使用片内振荡器时,该引脚连接外部石英晶体和微调电容;当采用外接时钟源时,该引脚接外部时钟振荡器的信号。

(2) XTAL2(18脚):片内振荡器反相放大器的输出端。当使用片内振荡器时,该引脚连接外部石英晶体和微调电容;当采用外部时钟源时,该引脚悬空。

控制引脚

此类引脚提供控制信号,有的引脚还具有复用功能。

(1) RST(RESET,9脚):复位信号输入端,高电平有效。在此引脚加上持续时间大于2个机器周期的高电平,就可以使单片机复位。在单片机正常工作时,此引脚应为≤0.5 V的低电平。

当看门狗定时器溢出输出时,该引脚将输出长达96个时钟振荡周期的高电平。

(2) EA(的反)/ Vpp(Enable Address/Voltage Pulse of Programing,31脚):EA(的反)(External AccessEnable)为该引脚的第一功能,即外部程序存储器访问允许控制端。

当EA(的反)引脚接高电平时,在PC值不超出OFFFH(即不超出片内4 KB Flash存储器的地址范围)时,单片机读片内程序存储器(4 KB)中的程序;当PC值超出(即超出片内4 KB Flash存储器地址范围)时,将自动转向读取片外60 KB(1000H~FFFFH)程序存储器空间中的程序。

当EA(的反)引脚为低电平时,只读取外部程序存储器中的内容,读取的地址范围为OOOOH~FFFFH,片内的4 KB Flash程序存储器不起作用。

Vpp为该引脚的第二功能,即在对片内Flash进行编程时,VPP引脚接人编程电压。

(3) ALE/PROG(的反)(Address Latch Enable/PROGramming,30脚):ALE为CPU访问外部程序存储器或外部数据存储器提供一个地址锁存信号,将低8位地址锁存在片外的地址锁存器中。

此外,单片机在正常运行时,ALE端一直有正脉冲信号输出,此频率为时钟振荡器频率fosc的1/6。该正脉冲振荡信号可作外部定时或触发信号使用。但是要注意,每当AT89S51访问外部RAM时(即执行MOVX类指令时),要丢失一个ALE脉冲。

如果需要,可将特殊功能寄存器AUXR(地址为8EH,将在本章后面介绍)的第O位(ALE禁止位)置l,来禁止ALE操作,但在执行访问外部程序存储器或外部数据存储器指令“MOVC”或“MOVX”时,ALE仍然有效。也就是说,ALE的禁止位不影响对外部存储器的访问。

PROG(的反)为该引脚的第二功能,即在对片内Flash存储器编程时,此引脚作为编程脉冲输入端。

(4) PSEN(的反)(Program Strobe ENable,29脚):片外程序存储器的读选通信号,低电平有效。

并行I/O口引脚

(1) PO口:8位,漏极开路的双向I/O口。

当AT89S51扩展外部存储器及I/O接口芯片时,PO口作为地址总线(低8位)及数据总线的分时复用端口。

PO口也可作为通用的I/O口使用,但需加上拉电阻,这时为准双向口。当作为通用的I/O、输入时,应先向端口输出锁存器写入1。PO口可驱动8个LS型TTL负载。

(2) Pl口:8位,准双向I/O口,具有内部上拉电阻。

Pl口是专为用户使用的准双向I/O口。当作为通用的I/O口输入时,应先向端口锁存器写入l。Pl口可驱动4个LS型TTL负载。

MOSI/P1.5、MISO/Pl.6和SCK/PI.7也可用于对片内Flash存储器串行编程和校验,它们分别是串行数据输入、输出和移位脉冲引脚。

(3) P2口:8位,准双向I/O口,具有内部上拉电阻。

当AT89S51扩展外部存储器及I/O口时,P2口作为高8位地址总线用,输出高8位地址。

P2口也可作为普通的I/O口使用。当作为通用的I/O输入时,应先向端口输出锁存器写入l。P2口可驱动4个LS型TTL负载。

(4) P3口:8位,准双向I/O口,具有内部上拉电阻。

P3口可作为通用的I/O口使用。当作为通用的I/O输入时,应先向端口输出锁存器写入l。P3口可驱动4个LS型TTL负载。

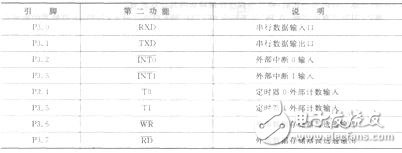

P3口还可提供第二功能。其第二功能定义见表2-1。

表2-1 P3口的第二功能定义

综上所述,PO口作为地址总线(低8位)及数据总线使用时,为双向口;作为通用的I/O口使用时,为准双向口,这时需加上拉电阻。Pl口、P2口、P3口均为准双向口。

要特别注意准双向口与双向口的差别。准双向口仅有两个状态。而PO口作为地址总线(低8位)及数据总线使用时,口线内无上拉电阻,由两个MOS管串接且开漏输出,处于高阻的“悬浮”状态。因此PO口与Pl口、P2口、P3口这三个准双向口相比,又多了一个高阻“悬浮”状态,故PO口为双向三态I/O口。为什么PO口要有高阻“悬浮”态呢?这是由于PO口作为数据总线使用时,多个数据源都挂在数据总线上,当PO口不需要与其他数据源打交道时,需要与数据总线高阻“悬浮”隔离,因此,PO口必须要有高阻的“悬浮”状态,而准双向I/O口无高阻的“悬浮”状态。另外,准双向口作为通用的I/O口输入使用时,一定要向该口先写入1。