来源: 本文由半导体行业观察翻译自semiengineering,作者ED SPERLING,谢谢

摩尔定律在过去52年中一直是“更小,更快,更便宜”的代名词,但越来越多的人认为它只是诸多选择之一,芯片行业开始针对特定的市场需求进行调整。

这并没有使得摩尔定律失去意义。众多行业人士透露,从16 / 14nm冲击7nm的公司数量要多于直接冲击16 / 14nm finFET的公司。但是,这种迁移也需要考虑到:

• 当代工厂利用16 / 14nm finFET进行相同度量时,节点命名在20nm之后就变得无意义。因此,对于10nm或7nm并没有一致的定义。更有价值的数字是各个代工厂的性能和功率的比较。

• 即使摩尔定律最执着的支持者也正在从每两年一个节点逐渐减缓到每三、四年一个节点。 但业内人士表示,由于成本和复杂程度的上升,许多公司计划跳过节点,所以并不是在每个节点都投放生产芯片,而是计划开发测试芯片来保持现有的最新技术,而他们的量产芯片的迁移则会延迟长达八年之久。

• 像苹果和谷歌这样的大型系统公司正在开发芯片,他们的开发违背标准的度量,因为他们是特定于应用程序的。相比之下,大多数节点特定的度量都是基于ASIC(专用集成电路)而不是ASSP(在特殊应用中使用而设计的集成电路)。此外,这些统计数据一般不包括在半导体行业统计数据中,因为系统公司不分享这些数据。

因此,半导体行业真正遵循的摩尔定律不再是简单的计数练习。逻辑器件仍在缩小,但不是连续的或成比例的。而随着高级封装的进一步发展,封装可以任意组合,例如最新的几何工艺搭配上旧节点的IP制成的逻辑芯片。

西门子董事长兼首席执行官Wally Rhines表示:“在过去50年中,提高复杂性的最便宜和最简单的方法是缩小尺寸并增加晶圆直径。但现在,这不是最简单的方法了,而是需要进行一个权衡。我们要为需要的性能做最经济的事情。其中一些将使我们几乎永远都能继续拥有越来越小的芯片尺寸。但是,最经济的折衷可能是更好的系统工程,多芯片封装,以及各种技术的结合,以最节约成本的方式不断提升能力。”

这些变化集中体现了对于半导体设计和制造方面所取得进步的衡量基准的不同看法。ARM的首席执行官Simon Segars说:“从根本上讲,摩尔定律每年都会提供更强的性能和扩展功能。除了让晶体管和栅极小到原子级别尺度以外,还存在许多维度。数代器件只是在缩小尺寸,然后人们开始思考,‘如果我们在这里使用一些不同的材料和材料科学会如何?’这会带来巨大的进步。我们即将看到EUV的引入,这将为缩小晶体管和半导体制造技术注入新的生命。同时,人们正在寻找其他方法来进行计算,如量子计算。这依赖于一套完全不同的技术。然而,成功虽然可能需要10年时间,但是一旦成功便会产生大量新的并行性,这将是又一个影响几代人的摩尔定律。”

光刻

由于双重曝光成为关键金属层(即20nm处的金属1和金属2)的要求,大多数专家认为,器件缩小的主要限制因素是光刻。

幸运的是,芯片制造商已经能够扩展传统的光刻技术。使用各种多重曝光工艺,芯片制造商能够分开掩模和图案。这种方法可以将今天的193nm波长的光刻技术扩展到16nm / 14nm,10nm甚至7nm。

但是在7nm或5nm处,图案复杂性和掩模计数正在成为浸入式和多重曝光的限制因素。28nm器件具有40至50个掩模层。相比之下,14nm / 10nm器件具有60层,预计7nm可以跃升到80到85层。在5nm可以有100层。

为了简化7nm/5nm的工艺流程,芯片制造商一直在等待极紫外(EUV)光刻技术,这是一种13.5nm波长的技术。EUV预计为45nm,但遇到了一些仅仅在最近才刚刚解决的问题。随着光源的增强,产量持续上升,EUV似乎终于接近了商业化生产。

极紫外光刻技术是否接近大批量生产还有待观察。 ASML的EUV服务和产品营销副总裁Hans Meiling表示:“我们的工厂每小时生产100个晶圆,今年晚些时候将提高到每小时125个晶圆。”

同时,根据11个月平均数,正常运行时间已经提高到80%以上。Meiling表示是90%+,这与浸入式光刻相当。事实上,我们已经达到了这一点,但并不令人震惊。这个项目看起来就像科幻小说中的内容。

这里有一些工程技巧。首先是从小液滴中得到稳定的锡液滴。这些小液滴被激光击中。然后,激光再次发射,这次是主脉冲。主激光脉冲击中薄饼状锡液滴并使其蒸发,转而将它变成等离子体。等离子体发射13.5nm波长的EUV。

“每秒有5万个液滴,”Meiling说,“这是一个受控的过程。它们以每秒数百米的速度流进去。然后我们将CO²激光射入每个液滴。因此,CO²激光器的速率与液滴发生器相同。每个液滴都变成了薄饼。由于CO²的作用,它膨胀成为200-400微米的雾滴,而不再是固体。第一个脉冲使它成为了薄饼。”

图1:跟随反弹光。(来源:ASML)

更令人震惊的是,这是有效的。有越来越多的论文可以证明这一点。

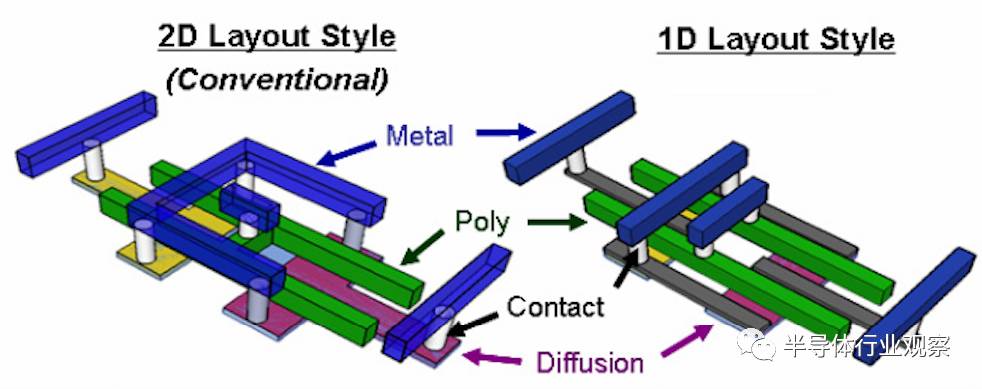

但是,尽管在光刻方面有这些改进,但在许多方面,缩小的极限变得越来越明显。每个新节点的布局灵活性都在降低。英特尔能够在45nm转移到1D图形,主要是因为CPU不需要与SoC拥有相同的灵活性水平,它的结构更加规则。对于SoC或ASSP,限制更为明显。

Lam Research首席技术官Yang Pan,说:“我们认为,使用EUV工艺,二维图案会变得太困难。首先,EUV仍然有掩模缺陷问题。我们必须修复这些缺陷,但我们肯定无法一遍又一遍地修复。其次,如果要为EUV获得良好的刻线边缘粗糙度特性,则需要大量能源。目前这是不可能的。所以EUV会走进1D空间。我们此时看不到2D。”

图2:1D vs 2D (来源:Multibeam公司)

EUV工艺还存在很多限制。Applied Materials蚀刻业务部副总裁兼总经理Raman Achutharaman说:“主要的是EUV的解决方案。它没有解决定位误差的要求。其二,随着较长的EUV的推出,甚至EUV也需要多重曝光。对于切割和通孔,可以使用EUV。但是对于线和空间,你只能使用基于空间的方法。”

不过,EUV工艺也有一些进展,部分原因是多家公司的大量投资,以及人们认识到EUV即将具备生产价值。直到去年,薄膜也是一个问题。没有人愿意负责开发薄膜,所以ASML开发了自己的薄膜。EUV进入线和空间的生产需要时间,而不仅仅是掩模切割。但是,这些方面现在得到了充分的进步,EUV技术也将会获得一些动力。

这一切何时会发生取决于许多因素。但从纯光刻的观点来看,ASML表示,EUV一直到1.5nm都有一条清晰的路径,通过更高的数值孔径技术和变形透镜,可以将激光延伸到更大的表面上,就像一台用于显示宽屏电影的老式CinemaScope投影机。

ASML高级首席架构师Jan van Schoot表示:“在芯片方面,挑战基本上是刻线边缘粗糙度和光子发射噪声。我们必须努力在晶圆上获得足够的能量。本质上,应对光子发射噪声有两种方法。你可以用暴力方式,应用更多的光子得到更好的统计数据。还可以尝试提高应用于芯片的图像对比度,这是更优雅的方法。”

其他后端的变化

EUV显着减少了构建芯片所需的掩模层的数量,加快了制作硅片的时间。业内人士表示,现在需要大概60到90天的时间才能从代工厂获得芯片,这比先前的节点多花了大概45到60天。利用EUV减少掩模数量会有效解决这一问题。

但减少掩模只是一个因素。正如越来越多的设计规则所证明的那样,工艺变化仍然是一个主要问题。Cadence产品管理总监Christen Decoin说:“设计规则越来越多,完成设计规则所需的操作数量呈指数级别增长。DRC检验无法再通宵运行了,这总共需要四天时间。如果使用EUV,着色规则较少,但是实现它尚需时日,我们仍然需要双重曝光,虽然复杂度不会像7nm时那么糟糕。”

每个新节点的工艺过程都会增加。规格从不体现为确切的数字,所以一个掩模与另一个不同。虽然这通常在设计工具中处理,但该方法是增加时间裕度。我们需要在低产出和高性能之间权衡。 这是FD-SOI并未广泛宣传的卖点之一,部分原因在于提供FD-SOI的代工厂必须与先进的节点技术共舞。

FD-SOI只是其中的一个选择。缩小正变得越来越困难,而且它也变得越来越贵。因此,一些芯片制造商正在考虑扩展技术投资的一些替代方案。所以有些厂商回避了10nm,直接跳跃到7nm。而在7nm处,他们可以迁移到5nm,或使用不同的架构继续保持在7nm。

ASM国际首席技术官Ivo Raaijmakers说:“还有很多方法可以用于器件的架构。您可以用5nm的纳米线改变栅极长度。但是对于晶圆厂而言则会越来越昂贵,研发费用越来越高,而需要的其他技术也越来越多。”

Raaijmakers表示,现在的权衡是,在现有节点上更进一步,或直接跳到未来的节点,或是让下一个节点拥有足够多次的迭代。“对于密度的巨大挑战就像控制诸如寄生电容和电阻这类寄生效应。”

封装:摩尔定律的一部分

封装并没有被忽视,这就是为什么近日在封装方面有很多活动的原因。先进封装增加了一种全新看待的摩尔定律视角。相比于存储器、处理器、I/O这些需要在同一工艺节点处共同开发的元素,封装允许不同节点上的各个部件的混合。

这为芯片制造商开辟了新的自由度。在过去,我们很担心多大的封装适合一片硅片。这导致了一大堆问题,主要涉及生产能力和热量。电阻和电容对于信号通过越来越细的导线传播速度的影响。电阻也产生热量,这可能导致信号完整性问题、电迁移,并且可能导致质量随时间的退化。 此外,片上资源存在线路拥塞和竞争。而在45nm以下,模拟IP不再缩小,这就是为什么模拟IP厂商在其产品中增加了更多的数字电路。

扇出型(fan-out)、系统级封装,以及2.5D配置彻底改变了这个等式。简化这些工艺的流程正在开发,但过去几年来,人们对于这一方法的兴趣也在迅速上升,特别是在过去12个月中,苹果公司在iPhone 7处理器采用了台积电的整合扇出(InFO),以及来自思科和华为等公司的高端2.5D网络芯片。

台积电的InFO使用扇出晶圆级封装,它大致位于2.5D与有机衬底系统级封装之间,所有这些都可以利用最先进的逻辑工艺节点,结合其他芯片或在较旧节点处开发的IP。

这里的关键是如何将芯片放在一起进行电气连接。STATS ChipPAC产品技术营销总监Seung Wook (S.W.) Yoon表示,一种新方法是使用层间电介质而不是凸块来连接裸片。“这比倒装芯片更可靠,而且没有凸块或管脚。”

我们还有更多的封装方式,对于IP供应商来说,这有巨大的好处,因为它们仍然可以销售用于最先进的芯片的老式节点开发的技术。对于模拟IP而言,IP供应商可以节约海量时间和开发成本。但它也为芯片制造商提供了降低成本的更多选择,因为它们不必将一切都缩小到同一个芯片上。这导致了半导体行业更多的合作和兴趣。

eSilicon营销副总裁Mike Gianfagna说:“这不再是疯狂的事情。几周前,我们刚刚完成了2.5D设计,使用了HBM(高带宽内存)和一个将在今年晚些时候投产的大型ASIC。这不仅仅针对ASSP供应商,他们拥有一个绝对的市场,而且成本没有对象。它正在转向ASIC,这意味着整个生态系统——包括客户,ASIC供应商,晶圆厂商,IP供应商都在为之努力。我们需要团队合作才能使新设计诞生。几年前,没有办法可以奏效。这是一个秘密社区。但是现在每个人都在谈论。”

结论

把这一切都带回摩尔定律是否有意义,我们不得而知。原来的研究是相当直截了当的,但它已经被重新诠释了很多次,现在很难说什么是摩尔定律,什么不是摩尔定律。正如Synopsys董事长兼联合首席执行官Aart de Geus所说:“如果你认为摩尔定律完全是经济学观点的话,那么就将面临巨大压力。但从技术的角度来看,还有很多地方可以去努力。八年前的争论是,finFET不会出现,因为它是垂直的、非常脆弱的结构,在经济上没有任何意义……摩尔定律的唯一规则是:永远不要说不可能。”

原文链接:http://semiengineering.com/moores-law-a-status-report/

今天是《半导体行业观察》为您分享的第1258期内容,欢迎关注。

【关于转载】:转载仅限全文转载并完整保留文章标题及内容,不得删改、添加内容绕开原创保护,且文章开头必须注明:转自“半导体行业观察icbank”微信公众号。谢谢合作!

【关于征稿】:欢迎半导体精英投稿(包括翻译、整理),一经录用将署名刊登,红包重谢!签约成为专栏专家更有千元稿费!来稿邮件请在标题标明“投稿”,并在稿件中注明姓名、电话、单位和职务。欢迎添加我的个人微信号 MooreRen001或发邮件到 jyzhang@moore.ren

【关于征稿】:欢迎半导体精英投稿(包括翻译、整理),一经录用将署名刊登,红包重谢!签约成为专栏专家更有千元稿费!来稿邮件请在标题标明“投稿”,并在稿件中注明姓名、电话、单位和职务。欢迎添加我的个人微信号 MooreRen001或发邮件到 jyzhang@moore.ren

相关文章

技术咨询

技术咨询 代买器件

代买器件 商务客服

商务客服 研发客服

研发客服