英特尔公司和戈登与贝蒂·摩尔基金会宣布,英特尔公司联合创始人先生于当地时间2023年3月24日星期五在夏威夷家中,在家人陪伴下平静,享年94岁。

本文引用地址:1968年7月,和他长期合作的同事罗伯特·诺伊斯创立了英特尔。摩尔最初担任执行副总裁,自1975年起担任总裁;1979年,摩尔被任命为董事会主席兼首席执行官,直至1987年卸任首席执行官的职位,并继续担任董事长;1997年,摩尔成为名誉主席,于2006年卸任。

的提出

除了创立英特尔,更为人熟知的成就,当属提出了计算机领域著名的定律 —— “”(Moore’s Law)。

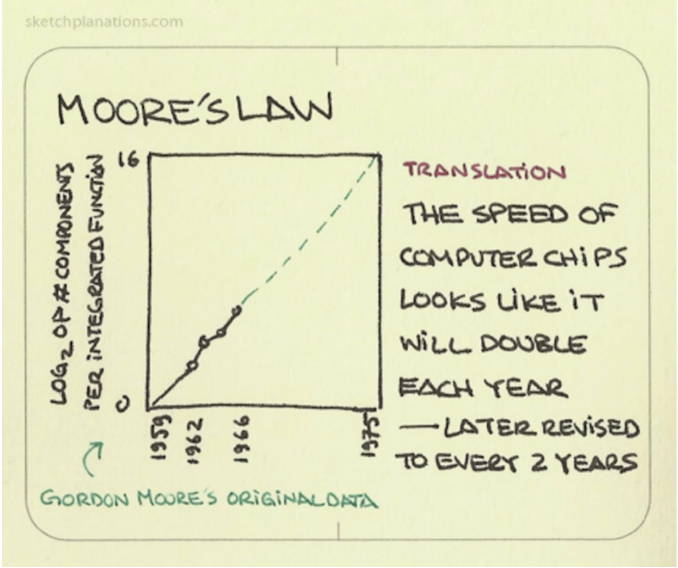

1965年戈登·摩尔在《电子学》(Electronics)杂志35周年专刊上写了一篇名为“让集成电路填满更多的元件”的短文,提出了基于实践数据观察的著名预测“”,即集成电路芯片上所集成的电路的数目,每隔12个月就翻一番,从而以指数方式提高计算机的数据处理能力。

后来逐步演化为每隔18-24个月翻一番,再后来又加上了经济含义,即单位晶体管的价格会每两年减少一半。无论如何,芯片技术以指数级速度增长,不断使电子产品变得更快、更小、更便宜,这个想法成为了半导体行业的驱动力,使得芯片普遍用于成百上千万的日常产品成为可能。

AI时代对摩尔定律的影响

虽然摩尔定律在历史上发挥了举足轻重的作用,但是随着进入AI时代,算力需求持续增加,半导体产业的变革也近在咫尺,业界关于“摩尔定律是否失效”的讨论越来越多。

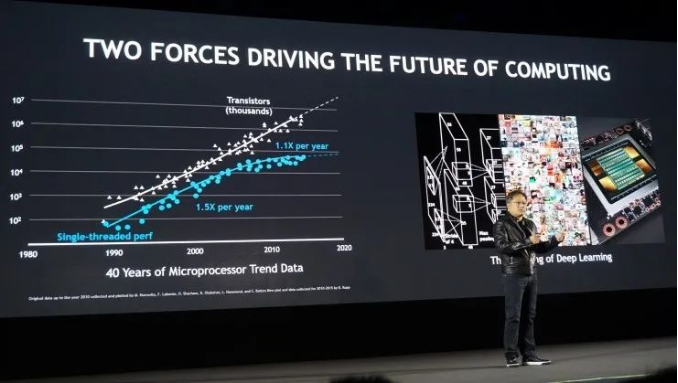

在黄仁勋看来:“摩尔定律已经结束了”。随着加速计算和人工智能时代的到来,摩尔定律的基本发展动能已经走到尽头,以类似成本实现两倍业绩预期对于芯片行业来说已成为过去式。

从定律狭义角度来说,摩尔定律确实是死了。因为摩尔定律的定义是集成电路在单位成本及功耗变动不大的条件下,晶体管数目提升一倍。也就是说,摩尔定律的精神在于集成电路性价比成本提升。但目前的发展已经走到性价比裹足不前,显然已经不符合该定义了。

根据美国乔治敦大学沃尔什外交学院安全与新兴技术中心(CSET)发布的研究数据显示,台积电一片采用3nm制程的12英寸晶圆,代工制造成本约为3万美元,约为5nm成本1.7万美元的1.75倍,也是7nm的3.21倍。在裸片(die)面积不变(即升级架构,不增加晶体管数量)、良率不变的情况下,未来苹果A17处理器如果采用3nm制程,成本或将上涨到154美元/颗,是iPhone第一大成本零部件。

随着芯片架构变得更加复杂,制程工艺越来越先进,硅晶片变得更加昂贵,而英伟达GPU和系统体系的发明,可以克服成本和通货膨胀问题。黄仁勋想到的破局点之一是借助GPU所带来的加速计算,“解决那些摩尔定律无法解决的,或者说在摩尔定律时代是不可能被解决的问题。”

黄仁勋将英伟达类比为台积电,最近发布的“NVIDIA AI Foundations(英伟达AI基础大模型)”,客户甚至不用自己配置超级计算机服务,直接借助英伟达DGX Cloud的AI超级计算云服务,通过一个Web浏览器就能训练、访问大模型产品。

但重返英特尔出任CEO的帕特·基辛格显然并不认同黄仁勋观点。在悼念摩尔文章中,基辛格再次重申:“英特尔仍然受到摩尔定律的启发,并打算追求它,直到元素周期表用尽。”

无论是基辛格还是黄仁勋的说法,都展现的是企业自身对于公司最匹配的战略方向考量,从系统角度来讲,两者观点并不矛盾。从英特尔角度来说,它一直引领技术前进方向,摩尔定律并没有失效;而黄仁勋的说法,是预测GPU将推动AI性能实现逐年翻倍,这不仅包含工艺节点,还有系统体系、软件算法、接口设计、数据传输等实现指数级提升。

“What Andy gives, Bill takes aways”(Andy指英特尔CEO安迪·格鲁夫,Bill指的是微软创始人比尔·盖茨)。这句流传甚广的谚语大意是说,硬件性能的大幅度提升所带来的广阔空间,很快就会被软件的发展消耗殆尽。相比起硬件,软件的进步则要容易得多,也快得多。另外从人们的体验来说,如果芯片只做制程工艺提升,不做任何优化,性能体验提升并不会出现质的飞跃。

其实早在2015年,摩尔定律50周年之际,退居幕后做慈善的戈登·摩尔接受纽约时报专栏作家托马斯·弗里德曼采访时直言:“摩尔定律”不会永远持续下去。

OpenAI公司首席执行官、“ChatGPT之父”山姆·阿尔特曼也曾表示,新版摩尔定律很快要来了。我们已经看到了摩尔定律的极限,尽管还没有触碰到,AI时代的摩尔定律或许正在孕育中,这可能是对戈登·摩尔最好的致敬。

摩尔定律的极限在哪里?

摩尔定律实现的维度主要分为制造、设计、封装三方面。摩尔定律在制造端的提升已经逼近极限,开始逐步将重心转向封装端和设计端。

随着人工智能、新的非硅半导体材料、光电量子等新技术的加速,以及半导体工艺和体系结构的改进,近年来,大家逐渐对于“摩尔定律”是否延缓或失效话题产生一定分歧,从而诞生出了多种技术演进方案。

同时,为了提升集成电路PPA:更高的性能,更低的功耗,更小的面积(成本),即使实现了晶体管堆积数量的增加,性能的提升,但是成本的飙升、高昂的价格让越来越多的企业停下对先进制程的追逐,思考摩尔定律本身的合理性。

摩尔定律是依据芯片工艺节点提出来的,工艺节点(nodes)是指芯片中MOS晶体管(一种金属氧化物半导体型场效应晶体管,是一种可变电流开关)栅极的最小长度,其尺寸和晶体管大小成正比。它是我们接触最多的芯片参数,比如:10nm、7nm等。

当节点是前一代的0.7倍(ITRS规划的最合适倍数)时,芯片面积将降低一半(0.7X0.7=0.49),换言之,就是单位面积上晶体管的数量翻了一番,这便是摩尔定律提出的基础。一般而言,每隔18-24个月,工艺节点就会发展一代。

毫无疑问的是,摩尔的预测能力在半导体产业的中早期(2000年之前)至少持续了20年,推动了整个集成电路产业的发展。2000年之前,每一代芯片的性能提升来自两个方面:一是按照Denard(登纳德)微缩效应,每代芯片的频率提升带来了40%的改进;二是每代芯片晶体管密度提升带来的体系结构的改进符合波拉克法则,即平方根级别的提升,达41%。将这两方面的性能提升叠加,最终得到1.97倍,于是每代会有差不多一倍的提升,而且,芯片晶体管密度的“摩尔定律”可换算成性能的“摩尔定律”。

从行业角度来看,业界一直遵循这一定律,随着年份推移而指数型尺寸微缩,从而诞生出90nm、65nm、45nm、32nm、28nm —— 每一代制程节点都能在给定面积上,容纳比前一代多一倍的晶体管。

但是当栅极缩小到20nm后,漏电率很高,平面型晶体管走到了尽头;随后三维鳍式场效应晶体管(FinFET)出炉,使芯片扩展到5nm,延续了摩尔定律。不过4nm后,鳍式结构也面临着漏电问题,摩尔定律又面临难题。

值得注意的是,立体晶体管还带来一个改变,原来用数字代表工艺的提升,那个数字是可以量出来的,有具体意义的物理量。而如今更倾向于营销概念,而它却不是节点的长度,而是等效长度,这早已脱离当初的摩尔定律了。

数字越小晶体管越密,7nm代表工艺比14nm更先进比5nm落后,不代表晶体管上的任何尺寸 —— 3nm不是晶体管宽度3nm,拿尺子量,找不到任何一个3nm的尺寸。

并且随着材料极限的接近,摩尔定律终将失效。因为芯片中连接晶体管的线宽如果只有1nm(几个原子大小),其材料性质会发生变化,导致无法正常工作。

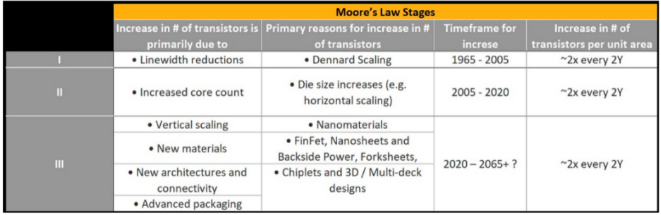

从摩尔定律的这段历史和时间表可以明显看出三个独立的阶段。

• 第一阶段:当晶体管密度由登纳德定标控制时,从1965年的公式延伸到大约2005年。

• 第二阶段:是半导体管芯的尺寸水平扩展(“更大的芯片”),通常是通过增加核心数量(核心是一个小的CPU或内置在更大的CPU中的处理器),从2005年左右延伸到2020年,届时管芯尺寸达到实际极限。

• 第三阶段:始于半导体管芯首先垂直缩放,然后通过新的步骤扩展以保持摩尔定律的有效性。复杂的3D结构,以及更多的材料、架构、连接选项和封装进步(小芯片等),所有行业都必须从设计到制造再到过程控制和测试,才能实现第三阶段的变化。

实际上,芯片性能的提升主要涉及半导体工艺和体系结构的改进,性能提升的同时,能耗也在提升。但如今,Denard微缩效应遇到了元件物理的瓶颈,早已失效,单核性能的提升没法纯粹依靠主频的提升。

于是,行业内出现了多核处理器、AI 芯片、专用集成电路(ASIC)或FPGA(现场可编程门阵列)芯片等,以提升芯片吞吐量性能,而非单个核心的计算性能。开始进入“后摩尔时代”。

后摩尔时代的发展趋势主要有:面向逻辑与存储的先进数字半导体产品的三维异构集成化;极多功能泛模拟产品的复杂异质集成化;利用云端数据中心、终端综合识别传感应用,半导体产业与产品的持续多样化。

目前业内对于所谓“后摩尔时代”有三大业务方向:More Moore(深度摩尔)、More than Moore(超越摩尔)、Beyond CMOS(新器件),主要在学术、产业两方面进行探索。

其中在学术方面,近年来,学术界在晶体管方面做出诸多探索,从而绕道解决“摩尔定律”延缓问题;相对于学术界的不计成本,产业行业人士则认为,企业端、产业端拥有很强的市场需求,对于“后摩尔时代”的落地应用则更为实际,拥有更多的价值。

但比如Chiplet是半导体封装技术,而量子,光电以及类脑等能不能在性能,通用性,以及经济效益上取代摩尔定律,还未有定论。

尽管当下“摩尔定律”还没死去,但人们已经在寻求“摩尔定律”放缓下新的技术创新了。短期内“摩尔定律”还会继续发展,当然不排除有一个革命性的技术来推翻定律。可能5年、10年之后就会有突破性革命技术诞生,比如量子、光电、新的化合物等,完全推翻了我们以前用硅做芯片。但现在这个阶段,硅芯片下的摩尔定律还是会往前走的,因为这是我们一个重要的技术迭代的媒介与平台。