来源:本文由半导体行业观察翻译自semiengineering.com,转载请咨询。。

编者按:本所谈及的新存储器和架构,尽管目前尚未广泛采用,但许多人认为改变不可避免。

存储器主导着许多SoC,我们很少听说某个设计包含太多的存储器。然而,存储器消耗了大部分的系统功耗,虽然这对于许多系统可能不是关键问题,但是对于物联网(IoT)边缘设备而言,总功耗是非常重要的。

几乎所有系统的存储需求都在变化。虽然新的存储器和存储器架构已经筹划了很长时间,但仍未被广泛采用。然而,许多业内人士认为临界点已然将近。

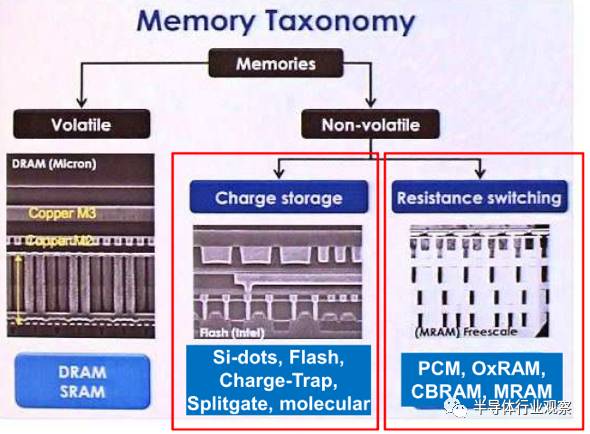

过去50年中,SRAM和DRAM已经成为存储器层次结构的主力,FLASH最近几年也在加入了“战场”。所有这些存储结构在往较小的几何结构缩放的过程中都存在问题,部分是因为它们都是平面结构。新的基于电阻开关的存储技术是金属层结构,消除了许多制造问题。因此,尽管我们今天可能不愿意采用它们,但它们可能是适合未来几代产品的唯一的存储技术。

图1:存储器分类

引人注目的新存储器包括:相变存储器(PCM)、铁电存储器(FeRAM)、磁阻RAM(MRAM)、电阻RAM(RRAM或 ReRAM)、自旋转移力矩RAM(STT-RAM)、导电桥RAM(CBRAM)、氧化物电阻存储器(OxRAM)。

Rambus公司的杰出发明家和营销方案副总裁Steven Woo说:“经典存储架构中有一个需要填补的空白。这些新型存储器中有一两种会生存下来,可能是3D XPoint(英特尔和镁光公司研发的PCM)、ReRAM、MRAM,也可能是其他的存储器,我不知道。关键问题是哪种会脱颖而出。但这主要由在给定性能参数范围内的数据输入输出确定。”

与性能直接相关的是功耗。 Adesto首席技术官Gideon Intrater说:“在给定功耗下的性能是一个非常重要的因素。在不同的应用中,存储器的用途非常不同,而且需求也是变化的。没有一个解决方案可以解决所有问题。”

那么,存储器子系统消耗了多少能量? Sonics的首席技术官Drew Wingard说:“我们对于特定应用芯片的统计数据已经搜集完成,得到了计算系统的数据,即各个系统占功耗的百分比。这些数字往往包括内存子系统。 当你一层层剥开其神秘面纱后,你会看到许多架构的存储器功耗,存储器功耗大约占总功耗的1/3至1/2。”

功耗和非易失性是FLASH存储器吸引人的因素。Synopsys公司IP部门高级产品营销经理Faisal Goriawalla说:“许多物联网设备依赖能量采集器,所以客户关注的是总功耗。设想一下,RFID标签。这些无源标签用于销售终端,不是用电池供电,而是从读取器的RF场获取能量,因此功率约束非常严格。”

物联网设备的另一个驱动力是成本。Cadence公司存储器和存储接口产品营销部门总监Lou Ternullo表示:“如果把存储器放在芯片上,就会删除引脚,降低了系统的成本。另一方面是硅面积增加。这是典型的SRAM。但是,如果需要嵌入式Flash,则需要一个特殊过程,成本十分昂贵。如果把所有的存储器都放在芯片裸片上,就会降低材料成本。如果需要放置比芯片裸片适合的更高的密度,那么就必须离开芯片。”

计算总能量

存储器消耗的总能量有几个部分,所有都要仔细考虑。它们是:

• 存储单元维护功率;

• 读、写和擦除功率;

• 接口功率;

• 架构的优化。

不同的应用可以用不同的方式平衡这些因素以及其它特性,例如持久性和性能。

仅为商业目的传播,不代表本刊观点

有一种能量成本与存储单元自身相关。这可能包括漏电流、刷新电路、或维持状态所需的有功电流。与许多存储器相关的总能量也可能取决于它们的规模,因为增加位线的规模会增加驱动电路的功耗,或在每个周期必须刷新的数据量。

以DRAM为例。Ternullo说,“DRAM的成本竞争力虽然不理想,但它使用必须刷新的电容单元。当你增加密度,单元容量下降——多亏了物理学定律——你必须经常刷新。所以它们试图变得更智能,包括诸如某些模式下的局部阵列自刷新技术,如果整个DRAM并不需要,那部分就不用自刷新。”

其他类型的存储器,例如SRAM,拥有无源动力功率元件,这些元件只是为了维持它们的状态。非易失性存储器(NVM)可能有零保持电流,无法忘记周围的逻辑。Goriawalla说,“漏电可能来自围绕存储核心的电路,NVM有一个使用传统CMOS器件的模拟组件。这些是较大的器件,所以这些器件的栅漏相当小,但是也有数字组件会产生栅漏。”

接下来是读、写和擦除存储单元所需要的能量。这些成本中的几个将与存储技术相关。Goriawalla继续说:“对于许多类型的FLASH存储器,写入电流往往高于读取电流。相比之下,多时间可编程(MTP)NVM具有相当高的能效。它们的程序电流低50倍,读取电流低10倍。 其原因是存储电荷的机制。在MTP存储器中,利用Fowler Nordheim(FN)电子隧穿,比嵌入式闪存使用的热载流子注入更节能。”

另一个考虑是访问机制。例如,许多Flash技术需要串行访问。CEA-Leti的高级系统和集成电路架构师Michel Harrand表示:“利用一些新兴的存储技术,你可以随机访问它们,无需顺序访问。你需要一些能量来写入一位,可能是10微安,这比DRAM略大,但DRAM是破坏性读出。当你读取一位时,你要读取完整的字线,然后你必须重写所有。新兴的NVM可以节省一些能量,即便它们写入一位需要更多的能量。它们不需要刷新。它会在你要写入的位数之间进行权衡。所以很难有确切的数字,因为它取决于你写入以及读取的位数。”

进出存储器的数据必须通过某种总线传输。Ternullo说:“存储器的大部分功耗与接口本身相关。在某些情况下,你面对的是难以改变的物理学规律。如果遵循这些标准,则I/O电压会发生变化,以帮助缓解这种情况。原来1.5V的DDR3已经变成了1.2V的DDR4和1.1V的LPDDR4。 从动态功率的角度来看,电压是关键组件,当你降低电压时可以降低动态功耗。”

降低接口成本的另一种方法是在芯片上集成,但是DRAM不能被嵌入,而且缩小Flash变得越来越困难。Goriawalla说:“系统功耗受到掩膜数量等因素的影响。与CMOS技术相比,嵌入式闪存需要12-14个额外的掩膜,并且可以增加25%的芯片裸片成本。”

还有其他因素会影响存储器的总功率,如系统的体系结构。缓存的设计是通过在芯片上放置少量快速、高功耗的存储器以减少访问时间,并且当所需的信息不在缓存中时,仅需要访问外部存储器。这减少了与访问外部存储器相关的时间和能量。如果在高速缓存中可以存储足够的数据,则可以最小化接口功率。

但因为SRAM 是高功耗的,所以物联网系统希望减少对其的依赖。然而,许多闪存器件,特别是在芯片外时,需要大量的SRAM。Intrater说:“无论何时,当处理器需要一个不在缓存中的程序时,处理器将从外部存储器获取必要的程序,然后继续。我们希望大部分程序都在缓存中。 闪存变成了内存层次结构的一部分。”

但这正在改变。“有一个名为‘就地执行’(XIP)的特征,此处你使用穿行NOR flash就像片外存储器。您可以让处理器直接从串行NOR flash读取数据,就像存储器一样。

另一个影响功耗的因素是读写的规模。当使用DDR时,单字节或字不会一次读取,而是可能突然读取512或1024。如果这是一个很好的能量使用,又如果不需要额外的字节读取,那么它依赖于应用程序,因此代表了浪费。这是一个示例,其中性能已成为驱动问题,并且对于许多系统可能是昂贵的功耗权衡。

A similar type of problem exists with NAND-type flash memories that are unable to write to a single location, instead requiring that a block of memory is first erased and then rewritten. This means there is a power penalty associated with small writes. An SRAM cache, even though it consumes more power, defers writes and may finish up providing energy savings.

NAND FLASH存储器也存在类似的问题——不能写入单一位置的,需要先擦除并随后重写存储器块。这意味着存在与小写入相关联的功率代价。 SRAM缓存,即使它消耗更多的功率,延迟写入,但是可能提供节能。

对于许多系统,现有的内存技术可能太耗电。Goriawalla说:“对于使用能量收集的系统。它们通常需要写入电流小于5μA,读取电流为几μA/ MHz。这加上了VDD的最小值 0.7 ~ 0.9V。所以我们谈论的是微小系统的功耗需求。 这些数字比大多数嵌入式闪存技术的数量级小。”

其他注意事项

同样,成本有许多方面,其中一些已经讨论过。功耗对成本有直接影响,但其他因素包括引脚数量、封装、芯片内的成本,以及与板上集成相关的成本。

Intrater说:“小系统往往拥有位于同一芯片裸片的嵌入式闪存。但也有局限性。我们看到系统要迁移到28nm,但在流程节点没有嵌入式闪存。闪存滞后于标准CMOS工艺。如果可以使用嵌入式闪存,那么这就是始终不变的最优解。但在许多情况下,这样却并不可行,原因在于成本,或者系统的其他部分需要更积极的过程节点。然后你需要恢复使用外部内存器,并开始遇到性能和功耗的问题。两者之间的联系需要具有正确的特性,以提供足够的性能,并且消耗更多的功率。”

这一判决对于新的内存类型变得更容易。 Harrand说:“在同一芯片上与逻辑一起进行闪存处理是很困难的。新存储器很友好,一切都在生产过程的后端。 这意味着在逻辑过程中可以有完全相同的晶体管,这使得它更容易嵌入逻辑或处理器。28nm使得嵌入式闪存过程变得很困难,所以我们有机会替换嵌入式闪存与这些新的记忆。”

许多互连架构针对现有存储器类型进行了优化。Harrand说:“DDR接口不太适合NVM。使用DDR,首先要声明你想要寻址的行或页面,然后声明你是要读取或写入。这对于新兴的NVM是不利的,因为如果你想要读取或写入,你一开始就必须知道。”Harrand表示,有办法克服这一限制,但它们会降低性能。

另一个障碍是接受新的权衡。Harrand继续说,“今天,我们可以拥有具备足够续航力的高度DRAM,但是无法拥有高密度,但是可以同时拥有速度和续航力。会有一些被优化接近DRAM,并具有完整的保留,或者有一些会有数日的保留,但并不是10年的保留,或者有一些会有优化保留,但他们没有速度。”

目前尚不清楚何时以及哪些新的存储器将首先打破障碍,但微控制器的出现将这些新的存储器嵌入到其中。随着数量的增加,成本将下降,这将加速它的应用。不久后,许多物联网系统将别无选择,尤其是如果它们想利用新的制造技术节点的话。

【关于转载】:转载仅限全文转载并完整保留文章标题及内容,不得删改、添加内容绕开原创保护,且文章开头必须注明:转自“半导体行业观察icbank”微信公众号。谢谢合作!

【关于投稿】:欢迎半导体精英投稿,一经录用将署名刊登,红包重谢!来稿邮件请在标题标明“投稿”,并在稿件中注明姓名、电话、单位和职务。欢迎添加我的个人微信号MooreRen001或发邮件到 jyzhang@moore.ren

【关于投稿】:欢迎半导体精英投稿,一经录用将署名刊登,红包重谢!来稿邮件请在标题标明“投稿”,并在稿件中注明姓名、电话、单位和职务。欢迎添加我的个人微信号MooreRen001或发邮件到 jyzhang@moore.ren