今天给大家分享两点内容: 一是,为什么我们要先开启STM32外设时钟;二是,关于STM32的 I/O 复用功能及什么时候开启AFIO时钟。

STM32为什么要先开启外设时钟?

相信很多朋友都曾遇到过这种坑,我最初学习STM32的时候同样也遇到过。下面,我就来说说为什么我们要先开启STM32外设模块时钟,再对其外设模块初始化配置?

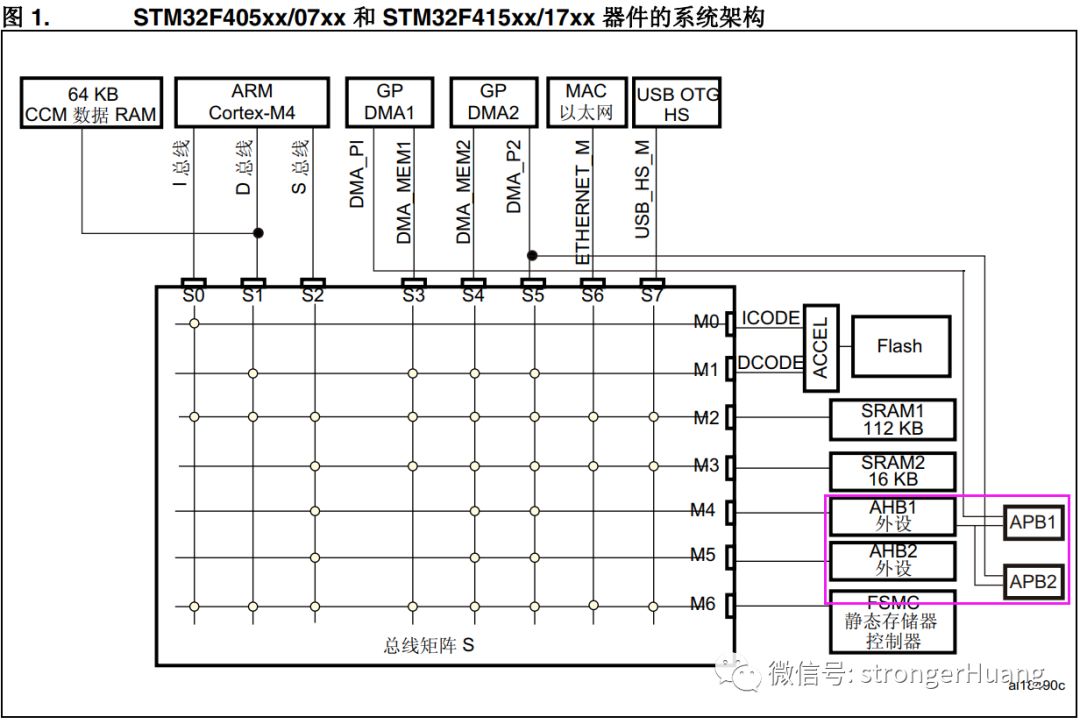

1、系统架构

不同类型的STM32,它的系统架构各有不同,但原理都类似,由多条主控总线和多条被控总线组成(请参看【参考手册】存储器和总线架构章节)。

以STM32F4为例:

● 八条主控总线:

— Cortex-M4F 内核 I 总线、 D 总线和 S 总线 — DMA1 存储器总线 — DMA2 存储器总线 — DMA2 外设总线 — 以太网 DMA 总线 — USB OTG HS DMA 总线 ● 七条被控总线: — 内部 Flash ICode 总线 — 内部 Flash DCode 总线 — 主要内部 SRAM1 (112 KB) — 辅助内部 SRAM2 (16 KB) — 辅助内部 SRAM3 (64 KB)(仅适用于 STM32F42xxx 和 STM32F43xxx 器件) — AHB1 外设(包括 AHB-APB 总线桥和 APB 外设) — AHB2 外设 — FSMC

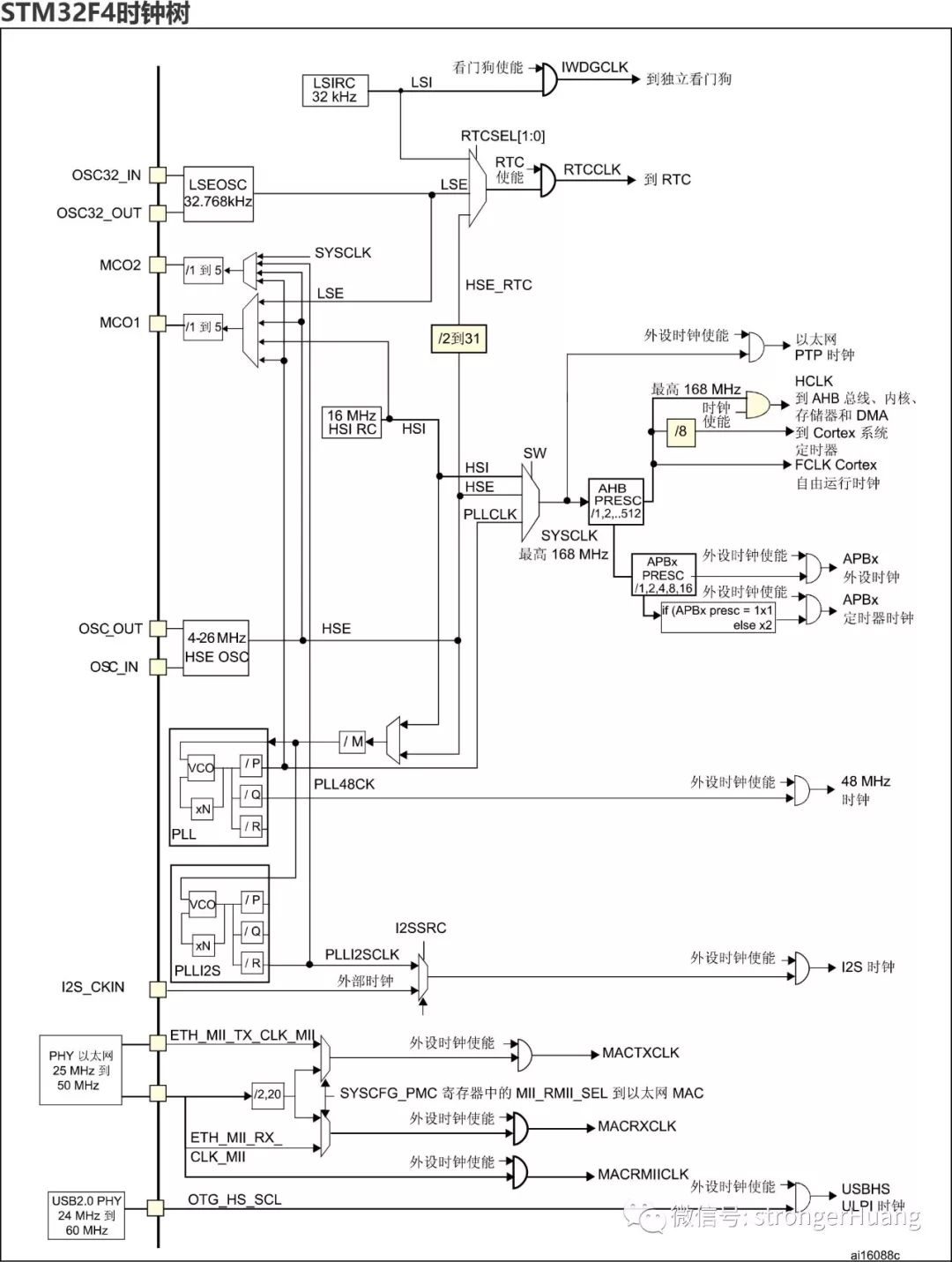

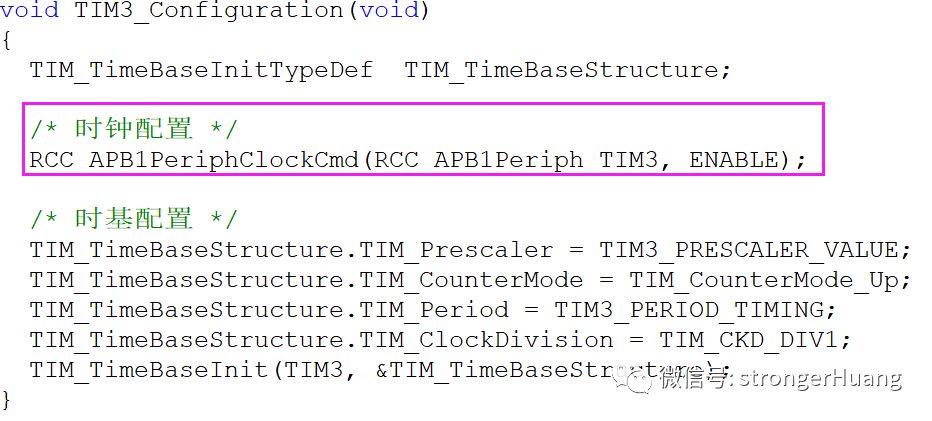

借助总线矩阵,可以实现主控总线到被控总线的访问,这样即使在多个高速外设同时运行期间,系统也可以实现并发访问和高效运行。 2、关于AHB和APB总线 AHB:Advanced High-performance Bus,即先进的高性能总线。 APB:Advanced Peripheral Bus,即先进的外围(外设)总线。 上面说了系统总线的架构引伸出来的就是AHB和APB总线,那为什么要讲述AHB和APB总线呢? 我们操作的外围设备一般都是位于AHB和APB总线上,而AHB可以引伸出AHB1、AHB2,甚至AHB3。同样APB也存在APB1、APB2等。 比如,USART1外设位于APB1总线上,GPIOA位于AHB1高速总线上。 请注意参考手册中“AHB/APB 总线桥”这一小节,有一条重要的内容:每次芯片复位后,所有外设时钟都被关闭( SRAM 和 Flash 接口除外)。使用外设前,必须在 RCC_AHBxENR 或 RCC_APBxENR 寄存器中使能其时钟。 3、STM32时钟控制 请参看STM32参考手册关于【复位与时钟控制RCC】章节。 STM32的时钟控制模块因MCU芯片不同,各有差异,但原理都类似,功能也相当丰富。主要的目的就是给相对独立的外设模块提供时钟,也是为了降低整个芯片的功能。 降低功耗是主要原因,还有一个原因,就是为了兼容不同速度的设备,有些高速,有些低速,如果都用高速时钟,势必造成浪费。 RCC给外设提供时钟是一个主要目的,那么为什么要提供时钟呢?原因在于外围设备的寄存器需要时钟才能工作。你可以把外设当做一个设备,而这个设备需要给它提供电源(时钟)才能工作。 你在STM32参考手册的“RCC”章节可能会看到这么一句话:当外设时钟没有启用时,软件不能读出外设寄存器的数值,返回的数值始终是0x0。 4、总结 看到这里,相信聪明的你已经明白了为什么我们要先开启STM32外设模块时钟,再配置其外设模块了。 简单来说,就是操作外设是通过外设总线来实现,只有外设总线有时钟了才能操作外设。 坑: A.先使能外设时钟,再对其进行配置

STM32的时钟控制模块因MCU芯片不同,各有差异,但原理都类似,功能也相当丰富。主要的目的就是给相对独立的外设模块提供时钟,也是为了降低整个芯片的功能。 降低功耗是主要原因,还有一个原因,就是为了兼容不同速度的设备,有些高速,有些低速,如果都用高速时钟,势必造成浪费。 RCC给外设提供时钟是一个主要目的,那么为什么要提供时钟呢?原因在于外围设备的寄存器需要时钟才能工作。你可以把外设当做一个设备,而这个设备需要给它提供电源(时钟)才能工作。 你在STM32参考手册的“RCC”章节可能会看到这么一句话:当外设时钟没有启用时,软件不能读出外设寄存器的数值,返回的数值始终是0x0。 4、总结 看到这里,相信聪明的你已经明白了为什么我们要先开启STM32外设模块时钟,再配置其外设模块了。 简单来说,就是操作外设是通过外设总线来实现,只有外设总线有时钟了才能操作外设。 坑: A.先使能外设时钟,再对其进行配置

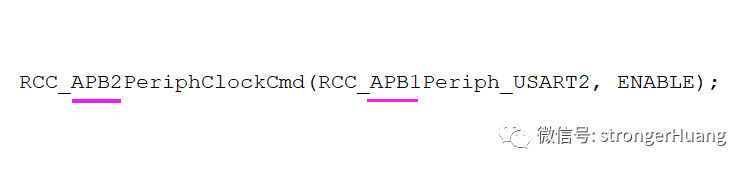

B.时钟配置需对应总线

这种基于标准外设库的低级错误,相信肯定有不少人遇到过,希望提高警惕。

AFIO复用时钟

有朋友问:“什么时候开启AFIO时钟”。写了上面章节,就顺便再讲述一下关于STM32的I/O复用功能及什么时候开启AFIO时钟。

1、什么是I/O 复用功能?

简单来说,就是把普通I/O用作其它的功能。如:将PA9引脚用作USART1的Tx引脚,那么我们就把这个Tx引脚称为PA9的复用功能。

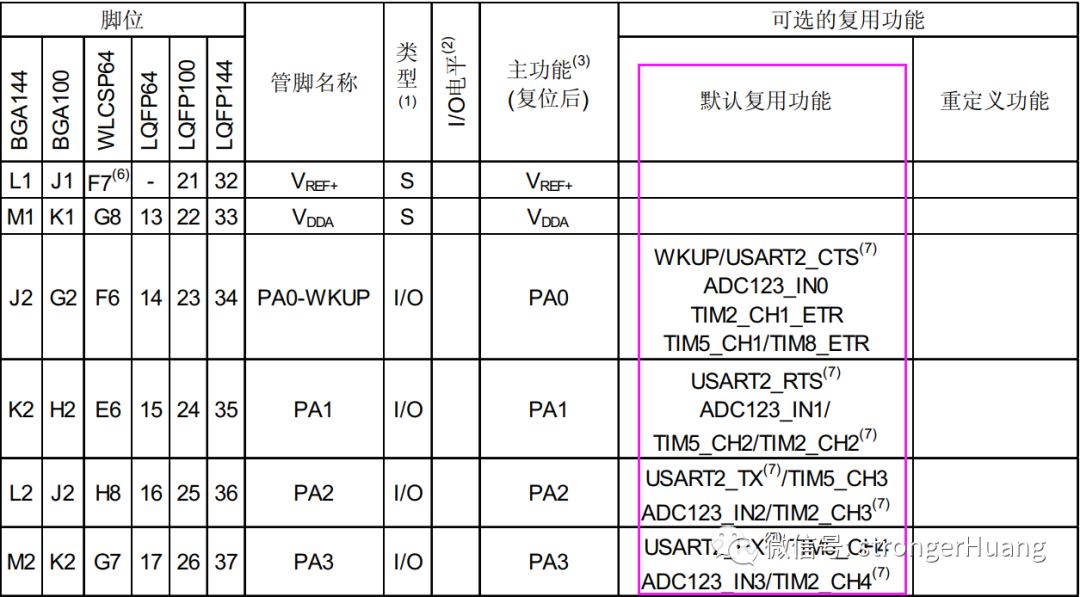

打开数据手册,会发现类似如下的列表:

2、什么时候开启AFIO时钟?

为了优化芯片引脚封装的外设数目,可以把一些复用功能重新映射到其他引脚上。设置复用重映射和调试I/O配置寄存器实现引脚的重新映射。这时,复用功能不再映射到它们的原始分配上,而是映射到“重定义功能”上(见上图)。

这种将引脚重定义到其它引脚上的功能在几乎所有STM32芯片中都有这个功能,但是实现的方法可能有所不同,其中STM32F1就是通过事件控制的方式将特定功能引脚连接到对应PORT和PIN上。

简单来说,如果需要使用重定义功能,那么就需要开启AFIO时钟。

最后,如果你觉得你的程序可能是因为时钟配置的问题,不妨上电第一步使能所有时钟试试。