方法1

可以使用STEP7(TIA Portal)的IEC定时器来通过简单的编程产生一个脉冲发生器。

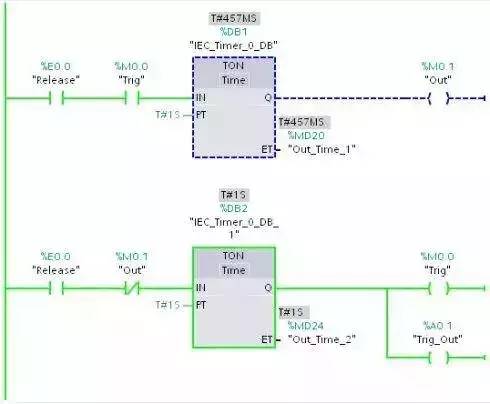

图.01展示的是如何利用两个“TON”(接通延时定时器)来实现在输出端 Q0.1 输出周期性脉冲信号的。

图.01

注:图中E0.0即为I0.0,A0.1即为Q0.1,德语关系。

“接通延时定时器”指令将使得输出端 Q 延迟一段时间接通,该时间通过 PT 来定义。

下表将描述如何实现脉冲发生功能。

脉冲发生器的功能

1 输入I0.0 “Release”用于激活此脉冲发生器。

2 标志 M0.1 “Out"”初始值为“False”,因此,下面一条接通延迟定时器指令“TON”开始计时。

3 当接通延时时间到达的时候,标志 M0.0 “Trig"”将被置位并且输出 Q0.1 “Trig_Out”获得 “True”信号。

4 M0.0 的“True”信号将触发上面一条“TON”指令开始计时。

5 当第二次接通延时时间到达的时候,标志 M0.1“Out”被置位。

6 M0.1 的 “True”信号将断开下面一条 “TON”指令的计时条件并中断该定时器,同时使标志 “M0.0”被复位。输出 Q0.1 “Trig_Out”获得 “False”信号。

7 M0.0 的 “False”信号将中断上面一条“TON” 指令,并将 M0.1 复位。

8 标志 M0.1 的 “False”信号将重新触发下面一条“TON"”指令,然后整个过程再次重新开始。

图.02展示了这个脉冲发生器的时序图

图.02

优势:

1. 脉冲信号为True和False的时间可以设为变量。

2. 使用这种方式可以灵活的更改脉冲信号的占空比。

方法2

您可以通过设置时钟标志来产生一个占空比为 50% 周期性脉冲信号。

步骤 :

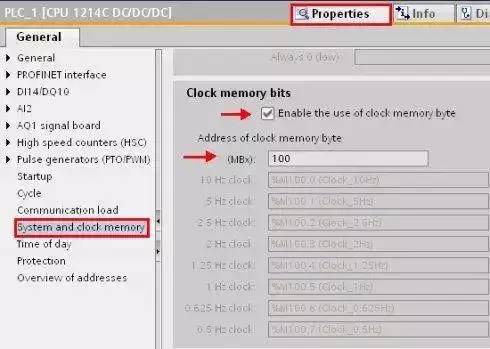

1 打开您的STEP7项目,在设备视图中双击S7 CPU模块。

2 选择“ProperTIes” ,并在页签中点击“System and clock memory”。

3 勾选“Enable the use of clock memory byte”选项并为时钟标志选定一个字节的地址;比如,“100”表示 MB100。时钟标志的每一位将被分配为不同频率的脉冲信号。

图.03

4 保存并编译硬件组态。然后下载到CPU。

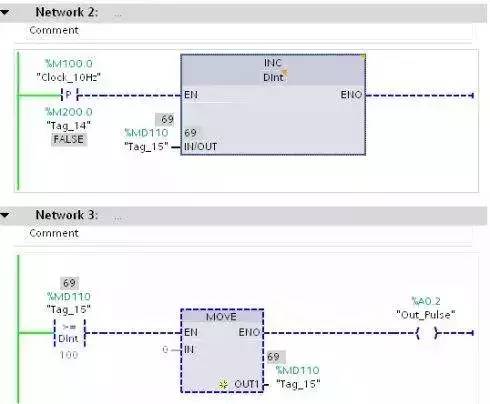

5 标志M100.0将被分配为10 Hz频率的脉冲,也就是说它每0.1秒改变一次状态。图04中展现了让“IN/OUT”引脚的操作数MD110循环递增的例子。比较指令连接MOVE指令使得当操作数到达99时将被复位为 0。

图.04

优势

1. 只需更改组态设置,简单便捷。

2. 不需要用 IEC 定时器指令。

使用时钟标志说明,时钟标志的占空比是1:1。

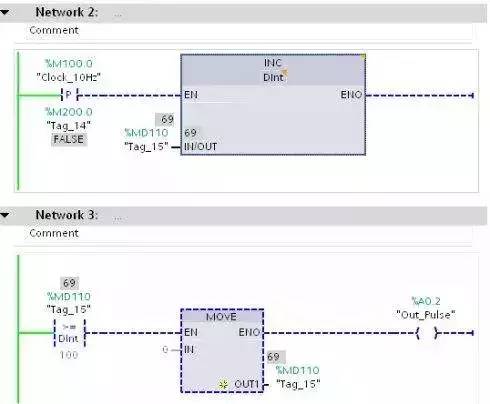

由于时钟标志的运行周期和CPU 是异步的,在一个长扫描周期中时钟标志能变化多次,这将导致歧义。

举例:

1. 时钟标志的保持时间是100ms 。

2. 程序的扫描周期是100ms并有正负10ms的波动。

3. 如果时钟标志在几个周期后状态都为 1 ,则可能感觉在监控时有 300ms 状态没有变化。

图.05

1. 时钟标志每 100ms 发生变化

2. 扫描周期: 110ms

3. 扫描周期: 90ms

4. 在线监控时钟标志