编译自EDN

介绍

现代电子系统需要小型、轻量、高效的电源。 这些电源需要经济高效的方法来从交流配电网获取电力并将其转换为直流电以运行电子系统。

高开关频率是小尺寸的最大推动因素之一。氮化镓 (GaN) 开关可以提供实现高频的有效方法,因为它们具有低寄生输出电容 (COSS) 和快速的开启和关闭时间。 然而,通过使用先进的控制及拓扑技术,可以放大 GaN 开关的高功率密度优势。

在本文中,我将研究服务器 5 kW 功率因数校正器 (PFC) 内使用的高级控制方法。 该设计使用高性能 GaN FET 以最高的实用频率运行电源。 该电源还采用了一种新颖的控制技术,可以从 GaN FET 中提取更多性能。 最终结果是具有更高功率密度的高效率、小尺寸设计。

系统总览

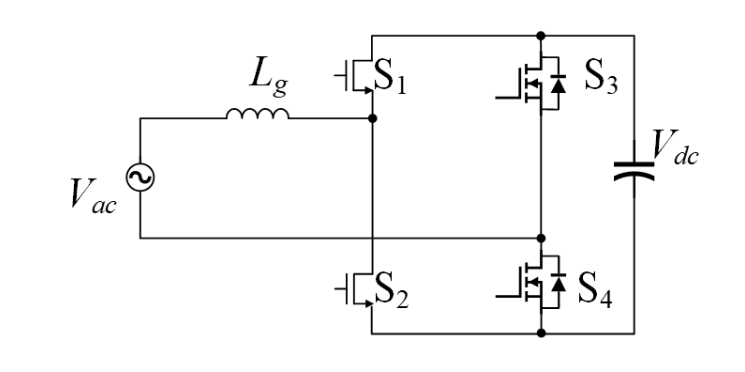

众所周知,图腾柱 PFC 是高功率、高效率 PFC 的主力。 图 1 说明了该拓扑。

图 1 基本图腾柱 PFC 拓扑,其中 S1 和 S2 是高频 GaN 开关,S3 和 S4 是低频硅开关。 资料来源:德州仪器

S1 和 S2 是高频 GaN 开关,工作频率在 70 kHz 到 1.2 MHz 之间。 S3 和 S4 是在线路频率(50 至 60 Hz)下工作的低频开关硅 MOSFET。

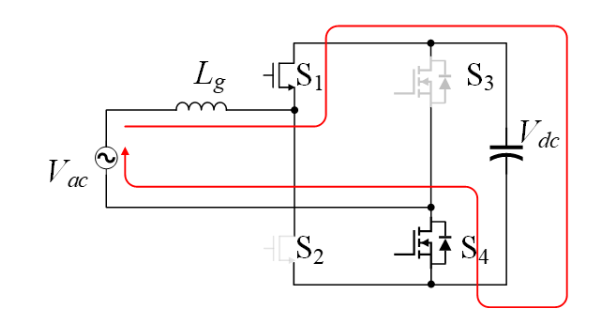

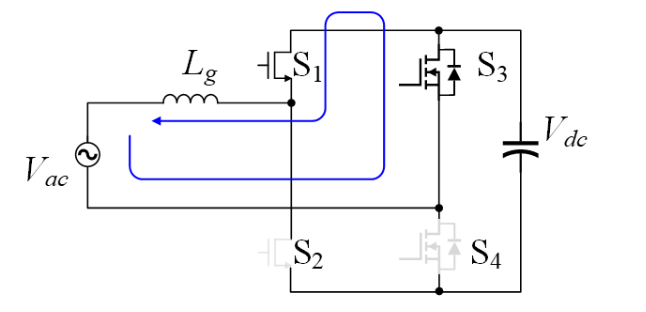

在交流线路的正半周期期间,S2 用作控制 FET,S1 用作同步整流。 S4 始终开启,S3 始终关闭。 图 2 显示了由于控制 FET ,S2导通而导致电感器电流增加的时间间隔。 图3显示了电感电流通过同步整流器S1放电的时间间隔。

图 2 正半周期电感充电间隔。 资料来源:德州仪器

图 3 正半周期电感放电间隔。 资料来源:德州仪器

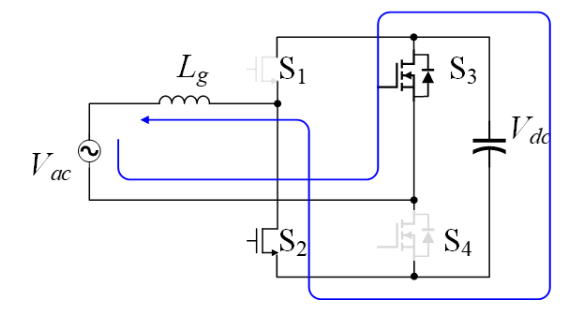

图 4 和图 5 显示了负半周期的相同行为。

图 4 负半周期电感电流充电间隔。 资料来源:德州仪器

图 5 负半周期电感放电间隔。 资料来源:德州仪器

零电压开关

S1 和 S2 使用 GaN 开关,使转换器能够以更高的开关频率运行,同时开关的开通和关断损耗更低。另外,如果 GaN 开关可以通过零电压开关 (ZVS) 开启,则可以实现更高的频率。 此设计的目标是在所有线路和负载条件下的每个开关周期都实现 ZVS。 为了做到这一点,需要确保两件事:

用于告知控制器是否已实现 ZVS 的反馈

微控制器可以实时执行算法,以实现低总谐波失真 (THD)

您可以通过 GaN 开关内部的集成零电压检测 (ZVD) 传感器来完成第一项任务,以告知系统开关是否通过ZVS导通。

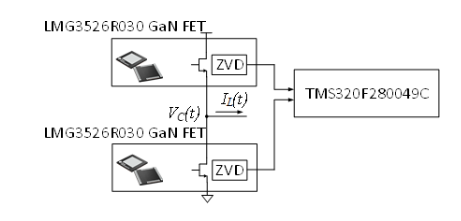

图 6 采用具有集成驱动器、保护和温度报告功能的 LMG3425R030 GaN FET 以及 TMS320F280049C MCU 的 ZVD 反馈框图。 资料来源:德州仪器

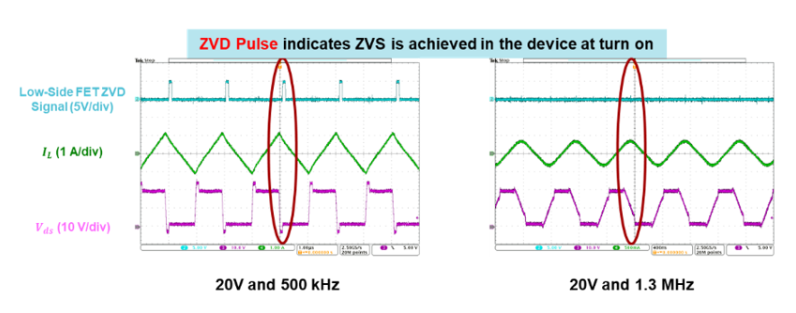

图 7 带 ZVS 的 ZVD 信号(左)和不带 ZVS 的 ZVD 信号(右)。 集成的 ZVD 传感器启用 ZVD 标志,如果开关通过 ZVS 打开,则可以看到该标志。 资料来源:德州仪器

将此功能集成到 GaN 开关内可提供许多优势:最少的组件数量、低延迟以及可靠的 ZVS 事件检测。

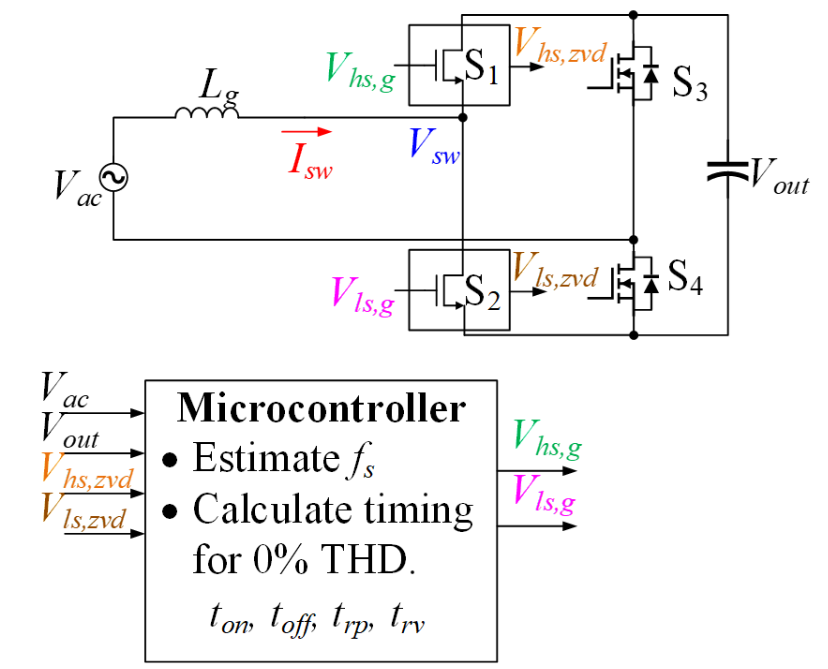

除了 ZVD 之外,您还需要一种能够计算开关时序参数的算法,以便同时实现 ZVS 和低 THD。 图 8 是实现该算法所需的硬件框图。

图 8 基于 ZVD 的控制方法所需的硬件,该方法使算法能够计算开关时序参数,以同时实现 ZVS 和低 THD。 资料来源:德州仪器

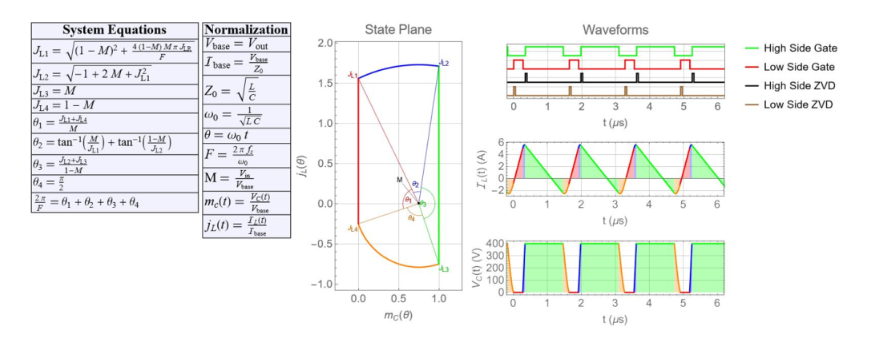

求解 GaN FET 谐振跃迁的 ZVS 状态平面电压 (VDS) 将为您提供此设计的算法。 图 9 显示了 GaN FET VDS、电感器电流和控制信号,以及时域图和状态平面图。

图 9 具有 GaN FET VDS、电感器电流和控制信号的谐振过渡状态平面解决方案,以及时域图和状态平面图。 资料来源:德州仪器

在图 9 的状态平面图中:

“j”是每个死区时间间隔开始和结束时的归一化电流

“m”是标准化电压

“θ”用于归一化时序参数

该图还显示了标准化关系。 图 8 中的微控制器求解图 9 中所示的状态平面系统方程,以便系统实现 ZVS 和理想功率因数。 ZVD 信号提供反馈,指示微控制器如何调整开关频率以满足 ZVS。

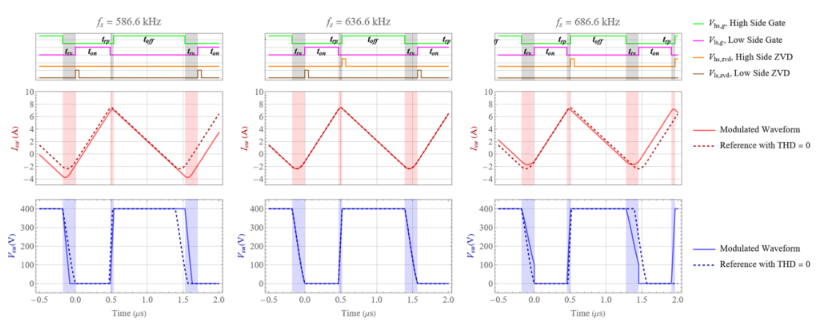

图 10 显示了应用频率太低(左)、理想(中)和太高(右)时的工作波形。 您可以看到,仅当应用频率处于理想值时,两个 ZVD 信号才会出现; 因此,可以改变频率直到两个 FET 实现ZVS的理想工作点。

图 10 应用频率太低(左)、理想(中)和太高(右)时的 ZVD 控制波形。 资料来源:德州仪器

硬件性能

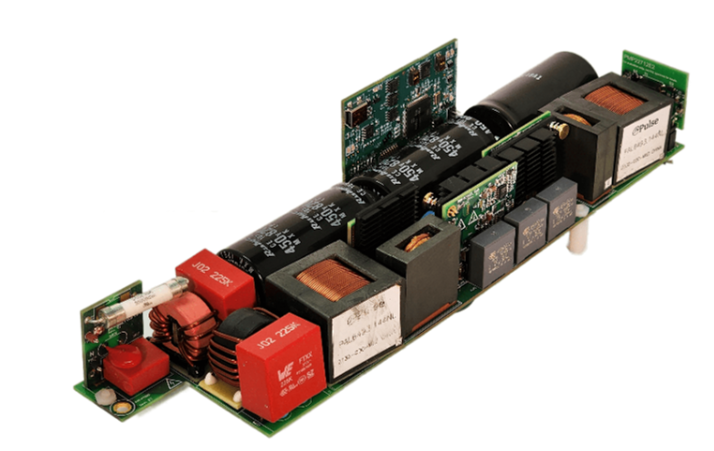

图 11 是使用 GaN 和之前描述的算法的两相 5 kW 设计示例的照片。

图 11 两相 5 kW 基于 GaN 的 PFC,具有应用算法所需的硬件,以实现更高的频率并提高整体解决方案的效率。 资料来源:德州仪器

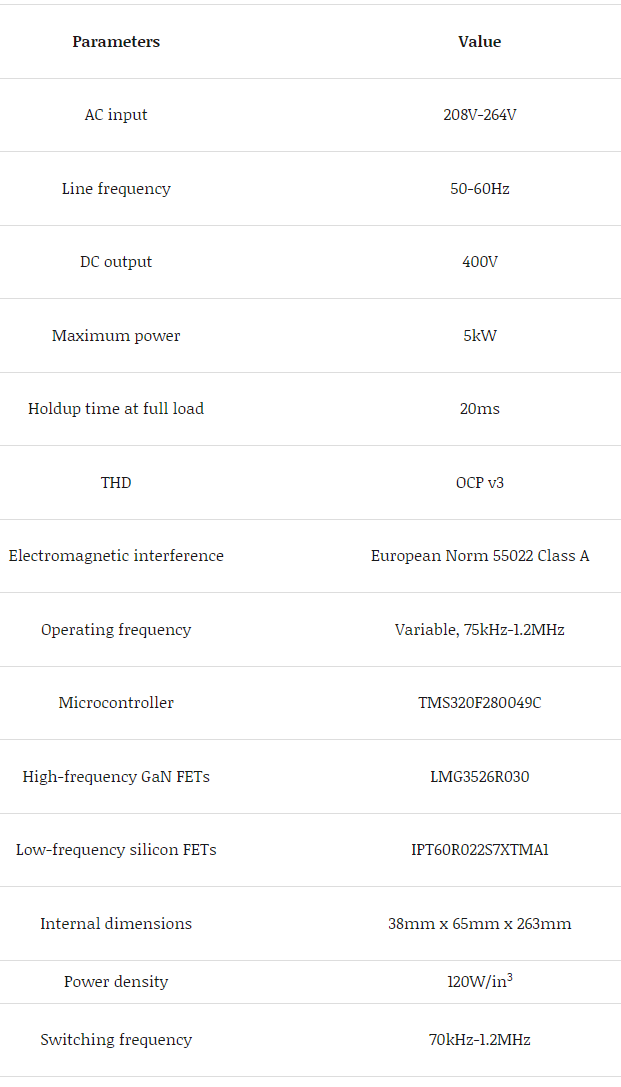

表 1 列出了设计示例的规格。

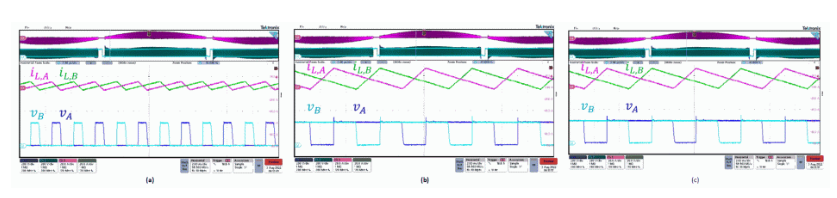

图 12 显示了两相(VA 和 VB)的电感器电流波形(ILA 和 ILB)和 GaN FET VDS 波形。 这些图处于全功率状态,说明了三种不同的操作条件。 在每种情况下,都可以看到 ZVS 和正弦电流包络。 所有三个图的条件均为 VIN = 230VRMS、VOUT = 400V、P = 5kW 以及 200V/div、20A/div 和 2μs/div。

图 12 在全功率下采集的电感器电流波形(ILA 和 ILB)和 GaN FET VDS 波形:(a) VIN≪VOUT/2、(b) VIN=VOUT/2 和 (c) VIN≫VOUT/2。 资料来源:德州仪器

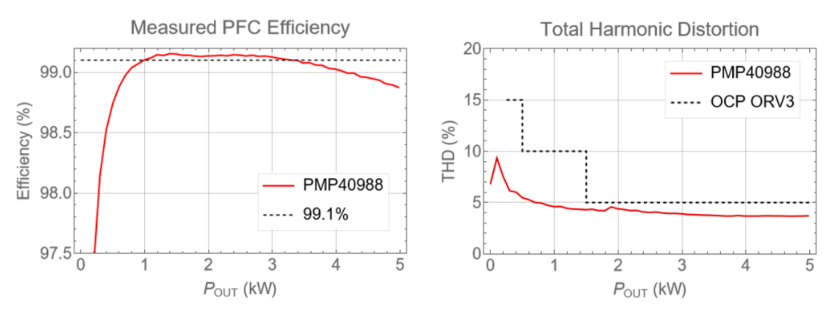

图 13 显示了在整个负载范围内以 230VAC 输入运行的系统的测量效率和 THD。

图 13 在整个负载范围内使用 230VAC 输入运行的两相 PFC 的效率和 THD。 资料来源:德州仪器

减少电源尺寸

GaN 开关可以通过实现更快的开关频率来提高各种应用的功率密度。当然,添加先进控制算法等技术也可以进一步显着减少电源的尺寸。

本文作者:Brent McDonald 担任德州仪器 (TI) 电源设计服务团队的系统工程师,为各种高功率应用创建参考设计。 Brent获得了威斯康星大学密尔沃基分校的电气工程学士学位,以及科罗拉多大学博尔德分校的电气工程硕士学位。