芯片设计复杂度不断提升,而芯片开发的时间窗口并未延长。这意味着,一方面,芯片开发团队需要信任成熟技术,大量复用IP;另一方面,新技术引入前需要更全面的分析仿真,以确保引入的新技术与工艺及成熟技术兼容。

工艺复杂化的趋势主要表现为两个方向。横向上,需要同时考虑的参数越来越多,很多传统工艺不需要考虑的寄生效应,在先进工艺中变得越来越不能忽视;纵向上,由底至顶通盘考虑成为必要,而不止于可制造设计(DFM)与可测试设计(DFT)等传统设计思维,用Silvaco全球市场副总裁Thomas Blaesi的话来说就是,系统级芯片(SoC)设计需要从原子到系统的一贯式设计流程。

在从原子到系统一贯式设计流程概念提出之前,EDA公司就提倡设计与工艺共同优化(Design Technology Co-Optimization, 简称DTCO)概念。笔者理解,从原子到系统一贯式设计,是DTCO理念的发展,更强调由底至顶通盘考虑的重要性。

如今复杂芯片集成度高达数十亿颗晶体管,苹果公司的A12处理器就集成了69亿颗晶体管。英伟达(Nvidia)公司的Tegra Xavir处理器更是集成了90亿颗晶体管,耗资20亿美元,总投入工程资源达8000人年。对于这样复杂的芯片开发,IP复用是开发的关键,据统计,现在复杂SoC中超过85%的模块是复用模块,预计到2025年,复杂SoC中的复用模块比例将达到90%,只有10%是新技术。

芯片设计复杂度不断提升,而芯片开发的时间窗口并未延长,这意味着芯片开发团队需要信任成熟技术,大量使用经过验证的成熟技术(IP)。成熟IP管理及优化成为芯片开发团队的必然需求,针对此需求,Silvaco提供Xena工具,来统一管理SoC开发过程中所需要的IP。据Thomas Blaesi介绍,Silvaco从并购IPExtreme开始进入IP市场,近年来通过并购整合已经打造了丰富的IP产品线,其中车载半导体用IP覆盖面非常广,其他先进工艺IP也不断取得突破,在2019年5月三星宣布与Silvaco达成协议,双方将在先进工艺上进行合作,三星将在14纳米等先进工艺采用Silvaco的IP。

IP与标准单元库等成熟模块在SoC当中的应用也并非拿来就用,针对需求的定制化优化非常重要。

在2019 Silvaco用户大会(上海站)上,Certus半导体公司首席技术官Stephen Fairbanks就向与会者介绍了定制化输入/输出模块(I/O)的重要性。他表示用户购买IP主要考虑三个因素,即成本、时间以及将技术应用于硅工艺的挑战。

Stephen Fairbanks在SURGE 2019上的演讲

Stephen Fairbanks表示,每一家晶圆代工厂都提供标准IO库,这些通常可以免费获得,但是全球前十大芯片设计公司,每一家都有自己开发的数字IO与模拟IO库,这是因为标准IO库为了适应更多应用,存在很多冗余设计,对于定制化芯片开发,这些冗余设计就成为成本的大敌。优化IO设计,不仅能大幅度缩减面积以降低成本,而且能提升防静电水平,满足多电源供电等复杂设计需求。

大量成熟技术复用为芯片开发节约了时间,但仍有一定比例的新技术在引入,如前所述,由于先进工艺中需要考虑的参数越来越多,因此如何确保引入的新技术能在硅工艺上正常工作也变得越来越有难度。

85%复用IP模块通常是架构层面的技术复用,而15%或10%的新技术,往往与新材料、新工艺密切相关,这就需要在纳米及原子层面进行仿真和分析。

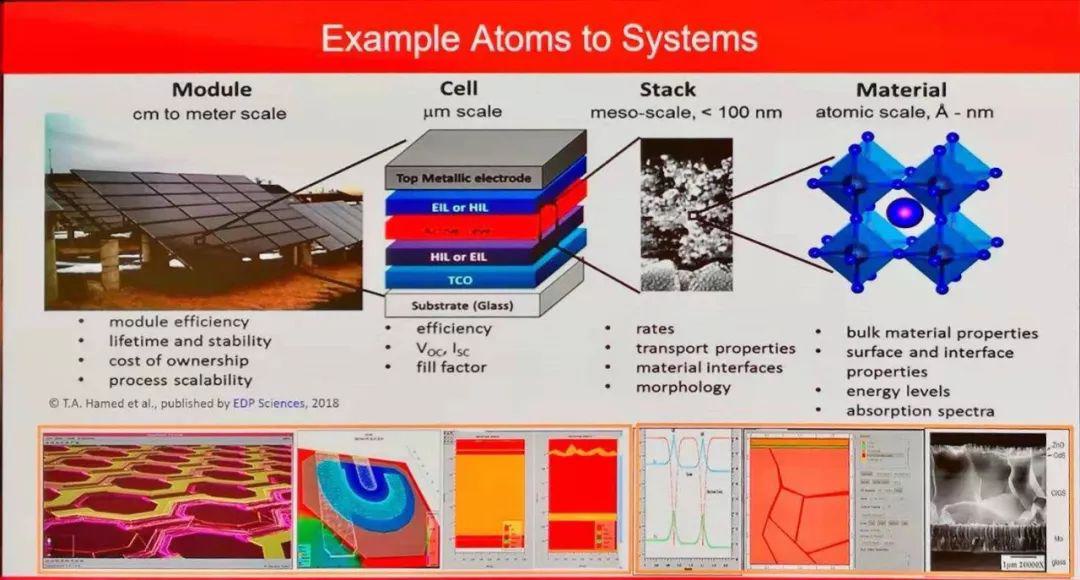

Thomas Blaesi表示,按照尺寸从大到小,从原子到系统一贯式设计流程大体可以分为四层:整机层面,尺寸是几厘米到几米,主要考虑的因素是系统效率、寿命及稳定性,还有成本及工艺可扩展性;单元电路,尺寸在微米级别,主要考虑的是效率、开路电压、短路电流,以及填充因子(太阳能电池)等;材料叠片(stack),尺寸小于100纳米,主要考虑传输特性、材料接口、晶体形态等因素;材料层面,尺寸在纳米或0.1纳米级别,主要考虑散体物理特性、能级、吸收光谱特性等因素。

将来的设计师,必须具备在原子层面进行仿真分析的能力,能够理解材料特性,并能推导材料在工艺或器件级的性能表现。

“设计师需要对材料在纳米级别进行仿真,分析原子在芯片运作时的行为模式,在应用一种新工艺时,设计师需要了解工艺底层的材料物理特性,并在量产前进行足够完善的仿真,来保证设计的可制造性。” Silvaco首席技术官Babak Taheri也曾这样表示。