2022年末,人工智能对话机器人 ChatGPT 的发布引发全球性轰动,其基础支撑的人工智能大模型成为产业热点。人工智能大模型通过“自监督学习+预训练+精调”的模式,能够低成本、高适应性的赋能下游诸多领域,成为人工智能应用落地的最优选择。随后,全球科技互联网龙头纷纷推出自身的人工智能大模型。 人工智能大模型训练数据量巨大,对算力尤其是智能算力需求庞大,且将在未来持续高增长,驱动全社会算力产业的快速发展。以GPT大模型为例,GPT-3模型参数约为1746亿个,训练一次需要的总算力为3640PF-days(即以1PFlops算力计算3640天[ 注:Flops即每秒执行的浮点运算次数。1E Flops=10^18Flops,约为5台天河2A超级计算机或50万颗主流服务器CPU或200万台主流笔记本的算力输出。1P Flops=10^15Flops]),而新一代GPT-4模型参数量将达到1.8万亿个,算力需求提高68倍。

GPT大模型各版本训练数据量

GPT大模型各版本训练数据量

ChatGPT的轰动引发全球人工智能大模型训练及应用的浪潮,驱动算力需求进入爆炸式增长阶段。尤其是针对人工智能的智能算力,更成为了算力产业未来发展的重要方向。

今天我们将解密ChatGPT背后的算力芯片技术,算力芯片如何工作?HBM内存是什么? GPGPU /CPU/FPGA区别于优劣?一切从芯片开始。

芯片,英文Chip,又称微电路(microcircuit)、微芯片(microchip),业内的正式名称叫集成电路 (Intergrated Circuit,简称IC)。

芯片是一种集成电路,由大量的晶体管构成。不同的芯片有不同的集成规模,大到几亿;小到几十、几百个晶体管。晶体管有两种状态,开和关,用1、0来表示。多个晶体管产生的多个1与0的信号,这些信号被设定成特定的功能(即指令和数据),来表示或处理字母、数字、颜色和图形等。芯片加电以后,首先产生一个启动指令,来启动芯片,以后就不断接受新指令和数据,来完成功能。集成电路的发展路线必然是越来越小,电压越来越低,频率越来越高,功耗越来越小。

芯片的工作原理是将电路制造在半导体芯片表面上从而进行运算与处理。

集成电路对于离散晶体管有两个主要优势:成本和性能。

成本低是由于芯片把所有的组件通过照相平版技术,作为一个单位印刷,而不是在一个时间只制作一个晶体管。

性能高是由于组件快速开关,消耗更低能量,因为组件很小且彼此靠近。2006年,芯片面积从几平方毫米到350 mm²,每mm²可以达到一百万个晶体管。

数字集成电路可以包含任何东西,在几平方毫米上有从几千到百万的逻辑门、触发器、多任务器和其他电路。

算力是单位时间处理数据并得到结果的计算能力。其数值越大代表计算能力越强。算力常用单位是每秒执行浮点数运算的次数( FLOPS )。

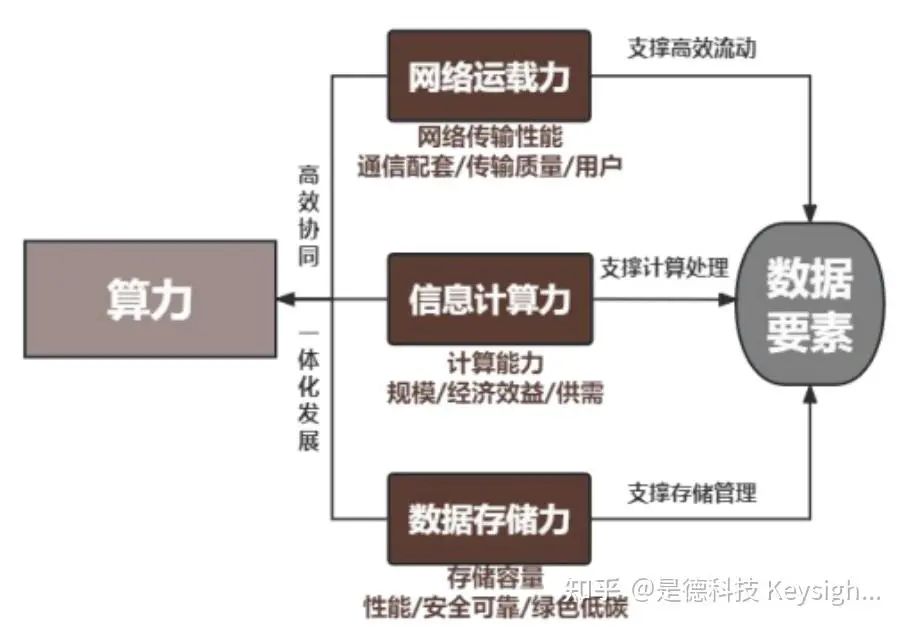

算力是集信息计算力、网络运载力、数据存储力于一体的新型生产力,促进新产业、新业态、新模式不断涌现,引领算力产业乃至数字经济的高质量发展。算力可分为通用计算能力、智能计算能力和超级计算能力。当前算力产业的两大驱动力:数字化转型驱动算力成为产业竞争关键力量,人工智能大模型驱动算力需求爆炸式增长。

算力概念

算力概念

网络运载力 (Network Power)是以网络传输性能为核心、支撑数据要素高效流动。在东数西算背景下,运载力是赋能数字经济的关键力量,是优化算力供需关系的关键,是连接用户、数据和算力的桥梁。

数据存储力 (Storage Power)是以存储容量为核心、支撑数据存储和管理。存储力是支撑大数据时代的核心力量,是迅速访问信息、推动信息资源共享的基石。在数字经济快速发展的背景下,数据呈指数级增长,存储力作为承载数据的关键设施,重要性日益凸显。

AI芯片算力的计算方法

1. FLOPs (每秒浮点运算次数)

FLOPS (Floating-point operations per second; 缩写:FLOPS, 1ops 或者 1lop/s)即每秒所运行的浮点运算次数。浮点 (loating-point),指的是带有小数的数值浮点运算即是小数的四则运算,常用来测量电脑运算速度或被用来估算电脑性能,尤其是在使用到大量浮点运算的科学计算领域中。

通常,FLOPs越高,芯片的算力就越强大。计算AI 芯片的 FLOPs,需要统计其浮点运算的数量,并除以单位时问。

因为FLOPS后缀的那个S代表秒,而不是复数,所以不能够省略。在多数情况下,测算FLOPS比测算每秒指令数 (IPS)要准确。是衡量芯片算力的常用指标之一。它表示芯片每秒能够执行的浮点运算次数。

区分 FLOPS 和 FLOPs

每秒浮点运算次数 (floating point operations per second, FLOPS ),即每秒所执行的浮点运算次数,是一个衡量硬件性能的指标。

下面列举了常见的 FLOPS换算指标

一个 KFLOPS (kiloFLOPS)等于每秒一千(103) 次的浮点运算;

一个 MFLOPS (megaFLOPS)等于每秒一百万(106)次的浮点运算;

一个 GFLOPS (gigaFLOPS)等于每秒十亿(109) 次的浮点运算;

一个 TFLOPS (teraFLOPS) 等于每秒一万亿 (1012) 次的浮点运算;

一个 PFLOPS (petaFLOPS)等于每秒一千万亿(1015) 次的浮点运算;

一个 EFLOPS (exaFLOPS)等于每秒一百亿亿(1018)次的浮点运算。

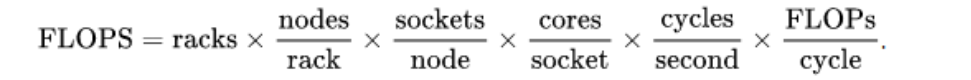

FLOPS在高性能计算机集群(超算)上可以用这个公式计算:

此外,从 FLOPs 延伸出另外一个指标是乘加运算量MACs。

2. MACs (乘加运算次数)

乘加运算量 (multiplication and accumulation operations, MACs )是指乘加运算的次数,也是衡量深度模型计算量的指标。它表示芯片每秒能够执行的乘加运算次数。在深度学习中,卷积神经网络是常用的模型,而卷积操作中的乘加运算是计算的主要部分。因此,MACs 能够更准确地反映芯片在深度学习任务中的算力。

在Intel AVX指令中,扩展了对于 乘加计算 (fused multiply-add, FMA )指令的支持,即在支持AVX指令的CPU上,可以通过FMA计算单元使用一条指令来执行类似

的操作,参考 Intel® C++ Compiler Classic Developer Guide and Reference

(https://www.intel.com/content/www/us/en/resources-documentation/developer.html)

中对于 _mm256_fmadd_ps 指令的介绍。一次乘加运算包含了两次浮点运算,一般地可以认为 MACs = 2FLOPs。

的操作,参考 Intel® C++ Compiler Classic Developer Guide and Reference

(https://www.intel.com/content/www/us/en/resources-documentation/developer.html)

中对于 _mm256_fmadd_ps 指令的介绍。一次乘加运算包含了两次浮点运算,一般地可以认为 MACs = 2FLOPs。

计算力分为通用计算能力、智能计算能力和超级计算能力。

通用算力 又称基础算力,是以CPU芯片输出的计算能力为主,能够在各种不同的应用场景中提供广泛、高效、稳定的计算能力,也是目前最常见的算力类型。近年来,随着社会数字化转型加速、数据处理需求增长,我国数据中心与云计算产业快速发展,提供通用算力的数据中心或云计算服务相对成熟,在社会各个行业快速落地。在需求端,互联网行业是通用算力最大需求市场,占比达到39%,其次是电信、政府、服务、金融、制造、教育、运输。

智能算力 以GPU、FPGA、 AI芯片 等加速芯片输出的人工智能计算能力为主,是专门为支持人工智能算法和应用而设计和优化的计算能力。在需求端,互联网行业的数据处理和AI模型训练的需求在智能算力占比高达53%,服务行业的智能化升级需求占比第二,其后是政府、电信、制造、教育、金融、运输。

超算算力 以超级计算机输出的计算能力为主,通过分布式高性能集群计算系统进行大规模计算任务,解决科学研究等领域的复杂计算问题。超算是国家综合锅里的重要体现,诸多基础科学领域的研究都离不开超算算力的支持。

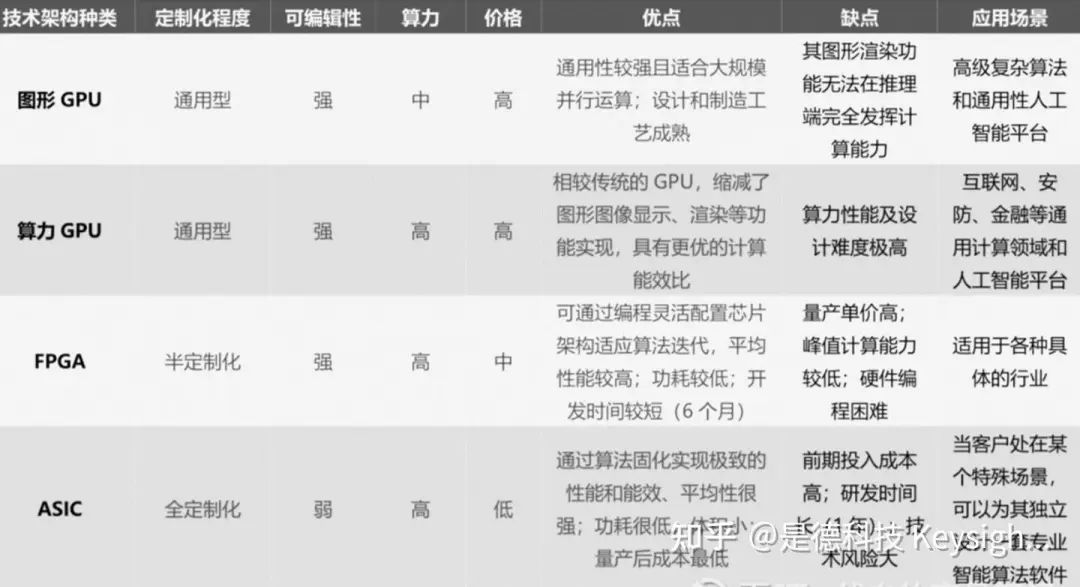

GPU, FPGA和ASIC这三类芯片有何区别呢?

● GPU是一种专门在电脑 、游戏机和一些移动设备上图像运算工作的微处理器,与CPU类似,也是游戏玩家口中熟悉的“显卡”。GPU设计初衷是专门处理执行复杂的数学和几何计算,也是图形渲染的基础。

● FPGA是可编程集成电路 ,是一种能完成任何数字器件的功能的芯片,甚至是高性能CPU都可以用FPGA来实现。但是一切实现都取决于对于FPGA的功能是如何设计的。

● ASIC是专用集成电路 ,是指按照特定用户要求设计、制造的集成电路,其绝大部分软件算法都固化于硅片。一般来说,ASIC具备低功耗、高性能的特点,但其研发投入较大。

算力是为大数据的发展提供基础保障,而算法的核心在芯片。承载算力的集成电路称为算力芯片。

算力芯片是一种新的计算机体系结构,旨在为超级计算机提供更加可靠的计算能力。该概念的最大创新点是它在同一块芯片上集成了多个核心,使其能够并行执行多重运算任务。除此之外,算力芯片还能支持虚拟机,实现高效调度,减少计算资源的浪费,更快地完成任务。

算力芯片是以架构的方式组织的多核心计算机,由多个晶体管和门元件组成,每个核心由完全独立的控制机和数据通道组成。当多个算力芯片连接在一起时,它们构成一个系统,共同完成不同的任务,为计算机带来更强大的性能。

算力芯片采用了独特的多核心设计,使得其执行多线程任务,可以提高处理能力,让单线程任务也可以发挥较强的性能。此外,它还支持一些新的处理单元,如内存访问单元、浮点运算单元和存储控制器,可以支持更复杂的多媒体应用,使应用软件得以更加可靠、高效地执行。

算力芯片可以提供计算机处理能力的巨大提升,尤其是大型算力芯片,它们可以搭配高性能系统,实现多核心处理器的共享资源调度,有效地增加系统的吞吐量,以及降低系统的延迟。另外,对于对服务器虚拟化技术的支持也是算力芯片的一项重要功能。虚拟化技术可以实现服务器的虚拟化,虚拟机可以在算力芯片上运行,而不必牺牲系统性能,大大减少了服务器的资源浪费,有效提高系统的处理能力。

算力芯片按处理信号种类分为光子芯片与电子芯片。光子芯片和电子芯片是两种不同的芯片技术,它们在信息传输和处理方面有着不同的特点和应用场景。

光子芯片和电子芯片的区别

电子芯片:电子芯片是基于电子技术的芯片,使用电子信号进行信息传输和处理。它通过电流的流动来实现信号的传输和处理,具有较高的速度和精度,适用于大规模数据处理和计算任务。

- 精度高:电子芯片可以实现精确的信号处理和计算,适用于复杂的数据处理任务。

- 成熟稳定:电子芯片技术经过长时间的发展和应用,具有成熟的制造工艺和稳定的性能。

电子芯片的缺点

- 能耗高:电子芯片在高速运行时会产生较大的能耗,对电源和散热要求较高。

在传输过程中,LED 发出的光信号会被反射口来,贔体管收集这些反射回来的光信号。当晶体管接收到光信号时,它会将光信号转换为电信号,然后由硅片进行处理。处理后的电信号会被发送到贴片电路(PCB)上,然后信号会再次发送到电子设备的电路板上。然后,这些信号会被记录并储存在存储器中,供以后使用。

光子芯片的优点

- 抗干扰能力强:光子芯片对电磁干扰的敏感度较低,具有较好的抗干扰能力。

- 能耗低:光子芯片在传输过程中能耗较低,适用于低功耗和节能的应用场景。

光子芯片的缺点

- 处理能力有限:光子芯片在信号处理和计算方面相对有限,适用于特定的应用领域。

综上所述,电子芯片和光子芯片各有其优势和局限性,根据具体的应用需求和场景选择合适的技术。在高速通信和大规模数据处理方面,光子芯片具有较大的优势;而在复杂的信号处理和计算任务方面,电子芯片更具优势。

这里我们围绕数据中心、车载和消费电子领域,聚焦电子芯片,电子芯片包括 CPU、GPU、DPU 等。

传统算力(又称基础算力)来源 CPU,新兴算力(又称智能算力)来源 GPU、 DPU。

复杂网络和新兴应用(大型游戏、大数据分析、云服务、高性能计算等)对新兴算力及算力芯片提出更高要求。

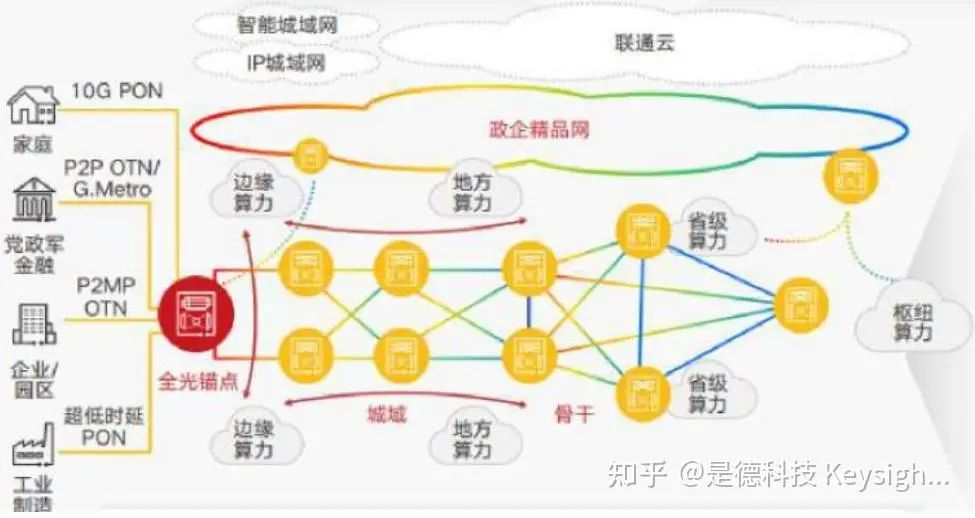

当前网络实现了全光底座,有管道特性,具备高品质连接能力。但社会信息化加速、新兴 应用涌现,光网络架构复杂、适应性差、智能化弱,需要由带宽驱动管道化网络向业务与体验 驱动的算力网络演进。算力网络需具备智能化、低时延、低抖动、低丢包、大带宽、高可靠等特点。从建设“尽 力满足需求”的传统网络转型到建设“提供高品质业务”的算力网络已提上日程。结合国家“东数 西算”工程与“全国一体化大数据”规划,加速算力网络建设。下图展示的是中国联通全光底座的算力网络架构。数据中心规划方面,建设靠近用户的全 光锚点,部署 边缘算力 ,提高用户体验;部署地方、省级算力实现地市、城市群算力统筹调 度;建设枢纽算力实现东、西部算力资源协调。网络时延方面,西部枢纽到东部远距离枢纽可 控制在小于 20ms,省与市数据中心可控制在 5ms 以内,光锚点与市数据中心可控制在 1ms 以内。计算能力方面, 数据中心拥有大量服务器和加速卡,可提供丰富算力资源。

图 1.算力网络

图 1.算力网络

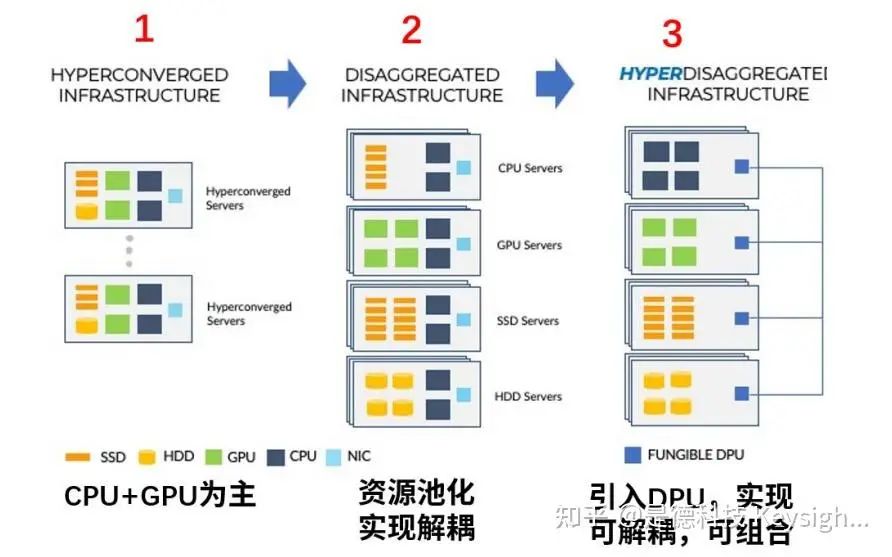

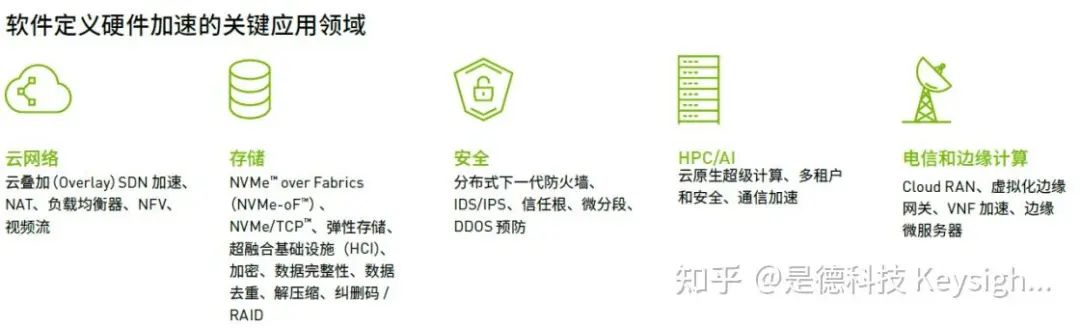

算网融合趋势下新兴应用助推以 DPU 为代表的算力芯片发展。基础设施层方面,网络接口 Ethernet、计算接口 PCIE、存储接口DDR 等快速迭代。平台层方面,可执行应用层算法或提供算力资源,按需软件定义并实现硬件加速,可解耦/组合硬件资源,方便算力调度与数据处理。

图 4.数据中心演进与 DPU 作用

图 4.数据中心演进与 DPU 作用

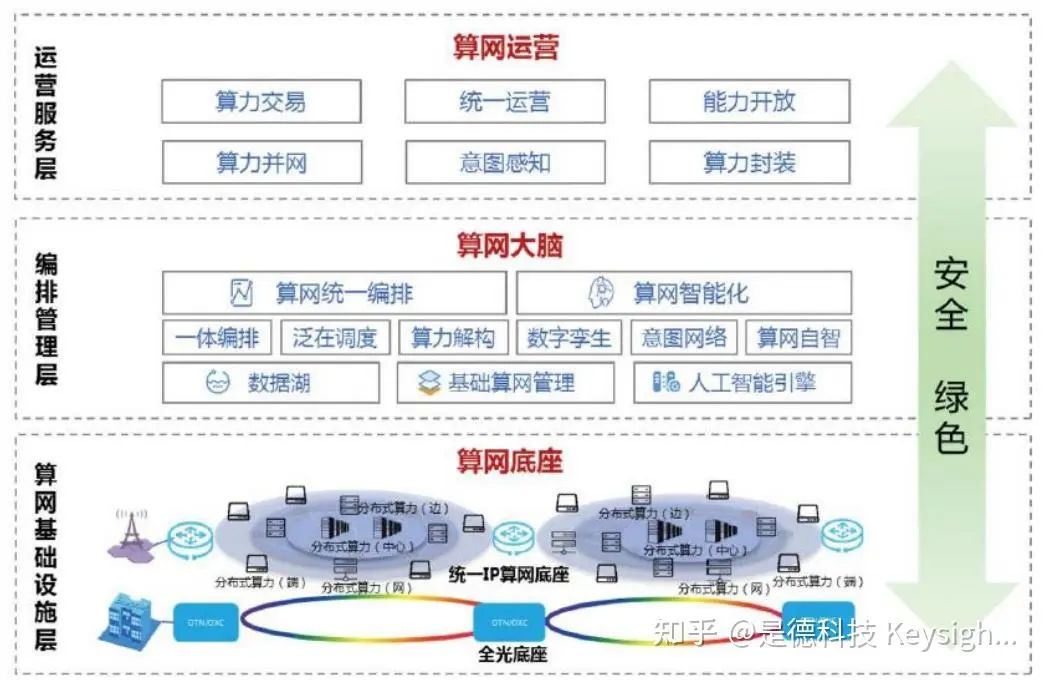

图 5.算网底座、算网大脑与算网运营

图 5.算网底座、算网大脑与算网运营

作为OpenAI研发的聊天机器人程序,支撑ChatGPT运转的可不是简单的一台机器,而是一个庞大的算力网络。这个算力网络可以抽象为三层:传输网络、计算网络和存储网络。如下图:

图:算力网络示意图

图:算力网络示意图

图:算力芯片分类

图:算力芯片分类

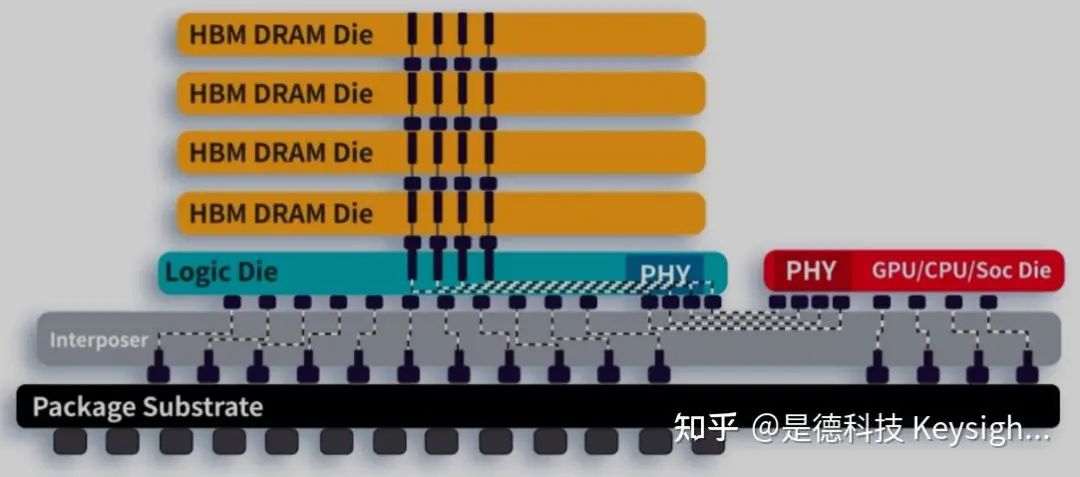

在算力网络中,GPGPU芯片要发挥性能光靠自己可不行,需要系统的配合。在这个系统内:CPU负责任务调度;GPU负责主要的算力输出,也就是计算任务;内存负责数据暂存,配合GPU进行计算。

图:算力网络芯片分工示意图

图:算力网络芯片分工示意图

图:HBM内存示意图

图:HBM内存示意图

图:内存技术发展

图:内存技术发展

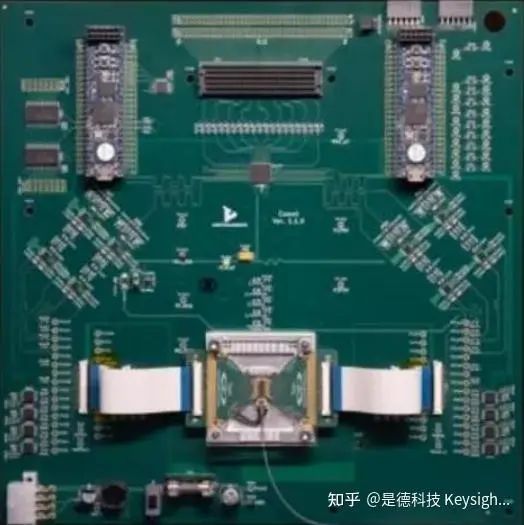

是德科技DDR5测试拓扑图

是德科技DDR5测试拓扑图

应用助推算力发展

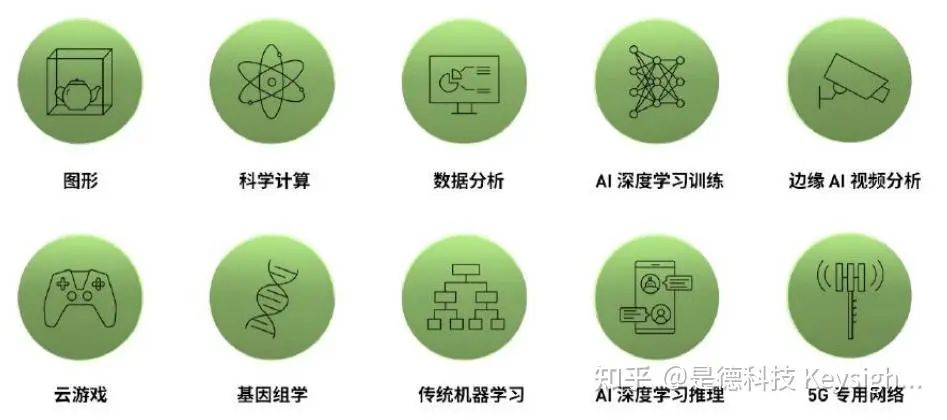

参考思科云计算白皮书(统计截止到 2020 年), 90%的流量(包括机架服务器内部数据流 量)发生在数据中心内部。应用产生了海量数据,数据传输与处理挑战很大。从数据中心网络拓扑看,传统数据中心采用三层架构,难以应对海量数据转发挑战。新 兴数据中心采用扁平叶脊两层架构,每台脊交换机可与所有叶交换机实现互连,提供多条传输 路径,提高传输效率。从核心器件性能看,传统数据中心性能与 CPU 相关。2015 年之后 CPU 性能以每年 3.5%增加,网络带宽以每年 45%增加,增速失配。新兴数据中心为解决该 问题,采用异构拓扑,多 CPU 级联,使用 GPU、DPU 等卸载 CPU 工作负载,提升性能。从 芯片架构看,CPU 遵循冯诺依曼架构,适合控制和通用计算。GPU 采用众核架构,用于图形/ 图像/视频处理、光线追踪、2D/3D 重建,可改进用于密集计算,以 Nvidia H100 GPU 为例, 可用于小型企业工作负载、百亿亿次级高性能计算、万亿级参数 AI模型,典型应用如下:

图 2.数据中心典型工作负载

图 2.数据中心典型工作负载

图 3.DPU 应用领域

图 3.DPU 应用领域

以算网基础设施物理层为分析对象,该层采用全光架构,已部署 400G,未来将演进到 800G、1.6T。

为实现更大带宽,数据中心需部署下一代服务器、交换机及光模块。以光模块为例,其涉 及高速数字和光通信技术,需进行电域和光域分析。当前电口单路 100G 在研发中,参考 IEEE 802.3ck 和 OIF CEI-112G 标准,200G 技术和标准还在讨论中。光口单路 100G,参考 IEEE 802.3db 标准,通过多路光纤或波分复用实现更大带宽。

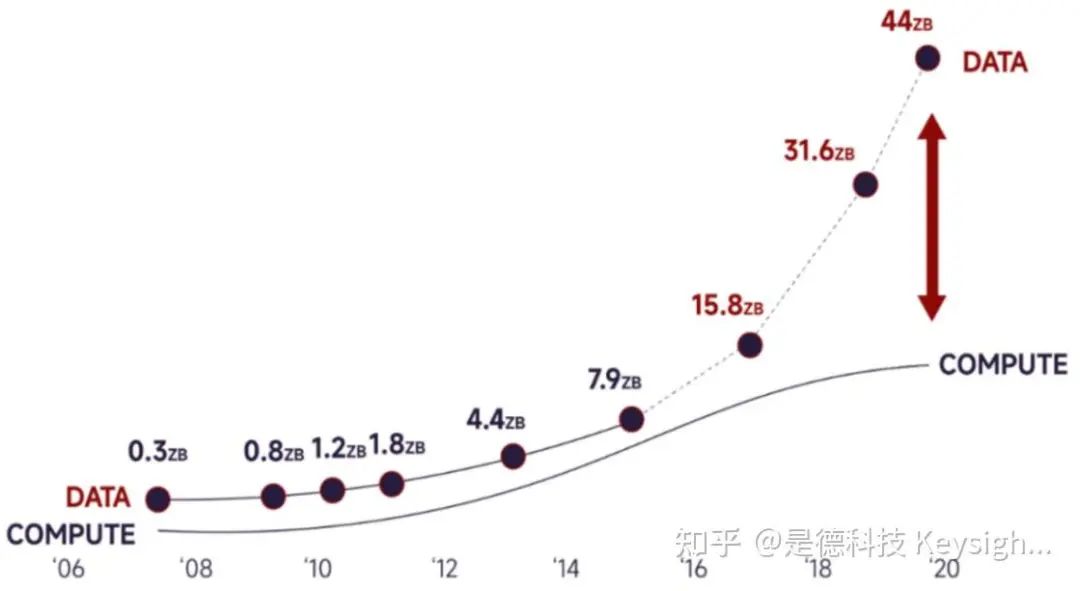

光模块随 Serdes 速率翻倍(50G~100G),其功耗会线性增加,面临散热挑战。为优化功耗,提升能效比,CPO/NPO 封装技术应用而生,通过将光引擎靠近交换芯片实现更短电连 接,降低损耗。海量数据驱动网络带宽越来越大。光模块不具备数据处理能力,仅支持简单故障管理/告警功能。数据传输到通信设备,推动了数据中心算力芯片及高速接口发展。面对海量数据几何级数的增长,传统 CPU性能和系统处理需求差异越来越大,需大算力芯片弥补。

2017、2018 年以来,人工智能兴起,算力芯片蓬勃发展。从逻辑层面看,CPU 遵循冯诺依曼架构,实现存储、取数、处理、返回,没有考虑网络、业务种类(互联网、金融、电信 等)、数据类型(音频、高清视频等)、时延、性能等。面对复杂网络、新兴应用和海量数据,CPU 通过轮询和中断实现控制、管理效率低,AI/GPU 仅考虑了数据平面功能,不够灵活,DPU 增加了控制平面和管理平面功能,主动解耦、组合硬件资源,达到按需处理网络数 据的目的。

未来算力网络会延伸至车载、消费电子领域。车载领域ADAS、Autopilot 等应用推动了 智能驾驶算力芯片发展。消费电子领域大型游戏等应用推动了智能手机 SoC 等算力芯片迭代 更新。

2、泛在算力芯片简介

如下介绍了智能终端(手机、平板)、智能座舱、智能驾驶、中央算力平台、云端计算等 多种场景算力芯片特点及发展趋势。

• 智能终端方面,其核心算力芯片是 SoC。以智能手机为例,SoC 包含 AP (CPU+GPU)和 Modem(集成或外挂)。SoC 基于 ARM 架构,64 bit 总线,多 以 6 核或 8 核进行设计与迭代。以苹果的 A16 和高通的骁龙 8+ Gen1 为例,前者 CPU 主频 3.46GHz,基于 ARM v8 架构,采用 2 核(性能核)+4 核(能效核)进 行设计,支持数据加速(16 核神经引擎/算力 17 TOPS+5 核 ISP 引擎),支持 LPDDR5,采用 TSMC N4 工艺。后者 CPU 主频约 3GHz,基于 ARM v9 架构,采 用 1 核(性能优先)+3 核(平衡效率和性能)+4 核(能效优先)进行设计,支持 融合 AI(矢量+标量+张量)加速,集成 GPU(2.2TOPS)、18-bit ISP 引擎及 DSP(52TOPS),支持 LPDDR5/USB 3.1 Gen2,采用三星 4nm 工艺。

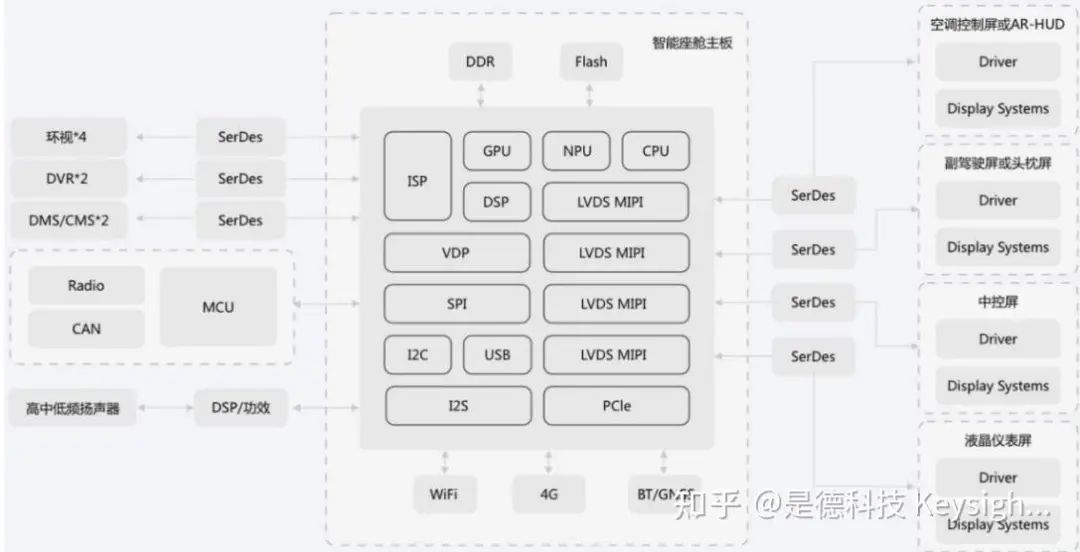

• 车载域控制器方面,比如智能座舱、智能驾驶。2017 年上海提出汽车“新四化”,推 动汽车智能化转型,汽车将成为手机、电脑之后第三大智能终端。通过智能座舱提 供第三生活空间,通过智能驾驶平台实现 L0~L5 不同等级驾驶功能,提升出行体 验。SoC 是汽车“大脑”,传感器是汽车“五官”。融合不同传感器数据实现低速智能 驾驶(自主泊车等)、高速智能驾驶及车内影音娱乐。智能座舱相比自主泊车、高 速自动驾驶更易实现。目前智能座舱可实现复杂监控,比如 360 度环视、行车记录 仪、驾驶员监控、电子后视镜,也可实现复杂显示,比如 C-HUD/W-HUD/AR-HUD 仪表盘、中控显示屏、副驾/后舱娱乐屏(4K 高清屏)等。在“一芯多屏”趋势下,算 力芯片性能不断提升。以 SA8155AP 为例,它集成了(64-bit/ 8 核/7nm 工艺) CPU、(1.1 TFLOPS)GPU 和 DSP,拥有图像识别与面部探测能力的 ISP,支持 4K 多点触屏显示器,有 1 路原生 DP 接口和 2 路 DSI 接口(可连到 DP 桥),支持 LPDDR4X、UFS3.0、USB3.0、8 路摄像头输入接口。

图 6.智能座舱简化框图

图 6.智能座舱简化框图

图 7.Horizon Matrix 智能驾驶简化架构

图 7.Horizon Matrix 智能驾驶简化架构

表 1.上市量产车智能驾驶算力

表 1.上市量产车智能驾驶算力

图 8.算力与数据增速趋势

图 8.算力与数据增速趋势

终端、边缘端和云端都集成了算力芯片。

终端 SoC 处理器加入了计算功能。以智能网联汽车为例,其域控制器架构向着区域控制 器(Zontal 架构)方向演进,采用中央算力平台。该平台使用高算力芯片,比如 Nvidia 的车 载算力芯片 Thor,可以提供 2000TOPS 算力。

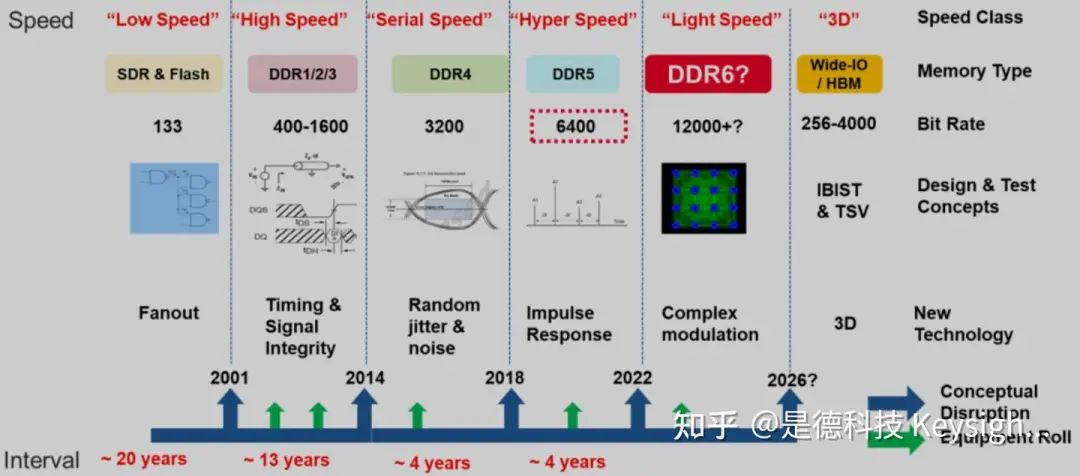

边缘端和云端广泛部署加速卡实现密集计算。加速卡的高速数字接口和网络接口向着第 5 代 IO 演进,分别是 PCIE5/DDR5 和 100G 以太网,接口每 2-3 年速率翻倍,下一代 PCIe6 和 200G 以太网也在讨论中。

• 性能与能效比提升带来芯片设计挑战。终端算力芯片 SoC 通过不同功能的多核组合 方式(有的核负责性能+有的核负责性能与能耗平衡+有的核负责能效)实现;

• 芯片及板级验证面临的物理层信号质量、协议层业务数据挑战

速率提升带来信号完整性挑战。以太网技术由 25G、50G 发展到 当前单路 100G 及未来 200G。高速数字 IO 技术,比如 PCIE、DDR、USB 等 也在快速演进,PCIE5.0 已经发布,PCIE6.0 采用 PAM4 调制格式实现单 lane 64Gbps,芯片 Base 规范已经发布,PHY Test 规范在讨论中。DDR5 相比 DDR4 数据速率提升至 8400MT/s,内置多抽头 DFE,DDR6 规范还未发布, 可能采用 PAM4 技术,提升比特速率。USB4 近期也发布了 v2 版本,采用 PAM3 调制格式提升数据速率。速率提升引起码间干扰、串扰等,导致眼图压 缩,给收发侧均衡设计带来挑战。技术参数变化带来验证挑战。相比 NRZ,采 用高阶调制 PAM3/4,无法通过手动设置完成所有测试。增加了 SNDR、JnU 等参数,需要进行复杂设置和后处理才能完成。

PCIE 不仅包括物理层,而且包含数据链路层和事务层。面对主 板与插卡进行业务通信时无法建立连接、业务出现故障等问题,通过探头采集 信号,非常困难。需借助 PCIE 协议分析仪监控 x4/x8/x16 的上行和下行链 路,借助解析软件,浏览数据包,检查合规性。

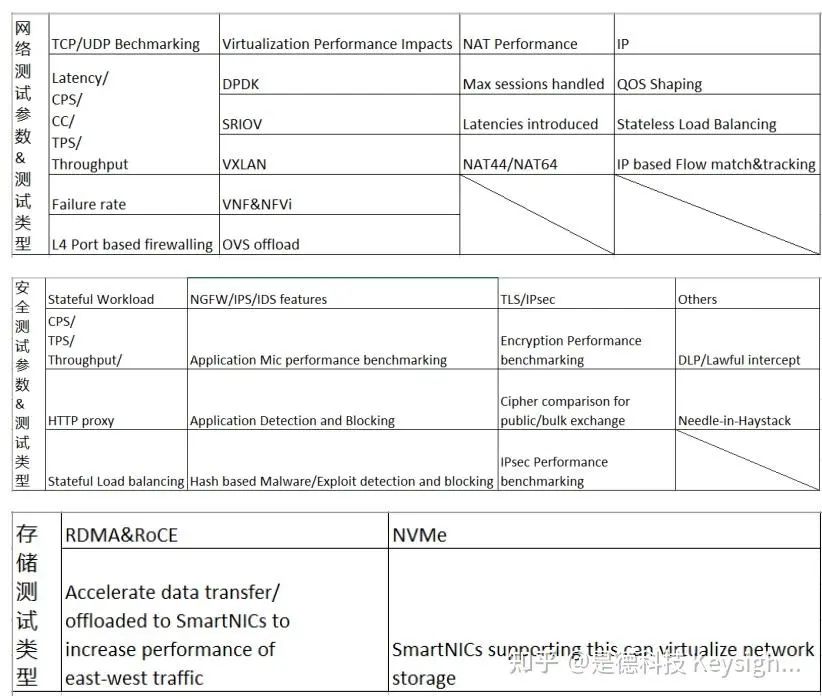

• 网络协议复杂,挑战很大。数据中心 DPU 卡需兼容不同服务器主板、卸载 CPU 工作负载,满足数据传输与处理要求,需进行网络测试、安全测试及存储测试。网络 测试包括基于 TCP/UDP 包的测试、虚拟化性能影响测试、网络地址转发性能测 试、IP 相关测试,安全测试包括有状态 TCP/HTTP 工作卸载验证、NGFW/IPS/IDS 特性测试、TLS/IPsec 测试等,存储测试包括 RDMA、RoCE、NVMe 测试。测试 用例繁多、非常复杂(存储测试中 RoCE 需要用到协会专用软件)

图 9.上层协议测试用例

图 9.上层协议测试用例

参考文献:

[2]:算力时代的全光底座白皮书.作者:中国联通研究院

[3]:https://www.nvidia.cn/

[4]:算力网络白皮书.作者:中国移动通信集团有限公司

[5]:https://www.hisilicon.com/cn/scenario/mobility/e-cockpit

[6]:https://www.horizon.ai/superdrive.html[7]:https://www.ctsec.com