10nm后,DRAM有这些发展方向

【导读】半导体公司正在推动 DRAM 的进步,突破性能、密度和效率的界限。这是最近的一些例子。动态随机存取存储器(DRAM) 长期以来一直是现代计算必不可少的,为各种应用程序提供快速和易失性存储。然而,随着对性能和内存密度的需求不断上升,DRAM 面临着缩小到 10 nm 工艺甚至超过 10 nm 工艺的挑战。

半导体公司正在推动 DRAM 的进步,突破性能、密度和效率的界限。这是最近的一些例子。

动态随机存取存储器(DRAM) 长期以来一直是现代计算必不可少的,为各种应用程序提供快速和易失性存储。然而,随着对性能和内存密度的需求不断上升,DRAM 面临着缩小到 10 nm 工艺甚至超过 10 nm 工艺的挑战。

尽管存在这些障碍,DRAM 制造商仍继续通过创新方法突破界限。本文讨论了 DRAM 行业的一些新进展,并探讨了推动这些存储器进步的技术。

首先,为什么 DRAM 很难扩展?

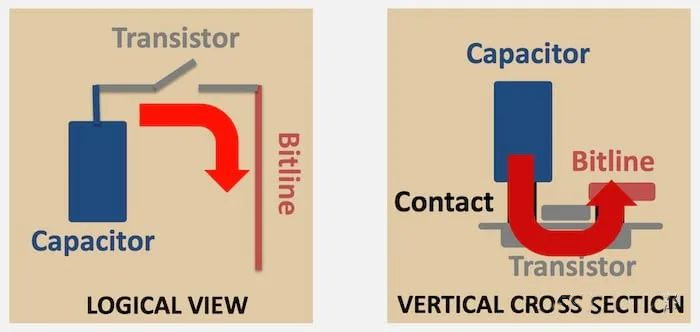

扩展 DRAM 的主要问题之一是降低单元电容,这会影响内存密度和数据保留。DRAM 制造商采取了各种策略来处理这个问题。一种方法是使用高级材料,例如高 k 电介质,它可以增强单个cell、的电容。

该技术的一个重要发展是三维 (3D) 集成。通过垂直堆叠多层存储单元,制造商绕过了横向尺寸缩小 10 纳米所施加的限制。这种垂直架构对于扩展至关重要,因为多层不会影响性能。

先进的光刻方法也有助于 DRAM 缩放。新技术,如极紫外 (EUV) 光刻,已经出现以克服传统光学光刻的局限性。它们使制造商能够实现更精细的尺寸并提高 DRAM 单元的整体性能。除了先进的材料、集成和光刻之外,开发人员已经证明,创新的电路设计和制造工艺也可以在解决 DRAM 尺寸方面发挥不可或缺的作用。以下是一些公司这样做的例子。

三星的 12 纳米 DRAM 和第一款 CXL DRAM

多年来,三星一直是 DRAM 行业的主要参与者。最近,该公司在其 12 纳米 DRAM 和业界首款 CXL(Compute Express Link)DRAM 方面取得了重大进展。

据三星称,新的16 GB、12 nm DDR5 DRAM具有精致的电路、优化的单元结构和低工作电压,可将功耗降低多达 23%,同时将晶圆生产率提高多达 20%。它的最高速度为 7.2 Gbps,这是通过有助于增加cell电容的新型高 κ 材料实现的。高电容使其更容易区分数据信号并降低噪声。

去年 12 月,三星成功评估了其 16-GB DDR5 DRAM 与 AMD 的兼容性,目前正在与全球 IT 公司合作,以推动其在下一代 DRAM 市场的创新。

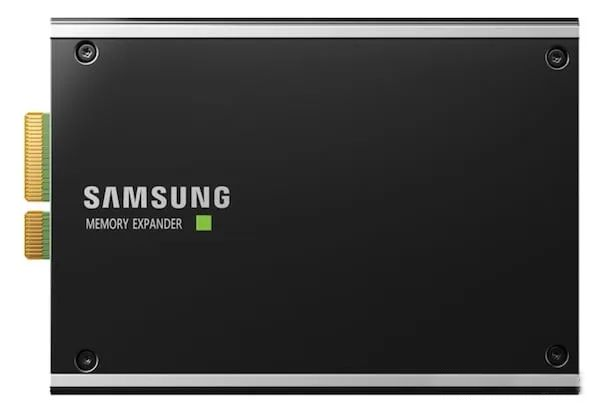

凭借其基于 CXL 2.0 构建的首款 128 GB CXL DRAM,三星旨在弥合内存与高性能计算之间的差距。它支持 PCle 5.0 接口(x8 通道)并提供高达每秒 35 GB 的带宽。此外,据说该设备支持动态内存分配、高效数据移动和共享内存池,使开发人员能够针对特定应用程序需求优化内存资源。

内存池涉及在服务器平台上绑定多个 CXL 内存块以形成池,并允许主机根据需要从块中分配内存。这种方法最大限度地提高了效率并降低了运营成本。

美光将通过 EUV 光刻技术在日本扩展 DRAM

美光、SK 海力士和其他行业领跑者等制造商认识到极紫外 (EUV) 光刻技术在推动其 DRAM 产品组合方面的关键作用。美光在 EUV 光刻技术上进行了大量投资,因为它具有出色的分辨率,能够在 DRAM 单元内创建更小、更精确的特征。

美光科技已宣布计划 首次在日本引入 EUV 光刻技术,以制造其下一代 DRAM,即 1-gamma (1γ) 节点。1-gamma 节点跟在1-beta 节点之后,这是当今最先进的 DRAM 节点之一,美光在其广岛工厂大量生产。该公司相信 EUV 技术将带来更快、更节能和更高性能的内存产品。它计划从 2025 年起在台湾和日本生产 1-gamma 节点。

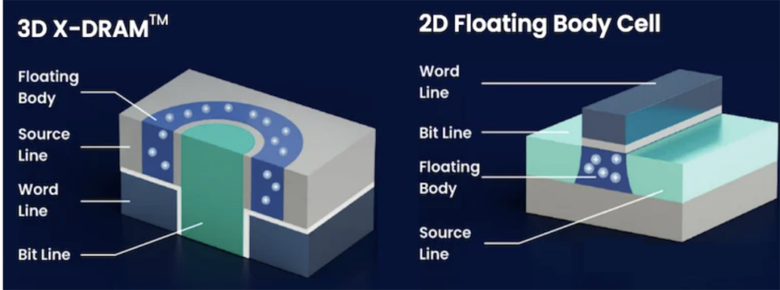

NEO Semiconductor 创造 3D X-DRAM

虽然内存领导者在 DRAM 领域占据主导地位,但像 NEO Semiconductor 这样的初创公司正在通过采用 DRAM 技术的创新方法取得重大进展。特别是,NEO Semiconductor 最近推出了一项名为 3D X-DRAM 的技术,该技术利用 3D 集成来克服传统 DRAM 的局限性。

(来源:内容由半导体行业观察(ID:icbank)编译自allaboutcircuits)

推荐阅读:

本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。