Agile Analog,模拟IP创新者,推出了其数字标准元件库(DSCL)。它提供了一个全面的数字元件库,使设计人员能够实现控制混合信号解决方案中模拟模块所需的数字电路。新的数字库可用于厚氧化物的电池,操作于核心电压域以上以及最大限度地减少泄漏,即使在FINFET技术中,也允许在不同的工艺节点之间轻松迁移

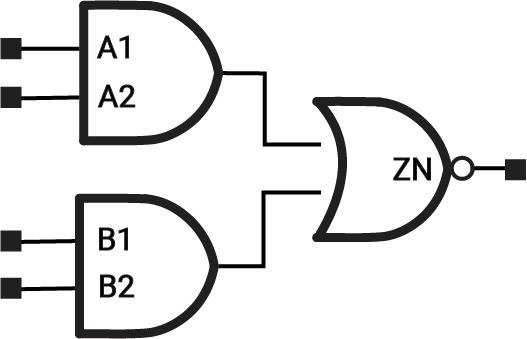

AND-OR

Agile Analog首席执行官Barry Paterson解释说:“Agile DSCL的开发使我们的客户能够在模拟领域中嵌入数字功能。这些数字单元将在模拟电压域内工作,从而避免了过多的电平偏移到核心域,并使数字控制能够紧密耦合到模拟IP。DSCL已被开发为与过程无关,因此可用于与我们的模拟IP相同的过程。该库通过提供所有必需的视图,完全支持行业标准的数字设计方法。我们的模拟数字单元库已成功用于客户设计,以支持物联网等应用的低功耗、始终在线的解决方案。

DSCL IP 模块可针对低功耗、超低泄漏、高密度或高速应用进行优化。有通道长度和各种轨道高度的选项,为设计人员提供灵活性。对于特定的设计目标,如低功耗设计,有一个特殊的电源管理库。该库可以针对其他PPA目标进行优化,以确保客户为其应用提供最佳解决方案。 还可以在定制的PVT角生成模型。该库具有一流的验证,并经过 DFM 优化。

ComposaTM

传统上,模拟IP模块必须针对每种应用和工艺技术进行手动重新设计,但Agile AnalogTM具有自动生成模拟IP的独特方式,以完全满足客户的规格和工艺技术。它被称为ComposaTM,它使用公司Composa库中经过试验和测试的模拟IP电路。实际上,数字IP的 “一次设计,多次重用” 的模式现在首次应用于模拟IP。由于Composa库中的模拟IP电路已在以前的设计中进行了广泛的测试和使用,并且每次生成时都经过全面验证,因此这为数字IP世界的“硅验证”提供了类似的保证。所有主要代工厂都得到支持,包括TSMC,GlobalFoundries,Samsung Foundry和SMIC以及其他IC代工厂和制造商。