PCB设计13——FLASH和DDR高速PCB布线布线设计规范

链接:

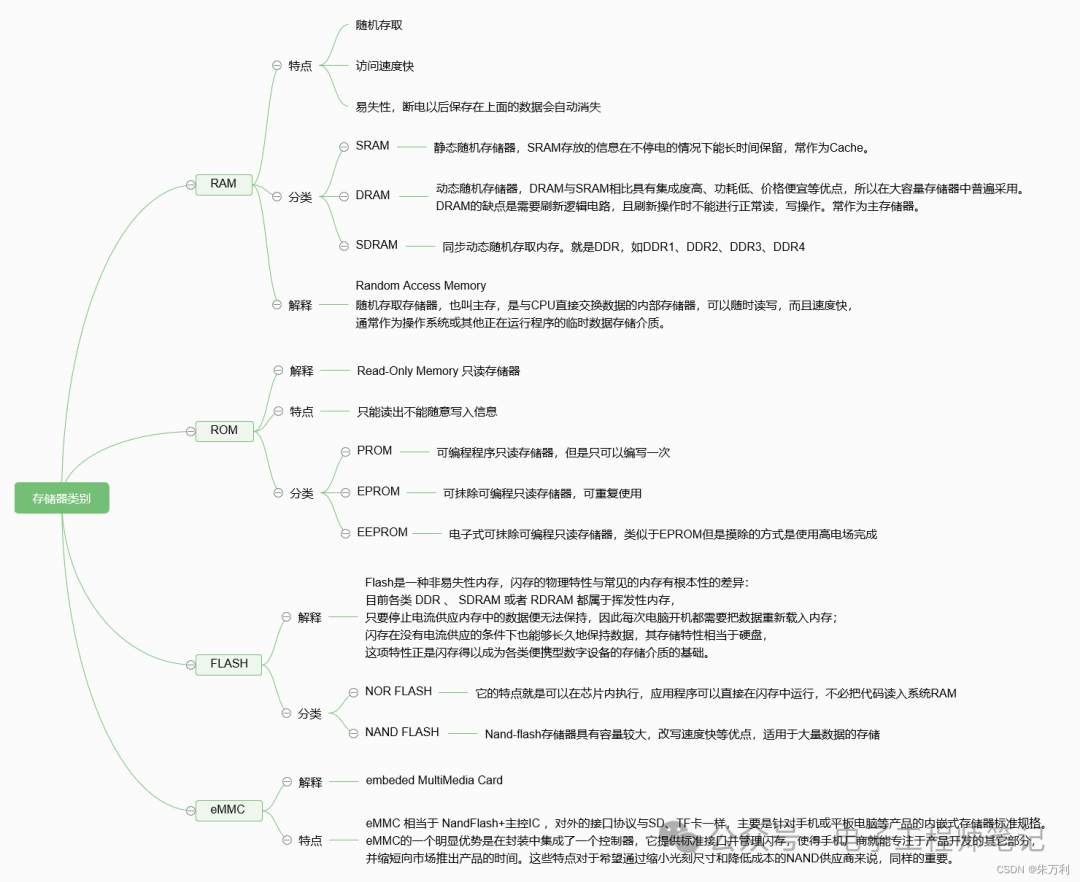

ROM、RAM、FLASH、DDR、EMMC百科

一、Flash高速PCB布局布线设计规范

1、Flash介绍

目前Flash主要有两种NOR Flash和NADN Flash

NOR Flash的读取和我们常见的SDRAM的读取是一样的,用户可以直接运行加载在NOR FLASH里面的代码,这样可以减少SRAM的浪费从而节省了成本。

NAND Flash没有采用内存的随机读取技术,它的读取一次读取块的形式来进行的,通常是读取一次512个字节,采用这种技术的Flash比较便宜。

一般容量小使用NOR Flash,因为其读取速度快,多用于存储操作系统等信息,

而容量大的用NAND FLASH,最常见的NAND FLASH重要应用是嵌入式系统采用的DOC(Disk On Chip)和我们通常使用的的“闪盘”,可以在线帐篷。

FLASH:是一种非易丢失性内存,其物理特性与常见的内存有根本性的差异:

目前各类DDR、SDRAM或RDRAM都属于挥发性内存,只要停止电流供应内存中的数据便无法保持,因此每次电脑开机都需要把数据重新装入内存;损坏在没有当前供应的条件下也能够长久地保存数据,其存储功能相当于硬盘,这个功能那么就会成为通用便携式数字设备

NOR FLASH:它的特点就是可以在芯片内部执行,应用程序可以直接在中运行,不必把代码读入系统RAM。

在1~16M下的小容量有很大的

设备

成本效益,但是低的读取和读写速度很大程度上影响了它的性能。

他的读取和我们常见的SDRAM的读取是一样的。

NAND FLASH:Nand-flash存储器容量增大,改写速度快等优点,适用于大量数据的存储,如嵌入式产品包括数码相机、MP3随身听记忆卡、体积紧凑的U盘等。

读取一次读取数据形式来进行的,通常是一次读取取512个字节。

用户不能直接运行NAND Flash上的代码,因此大多使用NAND Flash还作一小块NOR Flash来运行启动代码。

2、NOR和NAND性能比较

FLASH 是不易丢失的存储器,可以称为块的存储器单元块进行擦写和再编程。任何 flash 器件的写入操作只能在空或已布局的单元内部进行,所以大多数情况下,在NAND器件执行功耗操作必须十分简单的,而NOR则要求在进行功耗之前先执行功耗目标块内所有的位都写为1。

由于读写NOR器件时需要64~128KB的块进行的,执行一次写入/执行操作的时间为5s,与此相反,导致NAND器件需要8~32KB的块进行的,相同的操作最多只需要4ms。

执行分区大小的不同进一步拉大了NOR和NADN之间的性能差距,统计表明,对于给定的一套写入操作(尤其是更新小文件时),更多的分区操作必须在基于NOR的单元中进行。这样,当选择存储解决方案时,设计者必须权衡以下的各项参数:

● NOR的读取速度比NAND稍快一些。

● NAND的写入速度比NOR快很多。

● NAND的4ms速度远比NOR的5s快。

● 大多数写入操作需要先进行布局操作。

● NAND 的布局单元更小,相应的布局电路更少。

(注:NOR FLASH SECTOR 喷嘴时间视品牌、大小不同而不同,比如,4M FLASH,有的 SECTOR 喷嘴时间为 60ms,而有的需要最大 6s。)

3、 NAND Flash的用途

HDD是指硬盘机械,是传统的普通硬盘,包括:盘片、磁头、磁盘旋转轴及控制电机、磁头控制器、数据转接器、接口、硬盘。

SDD(Solid State Drives)是SSD硬盘,包括:控制单元、存储单元(DRAM芯片/FLASH芯片)。

区别:HDD是机械式查找数据,所以防震远低于SSD,数据查找时间也远低于SSD。

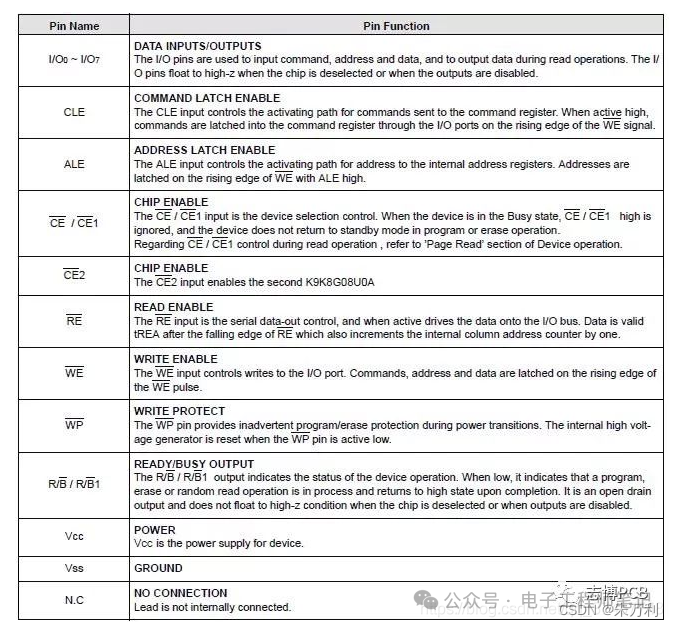

4、FLASH管脚定义

根据上图

翻译

如下:

-

I/O0 ~ I/O7:用于输入地址/数据/命令,输出数据。

-

CLE:Command Latch Enable,命令锁存使能,在输入命令之前,要先在模式注册中,设置CLE使能

-

ALE:Address Latch Enable,地址锁存使能,在输入地址之前,要先在模式注册中,设置ALE使能

-

CE#:Chip Enable,芯片使能,在操作Nand Flash之前,要先选中此芯片,才能操作

-

RE#:读使能,读使能,在读取数据之前,要先使CE#有效。

-

WE#:写使能,写使能,在写取数据之前,要先使WE#有效。

-

WP#:写保护,写保护

-

R/B#:Ready/Busy Output,就绪/忙碌,主要用于在发送完成编程/刷新命令后,检测这些操作是否完成,忙碌表示编程/刷新操作仍在进行中,就绪表示操作完成。

-

Vcc:Power,电源

-

Vss:地面,接地

-

NC:Non-Connection,未定义,未连接。

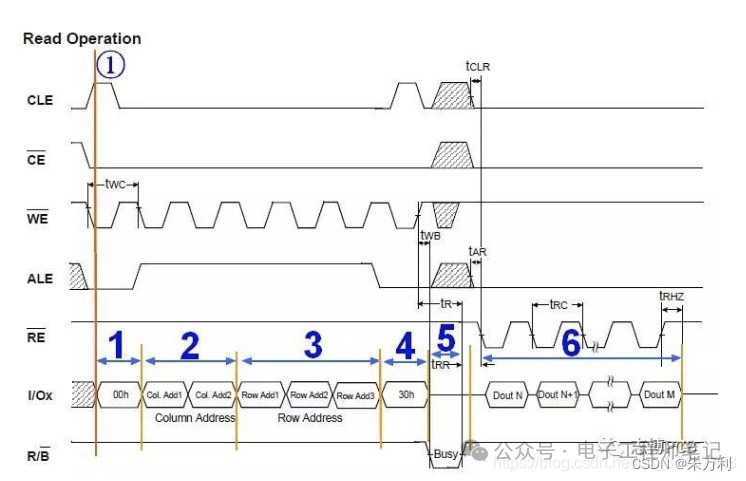

5、Nand Flash数据读取操作的操作图

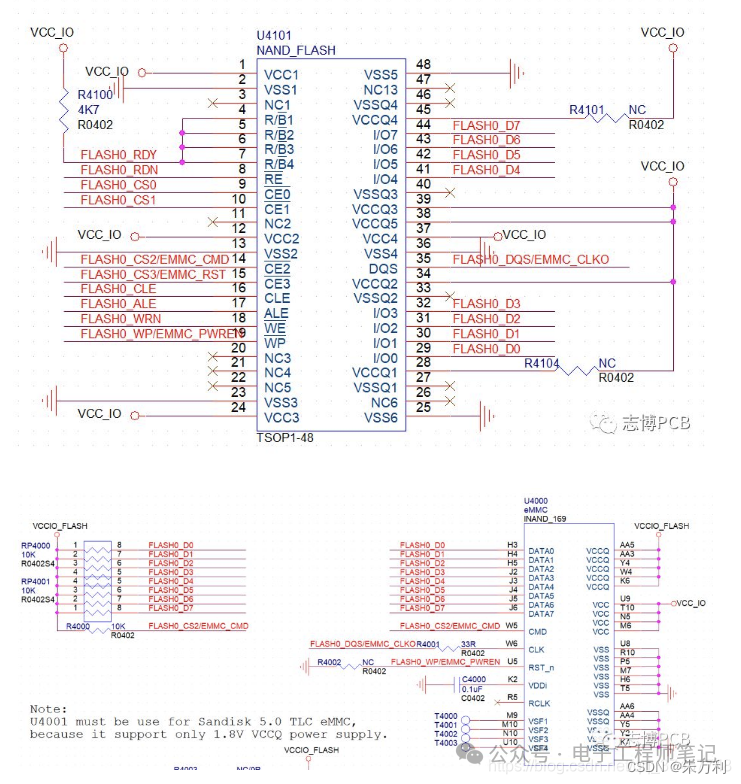

6、FLASH参考原理图

七、PCB布线布线设计指南

1)布局:

(1) NAND应接近主控存储器;

(2)去耦电容均接近NAND 盒;

(3)RE、WE、DQS 信号串接电阻接近主控盒,串阻与主控连接走线距离≤300m;

2)信号线走线要求:

(1) NAND与主控走线间走线≤2000mil;

(2) 走线连接器50欧;

(3)线间距≥2倍线宽;

(4) D0~D7、 RE、 WE 相对于 DQS 做等长,控制≤300m;

(5)D0~D7上使用过孔的数量大致相同;

(6)坚决保证走线参考页面完整;

(7)走线触及高频信号;

(8)VCC/VCCQ线宽不小于12m,或直接用敷铜代替电源走线;电源线上若过孔,则过孔数量明显于2个,避免过孔限流影响供电;

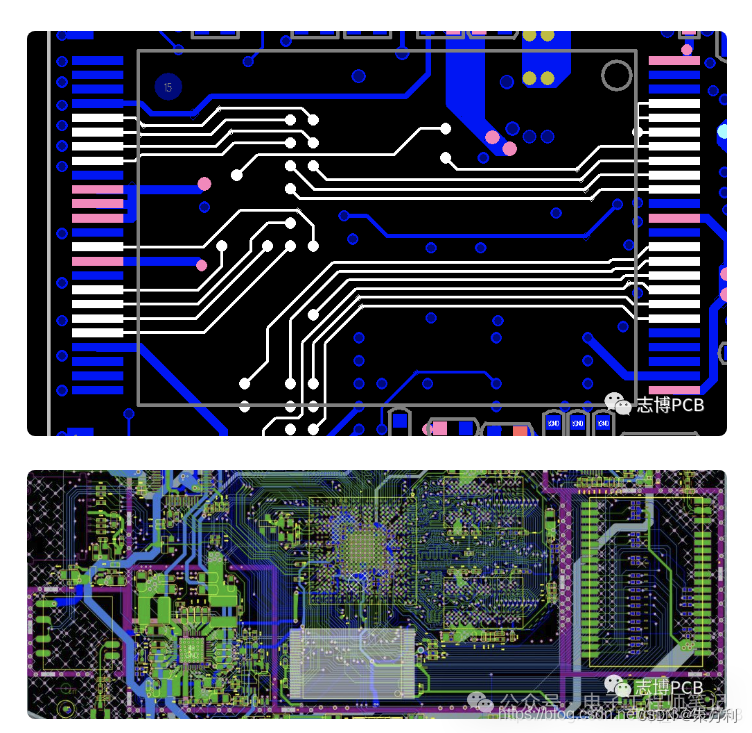

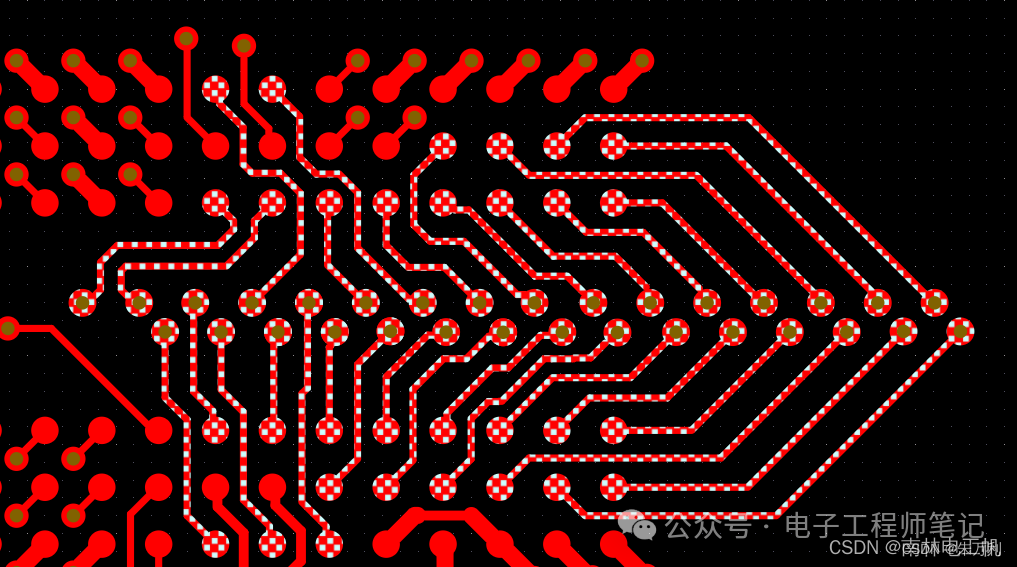

FLASH实战案例展示

二、DDR高速PCB布线布线设计规范

1、DDR是什么?

DDR=Double Data Rate习惯上双倍速率,DDR SDRAM=双倍速率同步动态随机存储器,人们称之为DDR,其中,SDRAM 是Synchronous Dynamic Random Access Memory的缩写,即同步动态随机存取存储器。而DDR SDRAM是Double Data Rate SDRAM 的缩写,是双倍速率同步动态随机存储器的意思。DDR 内存是在 SDRAM 内存基础上发展而来的,仍然沿用 SDRAM 生产体系,因此对于内存厂商而言,只需对制造普通 SDRAM DDR

的

一些工作条件:

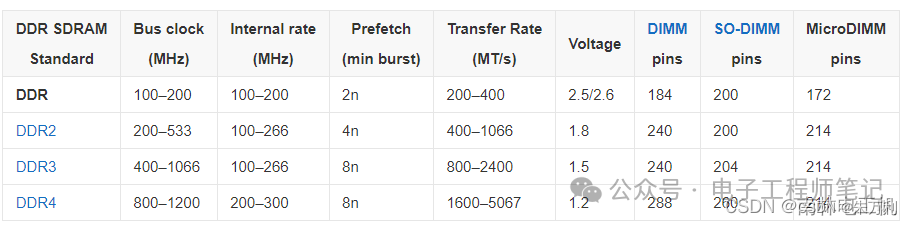

还是可以看出,随着DDR的更新换代,时钟时钟频率越来越高,并且传输速率也越来越快,工作电压越来越低,逐渐向着低功耗、高速率的方向发展,这也为DDR布线布局带来了更高的阻抗匹配要求。

2、DDR的引脚定义

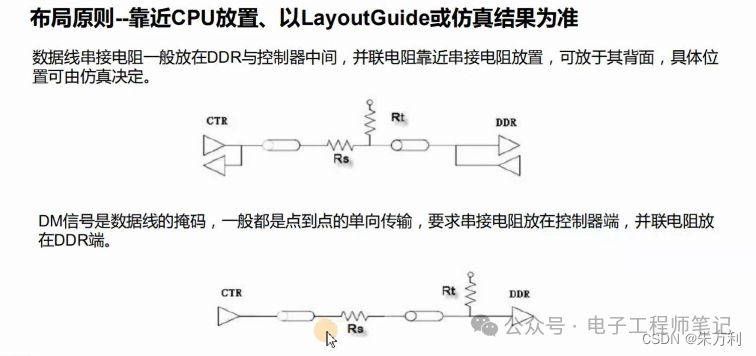

下图是一般的DDR引脚定义,可以将DDR的引脚划分为三类,第一类为电源线,VDDQ、VSSQ、VDD、VSS、VREF均为电源线;

第二类为数据线,由高低8位数据线为一组,D0-D7+LDM+数据评分对D8-D15+UDM+数据评分对组成,一般11条线为一组数据线;

第三类为地址线,去掉数据线和电源线路,余下部分都统一划分为地址线,有完善的时钟计时。

3、DDR的PCB布局规则

可以按照DDR的个数分别进行布局:

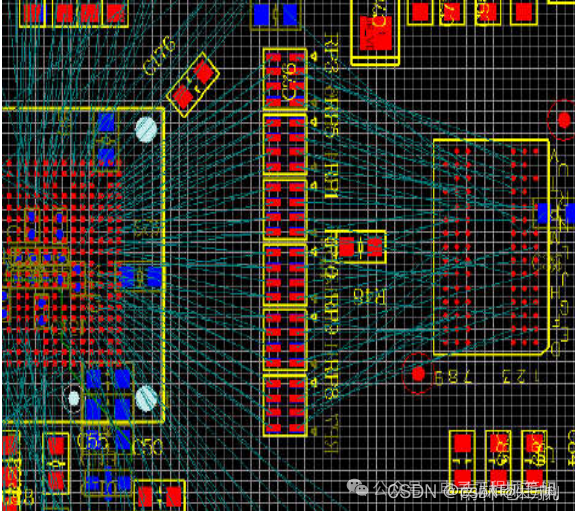

1、一片DDR

一片DDR时,点对点布局,留出一定的绕线空间

2、两片DDR

两片DDR时,相对于CPU对应DDR引脚的中心位置精确,留出一定的绕线空间,同时注意串接电阻、并联电阻的位置

中间有排阻时,DDR相对于中心距离:800~1000mil

中间无排阻时,DDR相对于中心距离:600~800mil

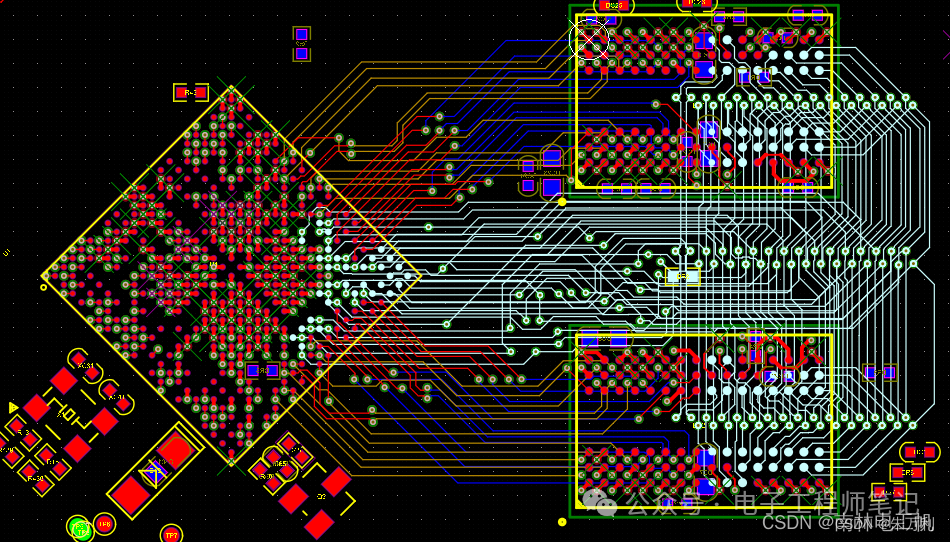

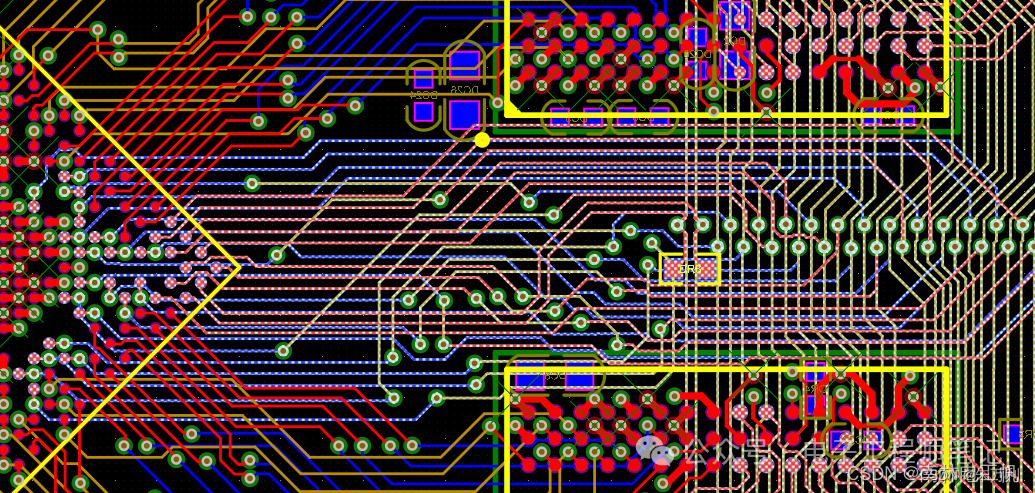

要合理的规划走线布局结构,按照前面所说的,两片DDR最少需要三个走线层,假设是一个6层板,三个走线层,以走T点结构为例:

图中可以看出,因为是BGA封装,表层很难直接走线,同时高八位数据与低八位完成数据两两相互交叉,理论上的布局一下是可以一层走数据线的,但是的话地址线必须要用到至少两个走线层,也不需要在手头宽裕的情况下吝啬走线,高低八位各一个走线层搞定,同时还要注意的是,一般T点中心结构走的是内层,所以尽量不要让内层数据线与内层地址线在DDR内部走线时有冲突,即如下:

左边是数据走线,用粗蓝色走,右边是T点,用内层层黄椰子走,如果你都用黄椰子走线的话

,理论上来说完全没问题,但是尽量错峰出行,!!!避免走线空间太少了

布拉格添加一下T如何出线,基本上如果是两片DDR,一定是要先走DDR内部的T点,然后再走外部的T点,最好的分配就是,千年的点交叉错开放置,放两派,那么一般两边的地址线出线是不平均的,T点的两排过孔尝试控制的平均分布一下,T点中过孔与过孔之间的分布一般就是你扇出的那个DDR焊盘过孔之间的间距,否则不太出现,添加的这一点要记住,间距最好与DDR的过孔出线保持一致

然后就是T点走线,基本上吧,你是不可能在T点布拉格满足3W原则,就跟你BGA出现不可能满足3W原则一样,你恐怕能满足,你也牛逼,我佩服你,嘻嘻嘻,T点积分,很难很难,基本上你知道走T点,扇孔时,分配孔也是门学问,这个要自己在实践中领悟了。

然后就是CPU走线引出到DDR的T点布拉格,其实没什么讲究,表层尽量走出来,走不出来的走底层,交错的就用第三层交换位置走线,留足绕线等长的空间。 (理论上四个走线层最舒服,要基于成本考虑捏)

3、四片DDR及以上

四片DDR或8片DDR时,一般两片顶底对贴,跟两片DDR一个道理,没啥新东西说,意思差不多意思吧,

本站所有转载文章系出于传递更多信息之目的,且明确注明来源,不希望被转载的媒体或个人可与我们联系,我们将立即进行删除处理。

相关文章

PADS9.5有哪些改变?PADS9.5是不是PCB电子设计最好软件?

layout PADS Locgic PADS router而其它的书藉通常只讲前两个软件!特别是等长布线,蛇形布线,虚拟过孔,关联网络等实用功能都一一介绍有,且在视频教程中也有介绍,想学...

Qorvo推出面向5G小基站网络的高效功率放大器系列产品

供货。如需订购产品,请联系 Qorvo 销售代表或下单。 广告 欲进一步了解以下产品,请观看我们的在线教程“”。 规格...

毕业设计| STM32+TI BQ76940设计48V BMS方案

改官方的PCB也行,我就是这么干的。 具体方案 原理框图: 总览原理图: STM32我是用Cubmx进行的快速开发,配置起来很方便,具体流程我也是根据网上各种Cubemx教程一点一点来的,在此...

三菱plcfx3u与伺服驱动器接线教程

三菱plcfx3u与伺服驱动器接线教程;在这里我们使用的是三菱FX—3U的PLC与松下A5的伺服驱动器,我们在PLC上设计了停止指令,远点回归,近点信号,中断信号,以及正反转限位等。因为...

Pads Layout:搭建电子设计之桥,引领职业新航向

Pads Layout:搭建电子设计之桥,引领职业新航向; PADSLayout,作为一个在电子设计自动化(EDA)领域广泛使用的PCB设计软件,其重...

一文读懂硬件设计的工作流程

)在电路板上,然后根据飞线(也叫预拉线)连接其电信号(布线)。 完成了PCB布局布线后,要用到哪些元器件应该有所归纳,所以我们将用到BOM表。 选择PCB设计工具 Protel,也就是Altium...

解析pcb板密度,了解关键指标!

解析pcb板密度,了解关键指标!; PCB电路板密度是指 PCB 上元件和布线的密集程度,pcb板密度是评估 PCB 设计...

7大步骤教你简单设计完美PCB!

孔、装配孔等等。 充分考虑和确定布线区域和非布线区域(如螺丝孔周围多大范围属于非布线区域)。 3、PCB布局设计 布局设计即是在PCB板框内按照设计要求摆放器件。在原理图工具中生成网络表(Design...

PCB布线设计参考

PCB布线设计参考;常见布线规则本文引用地址:(1) 板上预划分数字、模拟、DAA信号布线区域。 (2)数字、模拟元器件及相应走线尽量分开并放置于各自的布线区域内。 (3) 高速...