英伟达首席执行官黄仁勋近年来多次在公开场合表示,“摩尔定律已死”。虽然英特尔和 AMD 高管持不同观点,但谷歌近日公布的一份报告,再次佐证了黄仁勋的观点。

摩尔定律是英特尔创始人之一戈登・摩尔的经验之谈,其核心内容为:集成电路上可以容纳的晶体管数目在大约每经过 18 个月到 24 个月便会增加一倍。换言之,处理器的性能大约每两年翻一倍,同时价格下降为之前的一半。

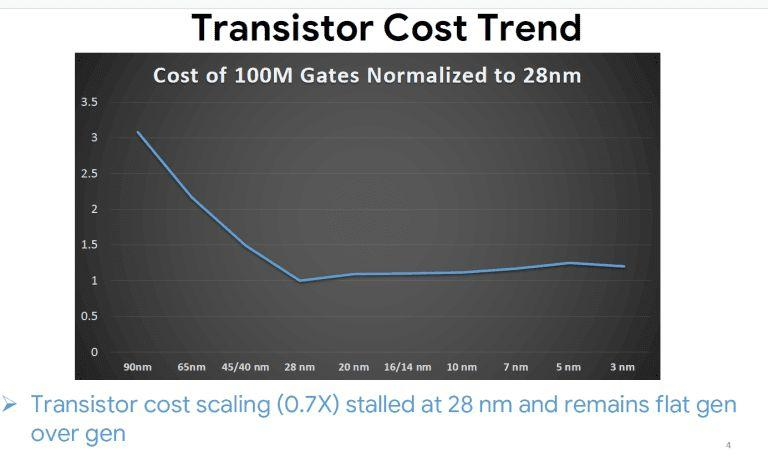

1 亿栅极晶体管自 2014 年 28nm 以来成本陷入停滞,并未下降

三维半导体集成公司 MonolithIC 3D 的首席执行官 Zvi Or-Bach 早在 2014 年就提交了一份分析报告,显示每晶体管成本在 28 纳米时已停止下降。

谷歌的 Milind Shah 在 IEDM 2023 的短期课程(SC1.6)中验证了这一说法。他指出,自台积电 2012 年量产 28 纳米平面工艺技术以来,1 亿个栅极(gate)单位晶体管成本实际上有所增加,并没有变得便宜。

上图表明 1 亿栅极晶体管成本并未下降

谷歌研究结果表明:“晶体管成本的增长(0.7 倍)在 28 纳米时停滞不前,并且在各代之间保持持平。”

业界对新节点的单位晶体管成本收益递减的担忧由来已久。在 7 纳米、5 纳米和 3 纳米不断演进过程中,芯片制造工艺技术需要更复杂的晶圆厂工具,这些工具的成本高达数亿美元(ASML Twinscan NXE 光刻机的成本为 2 亿美元),让前沿晶圆厂的成本达到 200 亿至 300 亿美元的水平。

不过,虽然芯片制造在过去几年中变得越来越复杂和昂贵,但我们还是应该从更大的角度来看待这个问题。

事实上,根据谷歌公司的 Milind Shah 在行业展会 IEDM 上展示的图表,以 28 纳米为标准的 1 亿个晶体管的成本实际上是持平的,甚至还在增加。

是什么推动工艺演进?

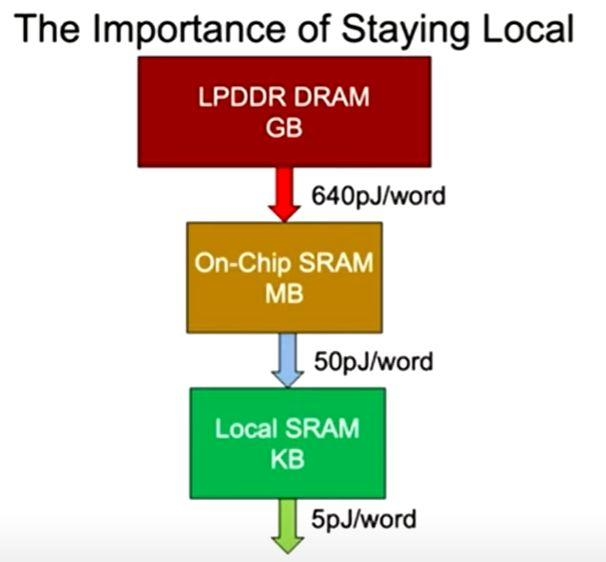

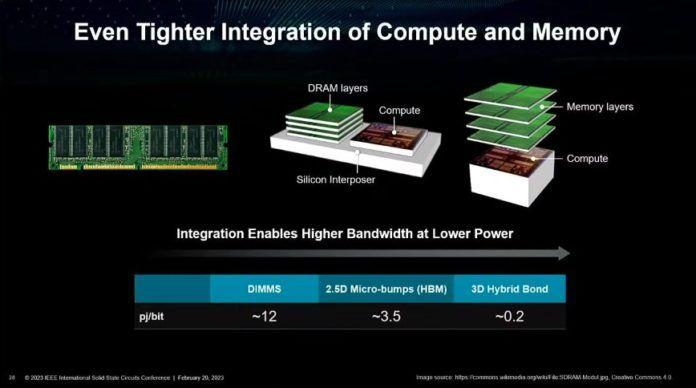

尽管成本缩减停滞不前,但为什么业界仍在推动晶体管不断缩小,目标是达到令人难以置信的 1 纳米节点?答案在于系统级效益(system-level benefits)。英伟达™(NVIDIA®)公司首席科学家比尔-达利(Bill Dally)绘制的这张图表就说明了这一点。

图源:Bill Dally,伯克利 EECS,2022 年 11 月 30 日

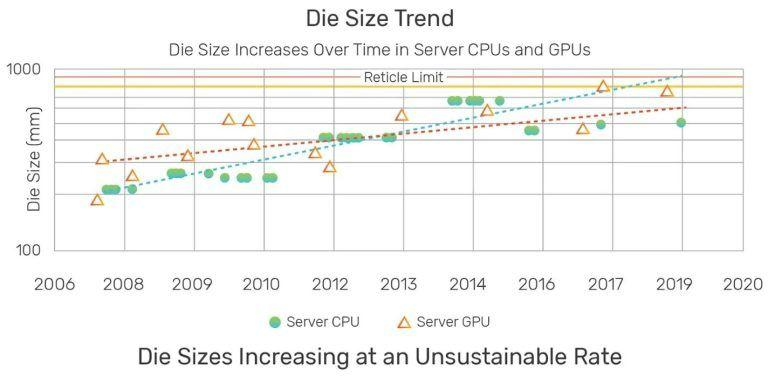

这反过来又推动了 CPU 和 GPU 等领先计算设备达到或超过微粒尺寸的趋势。追求更小的节点,可以让芯片上的元件集成得更紧密,从而进一步提高性能和效率。

下图为 Die(裸晶 / 裸片)尺寸趋势:

图源:AMD

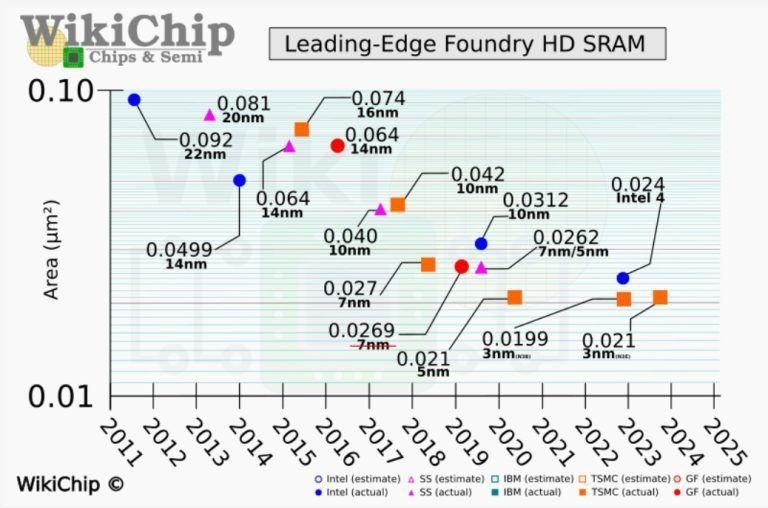

遗憾的是,逻辑和存储器(DRAM、NAND)的制造工艺截然不同。因此,它们在不同的晶圆上生产,无法通过微缩(scaling)实现集成。更糟糕的是,SRAM 位元格(Bit Cell)的微缩在 5 纳米节点时就已经停止了。

图源:WikiChip

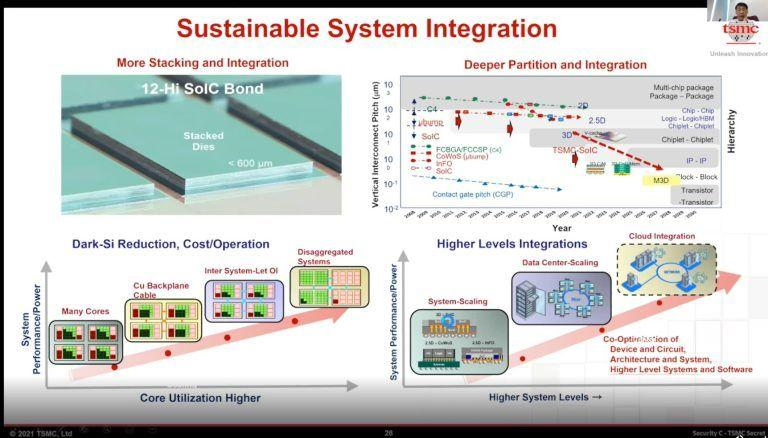

AMD 和台积电似乎都了解这些趋势,并在过去几年中调整了混合键合(Hybrid Bonding)技术,以进一步提升计算性能。

图源:Lisa Su 博士

图源:台积电

芯粒(Chiplet)方案受追捧

芯粒英文是 Chiplet,是指预先制造好、具有特定功能、可组合集成的 Die 。

厂商为了优化成本和性能,将某些设计分解,即切成 chiplets,而不是使用前沿节点生产由单片硅制成的单片设计,更有吸引力。

客户端领域

在客户端计算领域,最典型的分解设计实例就是 AMD 的 Ryzen 台式机 CPU 和英特尔的 Meteor Lake 笔记本电脑 CPU,采用来自不同工厂的不同工艺制造。

数据中心领域

在数据中心领域,AMD 的 EPYC 数据中心 CPU 也是一个成功的例子。像 AMD 和英特尔这样市值数十亿美元的公司当然可以仔细评估他们的设计方案,然后利用他们所掌握的最佳技术制造产品。

而对于规模较小的制造商来说,事情可能就没那么简单了。

多芯粒设计

首先,multi-chiplet 设计往往比单片(monolithic)设计更耗电,因此并不是移动设备的最佳选择。

multi-chiplet 设计一项艰巨的工程任务,虽然 MonolithIC 3D 等公司提供多芯片集成服务(最终使用先进的封装技术,如英特尔的 Foveros 或台积电的 CoWoS),但服务成本并不便宜。

第三,先进封装技术成本高昂,而且即便有厂商愿意掏钱购买,台积电 CoWoS 封装产能吃紧,显然没有余力满足其要求。