引言

前面漫谈车规MCU系列的首篇文章《漫谈车规MCU国产替代》发表后,受到了广大粉丝的广泛关注和热烈讨论。很多留言希望我能够介绍一下何为车规芯片,什么样的芯片才能算是真正的车规芯片? 为此,我特意撰写了本文,结合我在车规芯片行业的多年从业经验和对车规MCU行业的深入洞察,较为全面的展开“何为车规”这个话题的介绍和分析。

车规芯片的四大行业标准(技术壁垒)

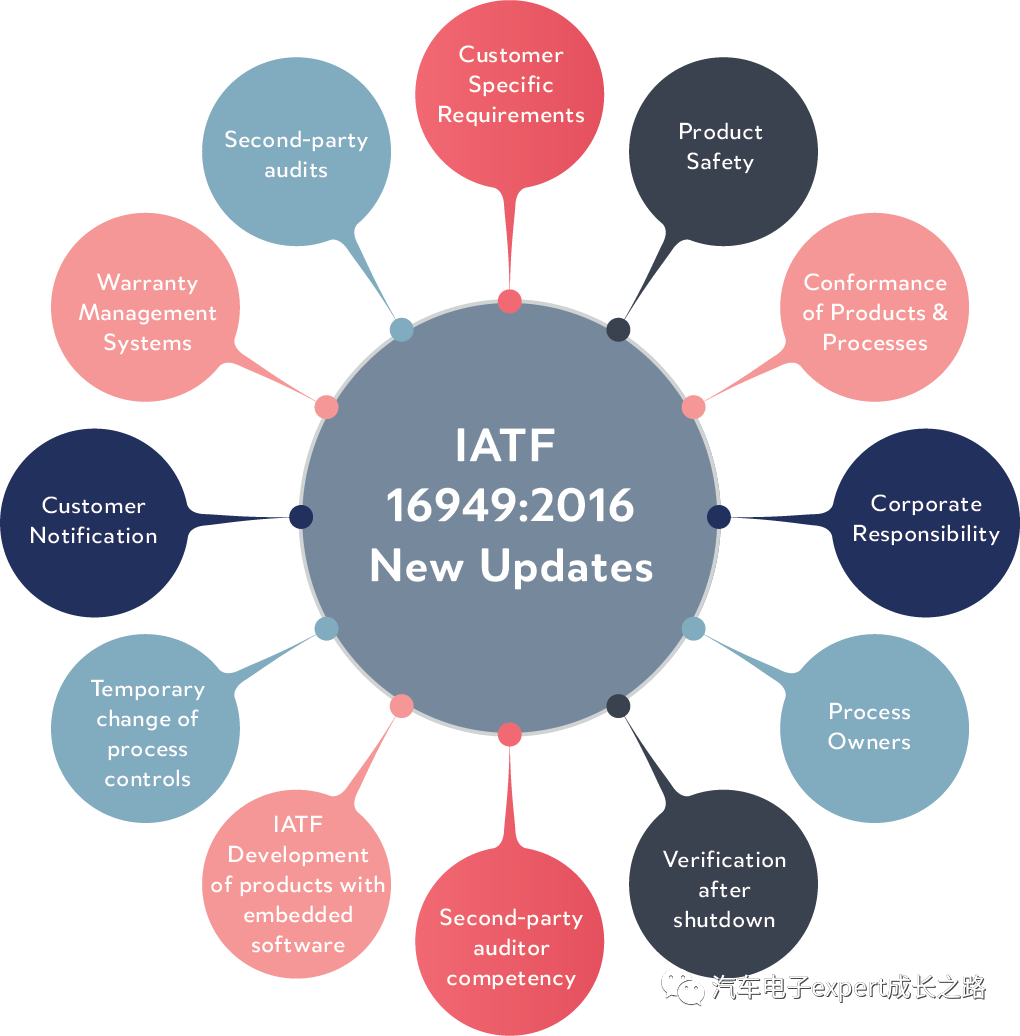

1.1 汽车行业铁律--IATF-16949

IATF-16949是国际汽车任务组(International Automotive Task Force,简称IATF)制定的一项国际标准,用于质量管理体系在汽车行业的应用。该标准基于ISO 9001质量管理体系标准,并在此基础上增加了汽车行业特定的要求和指导,旨在提高汽车供应链的质量管理水平和产品质量。

IATF的成员包括了国际标准化组织质量管理与质量保证技术委员会(ISO/TC176),意大利汽车工业协会(ANFIA),法国汽车制造商委员会(CCFA)和汽车装备工业联盟(FIEV),德国汽车工业协会(VDA),汽车制造商BMW)、Daimler Chrysler、Fiat、Ford、GM、Renault和Volkswagen等。

IATF-16949的目标是通过建立一套规范和要求,促进汽车制造商和供应商之间的合作和协作,确保供应链中的所有环节都符合质量管理的最佳实践。该标准涵盖了从设计和开发、生产、安装和服务到产品退役的全生命周期,要求组织建立和实施一套完整的质量管理体系。

IATF-16949的要求包括质量目标的设定和追踪、过程管理、产品和过程验证、供应商管理、不良品管理、持续改进等。它还强调了风险管理、员工培训和参与、测量和分析数据等方面的重要性。 通过实施IATF-16949,组织可以提高产品质量和可靠性,减少缺陷和客户投诉,提高生产效率和交付能力。此外,符合IATF-16949的组织还可以获得国际认可,增加在汽车行业中的竞争力和市场份额。

IATF-16949最为人所知的五大工具如下:

统计过程控制(SPC)

测量系统分析(MSA)

产品质量先期策划(APQP)

潜在失效模式和效果分析(FMEA)

生产件批准程序(PPAP)

其中,PPAP报告是汽车产业链供应商逐级提供的,由晶圆厂和封测厂提供的PPAP被整合到车规芯片的PPAP中,然后提供给零部件设计生成商(Tier-1),最后由Tier-1整合ECU系统软硬件设计和生产的流程数据提供给整车厂。

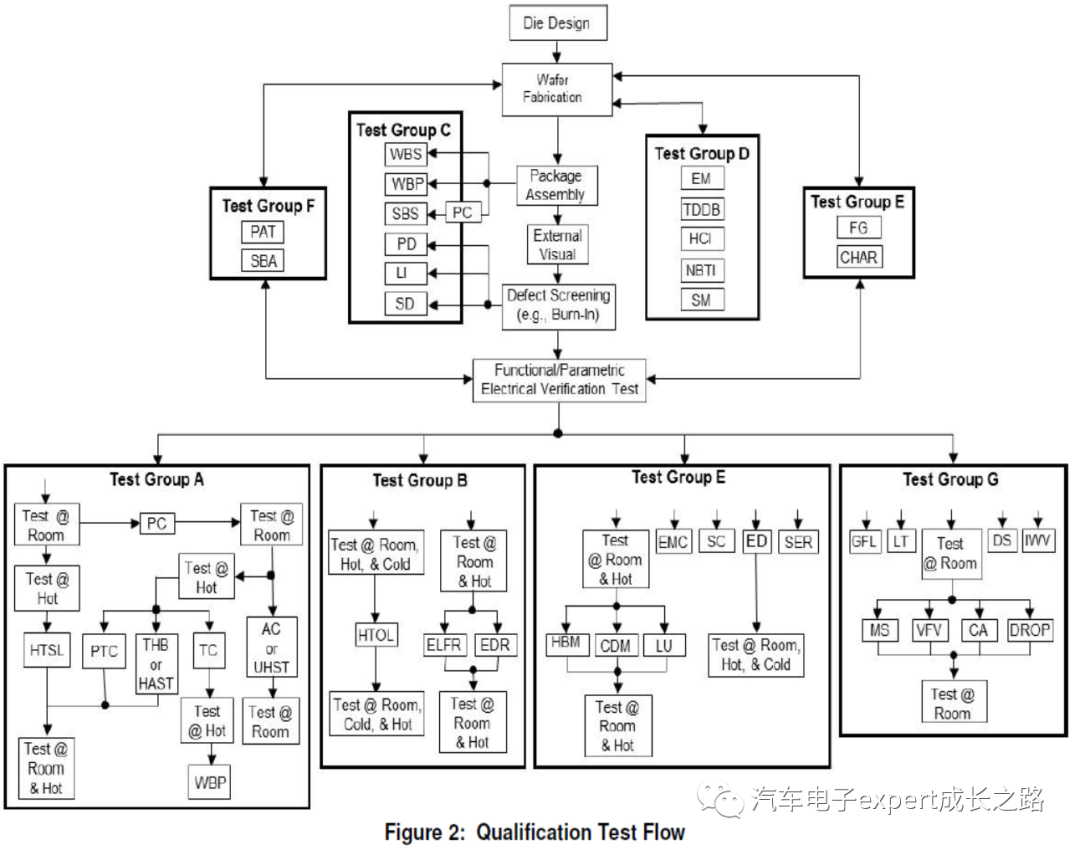

1.2 车规芯片可靠性验证标准--AEC-Q100

AEC-Q100是由汽车电子委员会(Automotive Electronics Council,简称AEC, 最初是由克莱斯勒、福特和通用汽车于 1990 年代成立 的组织,目的是建立通用的零件鉴定和质量体系标准)制定的一项汽车电子元器件可靠性标准。该标准旨在确保在汽车电子系统中使用的元器件具有足够的可靠性和耐久性,以满足汽车行业的严格要求。 AEC 是建立可靠、高质量电子组件标准的标准化机构。符合这些规格的组件适用于恶劣的汽车环境,无需额外的组件级鉴定测试。包括:

AEC-Q100:集成电路(IC)器件,比如MCU、ADC、PMIC, CAN/LIN收发器等;

AEC-Q101:分离(Discrete)器件,比如三极管、二极管、MOSFET, SiC等;

AEC-Q102:分离光电(Discrete Optoelectronic )器件,比如LED等;

AEC-Q103:分离传感器(Sensor)器件,比如MEMS压力/加速度计、温度传感器等;

AEC-Q104:分离多芯片模块(MCM)器件,除Q100/101/102/103和Q200不能覆盖的多芯片模块;

AEC-Q200:无源器件,比如电容、电阻、电感等;

AEC-Q100标准主要适用于集成电路(IC)和半导体器件,对其进行了一系列的可靠性测试和评估,其测试验证项目最多最复杂,周期也是最长的(以IC芯片功能的规模和复杂度而定)。这些测试和评估包括温度循环测试、湿热循环测试、可靠性评估、可靠性预测等。通过这些测试,可以评估元器件在不同环境条件下的可靠性和性能。

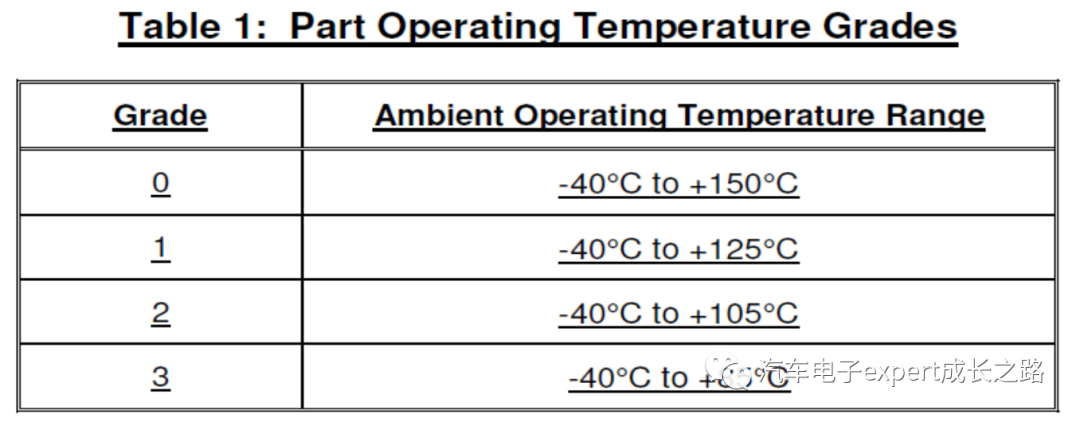

AEC-Q100标准分为几个等级,包括Grade 0到Grade 3,每个等级代表了不同的可靠性要求和测试条件。Grade 0是最高等级,适用于在高温环境下工作的关键应用,而Grade 3适用于一般的汽车电子应用。

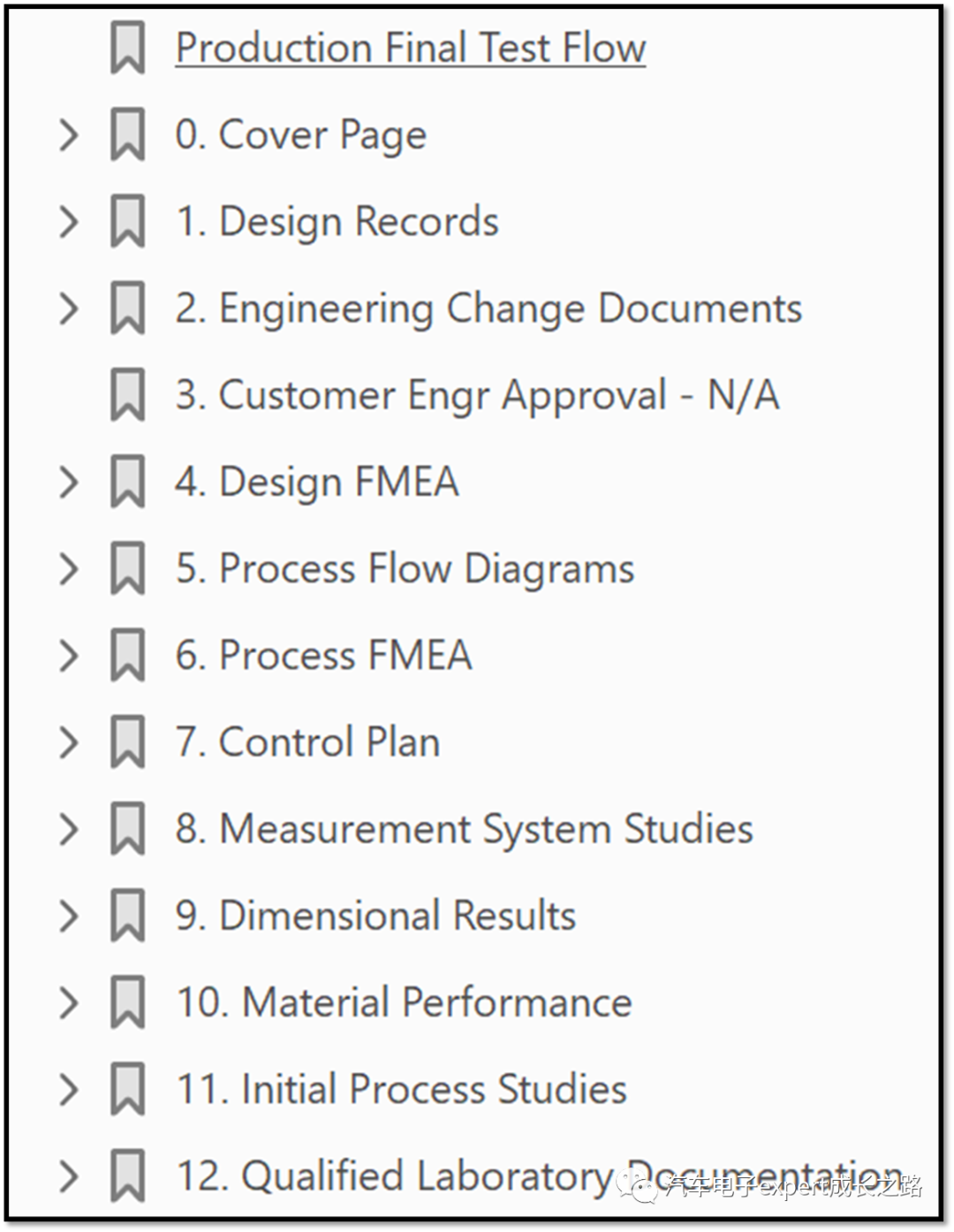

符合AEC-Q100标准的元器件可以获得汽车制造商的认可,并被广泛应用于汽车电子系统中,如发动机控制单元、车身控制模块、安全气囊系统等。这些元器件经过严格的可靠性测试和评估,能够在恶劣的汽车环境下稳定运行,确保汽车的安全性和可靠性。 AEC-Q100包含测试结果将包含在一份量产器件审批流程报告(PPAP report)中给到客户(Tier-1/Car OEM),其中还包括芯片的设计和流程失效模式与影响分析(Design FMEA & Process FMEA),如下是一份完整的量产车规MCU芯片的PPAP报告目录:

1.3 车规芯片功能安全标准--ISO 26262

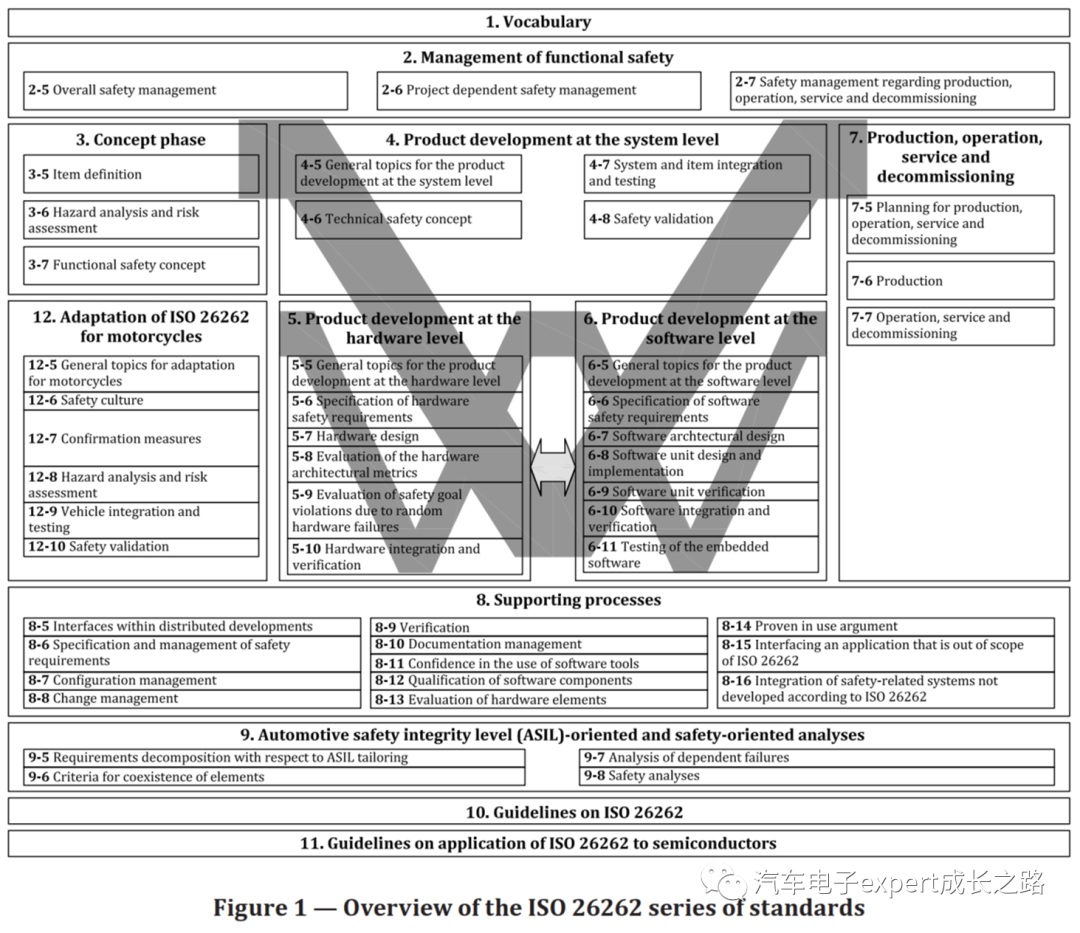

功能安全ISO-26262是IEC61508 对电子电气(E/E )系统在道路车辆方面的功能安全要求的具体应用。 ISO 26262是一项国际标准,用于汽车行业中的功能安全管理系统。该标准于2011年发布初版,2018年再版,新增了两个章节--第12章:ISO26262对摩托车的适用性和第11章:ISO26262对半导体器件的应用指南,旨在确保在车辆电子和电气系统中的功能安全性,以减少由于系统故障引起的事故和伤害。 ISO 26262标准适用于汽车电子和电气系统的整个生命周期,包括设计、开发、生产、操作、维护和退役阶段。它提供了一套方法和要求,帮助汽车制造商和供应商在设计和开发过程中识别和管理潜在的安全风险。

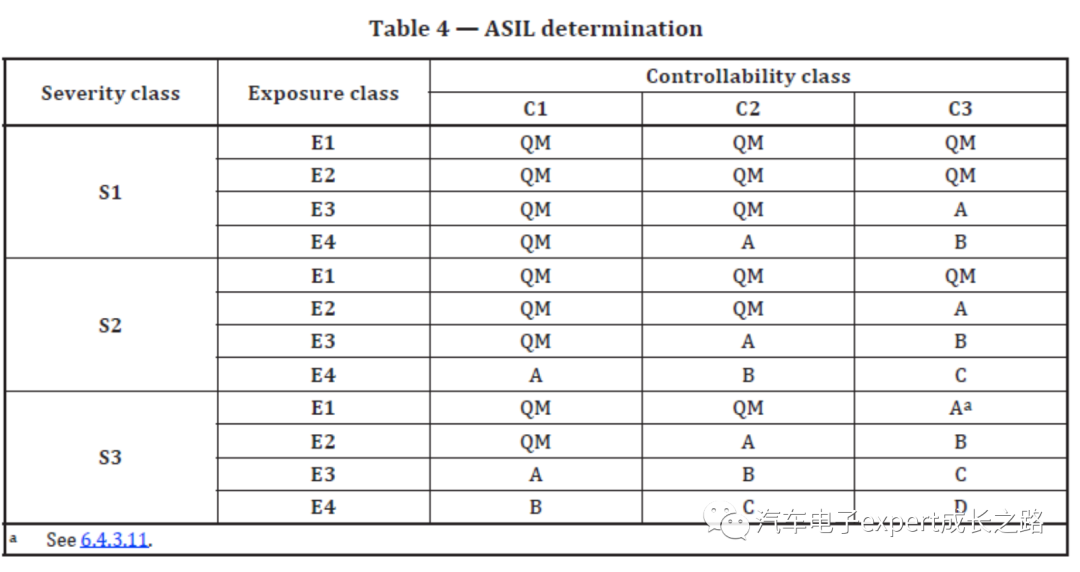

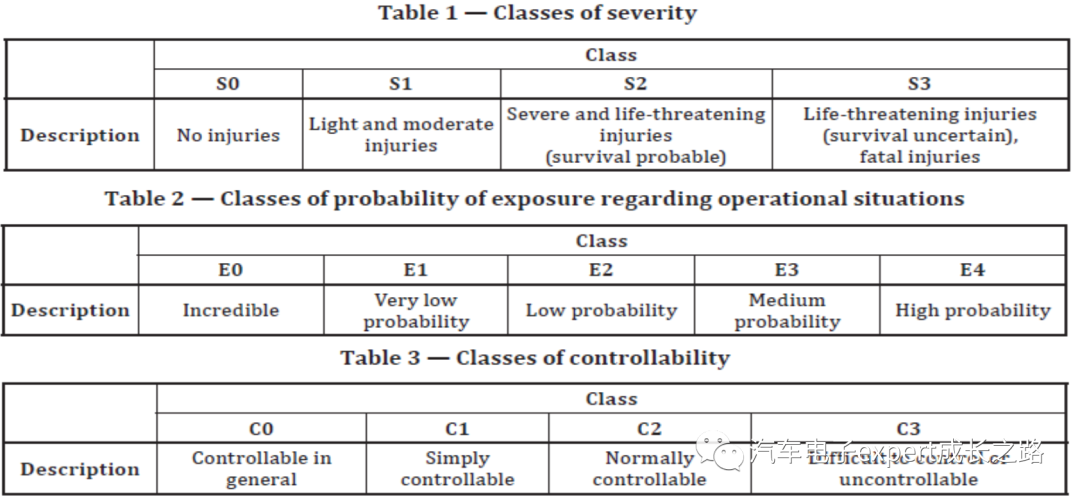

ISO 26262标准的关键概念包括安全性管理、安全性生命周期、安全性验证和确认,以及安全性要求的定义和评估。它要求组织进行安全风险评估和安全性目标的设定,采取适当的安全设计措施,并进行系统安全验证和确认。 ISO-26262提供了决定风险等级的具体风险评估方法HARA(SEC(严重度(S)、暴露率(E)、和可控性(C)三个指标 à ASIL- A/B/C/D or QM)等级;

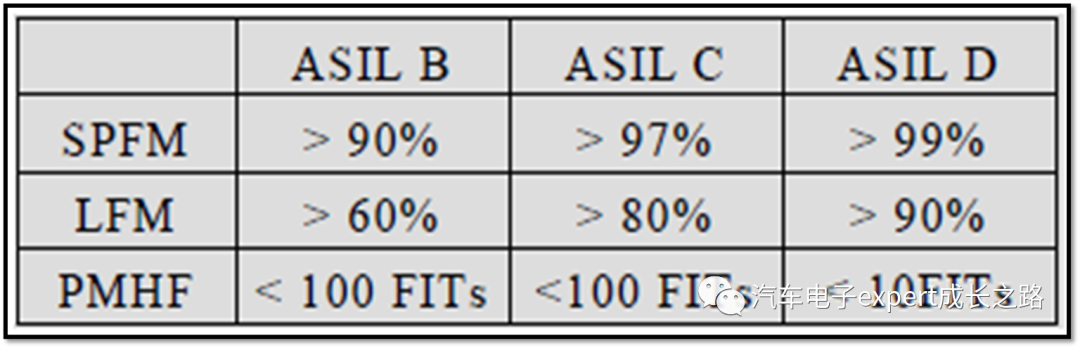

ISO-26262通过分析系统需求,关注具体的功能安全目标(SG), 通过系统实现软硬件评估/分解/验证,使用有效的功能安全机制(SM)保证单点失效(SPFM)和潜在失效(LFM)的目标诊断覆盖率(DC),同时满足随机硬件故障概率(PMHF, 单位为FIT(Failure In Time),1FIT = 1/10(-9)h, 即1000,000,000小时内失效仅1次)要求;

通过遵循ISO 26262标准,汽车制造商和供应商可以确保其电子和电气系统满足功能安全的要求,减少系统故障导致的潜在风险。这有助于提高汽车的安全性和可靠性,并满足法规和客户的要求。同时,符合ISO 26262的组织还能够提高其在汽车行业中的竞争力和市场份额。

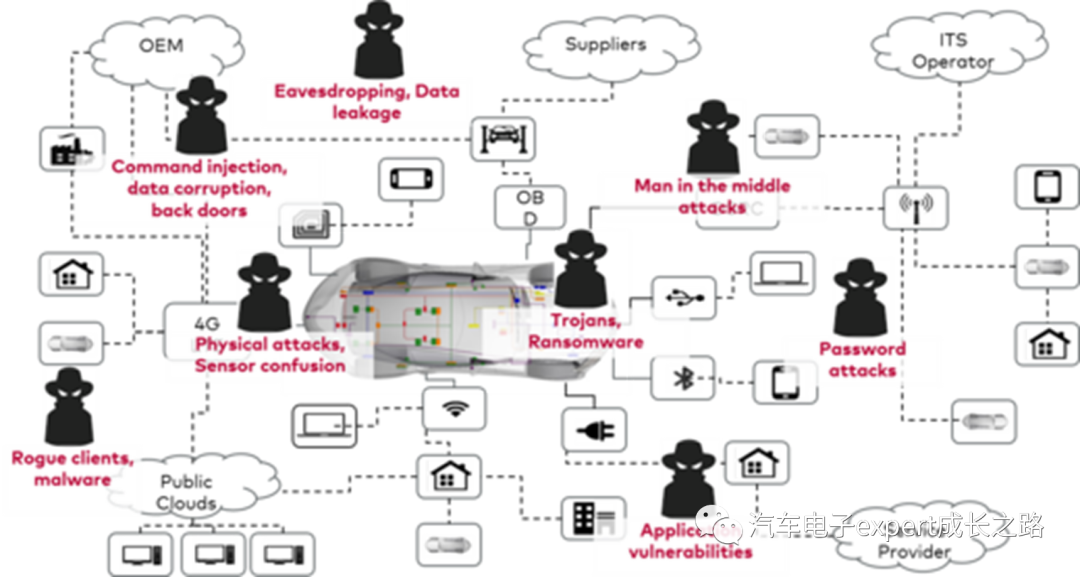

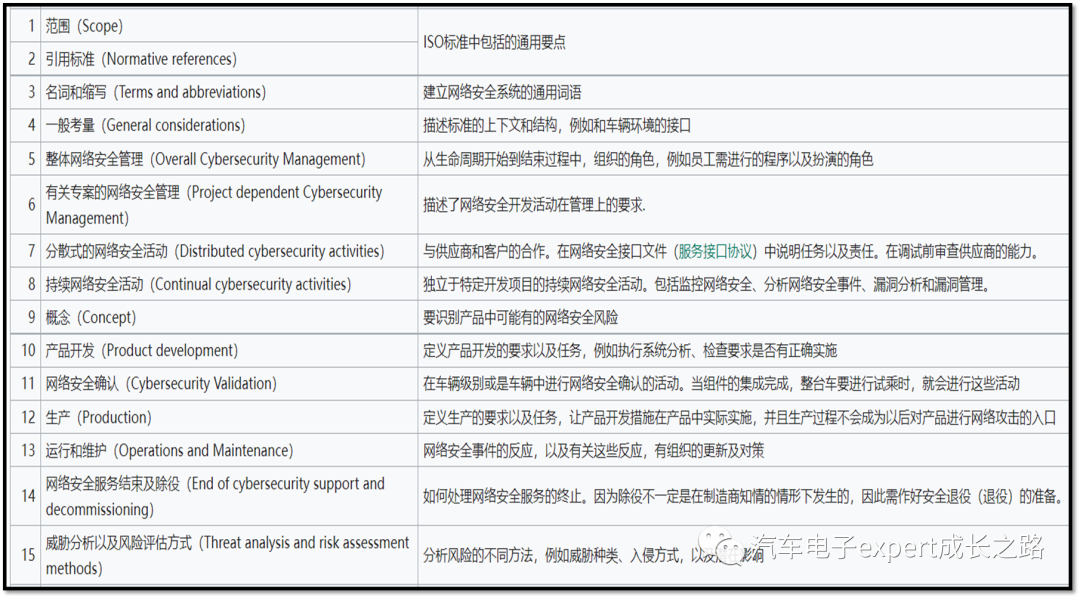

1.4 车规芯片信息安全标准--ISO 21434

随着车联网应用的日益普及,针对汽车的网络攻击风险越来越高:作为汽车的空中编程(OTA)、车队管理系统、车辆和其他设备通讯(V2X / V2V)等功能的基础架构,汽车也出现了新的攻击面。基于开发的考量,需要在标准上有对应的措施。 ISO 21434是一项新的国际标准,专门针对汽车行业中的信息安全进行管理和保护。该标准于2021年发布,旨在帮助汽车制造商和供应商建立和维护安全的汽车电子和软件系统。

ISO 21434标准的目标是确保汽车电子和软件系统在设计、开发、生产、操作和维护的整个生命周期中具备适当的信息安全控制措施。它提供了一套方法和要求,以帮助组织识别和管理潜在的信息安全风险,保护车辆免受恶意攻击和未经授权的访问。

ISO 21434标准涵盖了许多关键方面,包括安全风险评估、安全需求分析、安全设计、安全验证和确认、安全生命周期管理等。它要求组织在设计和开发过程中采取适当的安全措施,如身份验证、访问控制、数据保护、通信安全等。 ISO/SAE 21434的核心是威胁分析以及风险评估。其基于威胁分析与风险评估(TARA)方法,定义了类似于 ISO 26262 中的 ASIL的网络安全保证级别(CAL)。 通过遵循ISO 21434标准,汽车制造商和供应商可以提高其车辆和系统的信息安全性,减少被黑客攻击和未经授权访问的风险。这有助于保护车辆中的关键功能和数据,确保驾驶员和乘客的安全和隐私。 ISO 21434标准的实施还可以帮助汽车行业满足法规和客户对信息安全的要求,并提高组织在市场竞争中的信誉和竞争力。同时,它也促进了汽车行业对信息安全的重视和持续改进。

完整的车规芯片研发流程

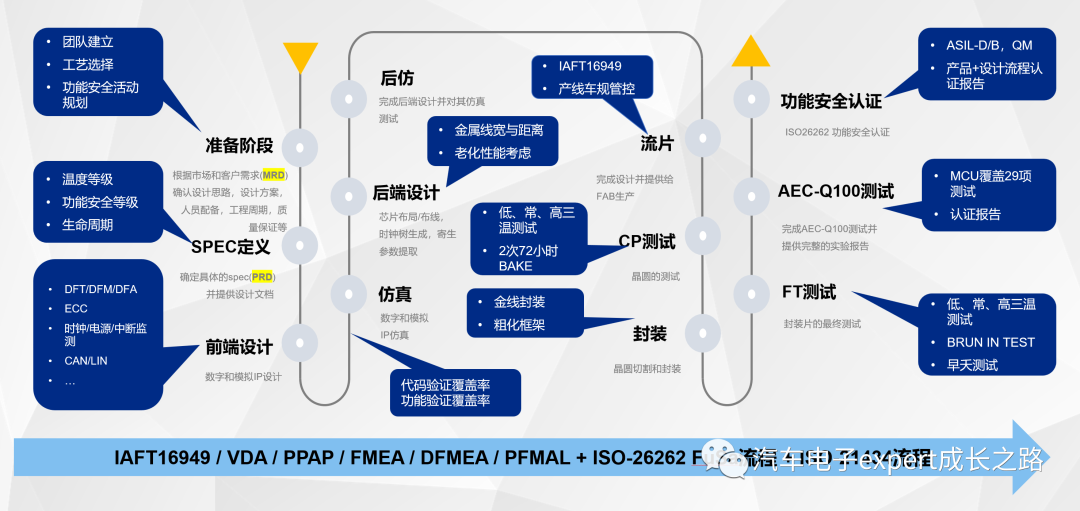

为了保证车规芯片的高性能和高可靠性,必须掌握和使用符合IATF-16949并结合汽车功能安全和信息安全流程的完整的车规芯片研发流程。

为了帮助大家更好的理解相关概念,这里有必要介绍一下芯片设计的各环节和流程要求要点及意义。

2.1 需求定义(MRD和PRD)

芯片的需求定义主要包括市场需求文档(Market Requirements Document,MRD)和产品需求文档(Product Requirements Document,PRD)。 市场需求文档(MRD)是在芯片设计之前制定的,它主要描述了市场对芯片产品的需求和期望。MRD通常由市场营销团队或产品管理团队编写,包括以下内容:

市场背景:描述芯片产品所处的市场环境和竞争情况,包括市场规模、增长趋势、竞争对手等。

目标市场和用户:明确芯片产品的目标市场和目标用户,包括行业、应用领域、用户需求等。

产品定位:定义芯片产品在市场中的定位和差异化特点,包括产品的主要功能、性能要求、价格范围等。

功能需求:列出芯片产品的主要功能需求,包括支持的通信协议、数据处理能力、接口要求等。

性能需求:定义芯片产品的性能指标,包括速度、功耗、可靠性等。

市场需求优先级:根据市场需求的重要性和紧迫性,对各项需求进行优先级排序。

产品需求文档(PRD)是在MRD的基础上进一步细化和详细描述芯片产品的具体功能和电气参数规格(spec.),它主要由产品经理或系统工程师编写,包括以下内容:

产品概述:对芯片产品的整体概述和目标进行描述,包括产品的主要特点和优势。

功能需求:详细说明芯片产品的各项功能需求,包括功能模块、接口要求、数据处理能力等。

性能需求:具体定义芯片产品的性能指标,包括速度、功耗、时延、抗干扰能力等。

通信接口需求:描述芯片产品与外部设备的接口和通信协议要求,包括物理接口、电气特性、数据格式等。

可靠性需求:定义芯片产品的可靠性要求,包括寿命、稳定性、故障率等。

安全性需求:列出芯片产品的安全性要求,包括数据保护、身份认证、防篡改等。

限制和约束:说明芯片设计中的限制和约束条件,包括成本、尺寸、供电要求等。

MRD和PRD是芯片设计的基础,它们明确了芯片产品的需求和目标,为后续的芯片设计和开发工作提供了指导和依据。同时,MRD和PRD也是与客户和合作伙伴进行沟通和协调的重要文档。

2.2 前端设计(数字外设和模拟外设IP设计)

芯片的前端设计包括数字外设和模拟外设IP设计,是芯片设计中的重要组成部分,它们提供了与外部设备进行通信和交互的接口和功能。下面是数字外设和模拟外设IP设计的一般流程:

外设需求分析:在开始设计之前,需要明确外设的功能需求和接口要求。这包括外设的数据传输速率、通信协议、数据格式等方面的要求。同时,还需要考虑外设与芯片的连接方式和电气特性等。

IP架构设计:根据外设需求分析,设计IP的整体架构。这包括确定IP的功能模块、接口和数据路径等。在数字外设IP设计中,常见的功能模块包括数据缓冲、时钟管理、数据处理等。在模拟外设IP设计中,常见的功能模块包括模拟信号输入输出接口、信号处理电路等。

IP设计和验证:根据IP架构设计,进行IP的详细设计和验证。在数字外设IP设计中,使用硬件描述语言(如Verilog或VHDL)来描述IP的逻辑结构和功能。在模拟外设IP设计中,使用模拟电路设计工具进行电路设计和仿真验证。

IP集成和验证:将设计好的IP集成到芯片的整体设计中,并进行验证。在数字外设IP设计中,需要进行逻辑仿真和时序仿真,验证IP的功能和时序性能是否符合设计要求。在模拟外设IP设计中,需要进行电路仿真和电路验证,验证IP的模拟性能是否符合设计要求。

物理设计和布局:对IP进行物理设计和布局,将IP的电路结构和布局规则与芯片的其他部分进行整合。物理设计包括IP的布局、布线、时钟树设计等。通过物理设计和布局,可以优化IP的面积、功耗和性能等。

物理验证:对IP进行最终的物理验证,确保IP的物理设计满足设计要求和约束。物理验证包括电气规则检查(DRC)、布局规则检查(LVS)等。

IP文档和测试:最后,根据IP设计和验证的结果,生成IP的设计文档和测试文档。设计文档包括IP的规格说明、设计原理和接口定义等。测试文档包括IP的测试计划、测试用例和测试结果等。

数字外设和模拟外设IP设计在芯片设计中起着重要的作用,它们提供了与外部设备进行通信和交互的接口和功能。通过设计和验证IP,可以确保芯片与外部设备的兼容性和可靠性,提高芯片的功能和性能。同时,IP设计的模块化和可重用性也可以提高芯片设计的效率和可靠性。

2.3 逻辑仿真和数字验证

芯片设计的逻辑仿真和数字验证是芯片设计流程中非常重要的一环,它主要用于验证芯片的功能和时序等方面的正确性。下面是逻辑仿真和数字验证的一般流程:

设计规格和功能验证:在开始逻辑仿真之前,首先需要明确芯片的设计规格和功能要求。根据这些要求,制定验证计划,并编写测试用例。

逻辑仿真:逻辑仿真是通过软件工具模拟芯片电路的行为,验证电路的功能是否符合设计规格。在逻辑仿真中,会使用硬件描述语言(如Verilog或VHDL)来描述电路的逻辑结构和功能,并使用仿真工具进行仿真运行。通过仿真结果,可以检查电路的功能是否正确。

时序仿真:时序仿真是在逻辑仿真的基础上,考虑电路的时序约束,验证电路的时序性能是否满足设计要求。时序仿真可以检查电路的时钟频率、时序路径、时序敏感性等方面的性能。

电源和环境仿真:除了功能和时序仿真,还需要进行电源和环境仿真,验证电路在不同电源和环境条件下的工作情况。这可以帮助检查电路对电源噪声、温度变化等因素的鲁棒性。

仿真结果分析和调试:在仿真过程中,需要对仿真结果进行分析和调试。如果发现电路的功能或时序不符合设计要求,需要进行错误定位和修复。

数字验证:数字验证是在逻辑仿真的基础上,使用专门的验证工具进行验证。数字验证可以通过随机测试、形式验证、覆盖率分析等方法,对电路的功能进行全面验证。

仿真验证报告:最后,根据逻辑仿真和数字验证的结果,生成仿真验证报告。报告中包括了验证计划、测试用例、仿真结果和分析等内容,用于记录和交流验证过程和结果。

逻辑仿真和数字验证在芯片设计中起着至关重要的作用,它可以帮助设计人员发现和解决电路设计中的问题,确保芯片的功能和性能满足设计要求。通过逻辑仿真和数字验证,可以提高芯片设计的可靠性和效率,减少后续芯片制造和测试的成本和风险。

2.4 后端设计与仿真

芯片的后端设计与仿真是指在芯片设计流程中,将前端设计完成的电路布局、布线和物理实现等工作。这个阶段主要包括以下几个步骤:

物理设计规划:根据设计需求和约束,制定物理设计规划,确定芯片的布局和布线风格,以及各个模块的位置和大小等。

布局设计:将电路的逻辑元件按照物理规划的要求进行布局,确定各个模块的相对位置和大小。布局设计要考虑电路的性能、功耗、面积和可靠性等因素。

布线设计:根据布局设计结果,进行电路的布线,将各个逻辑元件之间的连线完成。布线设计要考虑信号延迟、功耗、电磁兼容性等因素。

物理验证:对布局和布线进行物理验证,确保电路的布局和布线满足设计规范和约束。物理验证包括电气规则检查(DRC)、布局规则检查(LVS)等。

时序分析:对芯片进行时序分析,确保电路的时序满足设计要求。时序分析包括时序约束的制定和时序模拟等。

功耗分析:对芯片进行功耗分析,评估芯片的功耗性能,并进行功耗优化。功耗分析包括静态功耗和动态功耗的评估。

仿真验证:对芯片进行各种仿真,验证电路的功能和性能。仿真验证包括功能仿真、时序仿真、功耗仿真等。

物理优化:根据仿真和验证结果,对芯片进行物理优化,改进电路的性能、功耗和面积等。物理优化包括布局优化和布线优化等。

芯片的后端设计与仿真是芯片设计流程中非常重要的一环,它确保了芯片的物理实现满足设计要求和约束。通过物理设计和仿真验证,可以评估和改进芯片的性能、功耗和可靠性等,最终实现高质量的芯片产品。

2.5 流片与ECO设计修改

芯片设计的流片是指将芯片设计转化为实际的物理布局和连线,生成布局图和掩膜数据,以便进行芯片制造。流片的过程包括以下几个主要步骤:

物理设计规划:确定芯片的布局约束和分区,包括芯片的核心区域、输入输出引脚位置、电源和地线分布等。

布局设计:根据物理设计规划,将芯片的各个功能模块进行布局,包括放置模块、调整模块间的距离和相对位置,以满足性能和功耗要求。

连线设计:在布局的基础上,进行模块间的连线设计,包括信号线和电源线的布线,以及时钟网络的布线,以满足信号完整性和时序要求。

特殊设计:针对特殊模块和特殊要求,进行特殊设计,如模拟电路的布局和连线、高速接口的布线等。

布局优化:对布局进行优化,包括减小面积、减小功耗、减小时延等,以提高芯片的性能和可靠性。

掩膜生成:根据布局和连线设计,生成掩膜数据,用于芯片制造。

ECO(Engineering Change Order)设计修改是在芯片设计流片后,发现需要进行修改或修正的情况下进行的设计调整。ECO设计修改的目的是解决芯片设计中的问题或改进设计的性能和功能。ECO设计修改的步骤包括以下几个主要过程:

问题分析:分析芯片设计中的问题或需要改进的地方,确定需要进行的设计修改。

设计调整:根据问题分析的结果,进行相应的设计调整,包括修改布局、优化连线、调整电源和地线等。

验证和仿真:对设计修改后的芯片进行验证和仿真,以确保修改后的设计满足要求,并解决之前的问题。

评估和验证:对修改后的设计进行评估和验证,包括性能评估、功耗评估、时序验证等。

掩膜生成:根据修改后的设计,生成新的掩膜数据,用于芯片制造。

ECO设计修改是芯片设计的一个重要环节,它可以解决设计中的问题和改进设计的性能和功能,提高芯片的质量和可靠性。同时,ECO设计修改也需要考虑成本和时间的因素,以确保设计的修改是可行和有效的。

2.6 回片测试与EVB功能验证

芯片的回片测试是指在芯片制造完成后,对芯片进行测试和验证的过程。回片测试的目的是检测芯片的功能、性能和可靠性,以确保芯片符合设计规格和要求。回片测试的步骤包括以下几个主要过程:

芯片封装:将芯片进行封装,即将芯片芯片和引脚连接封装在封装材料中,以便进行测试和使用。

测试计划制定:根据芯片的设计规格和要求,制定测试计划,确定测试的目标、方法和流程。

芯片测试:使用测试设备和工具,对芯片进行各种测试,包括功能测试、性能测试、电气特性测试等。

数据分析:对测试结果进行数据分析和处理,评估芯片的性能和可靠性,检测是否存在缺陷或问题。

故障排除:如果在测试中发现问题或故障,进行故障排除,确定问题的原因,并进行修复或调整。

测试报告:根据测试结果,生成测试报告,记录芯片的测试情况和结果,以便后续的评估和验证。

EVB(Evaluation Board)功能验证是在芯片设计完成后,使用评估板对芯片的功能进行验证和评估的过程。EVB是一个包含芯片和相关电路的开发板,可以提供电源、时钟和接口等功能,以便进行芯片的功能验证和性能评估。EVB功能验证的步骤包括以下几个主要过程:

硬件连接:将芯片连接到评估板上,包括电源连接、引脚连接、信号线连接等。

软件配置:根据芯片的设计规格和要求,配置评估板的软件,包括时钟配置、寄存器设置等。

功能验证:使用评估板提供的接口和功能,对芯片的各个功能进行验证,包括输入输出功能、通信功能、存储功能等。

性能评估:通过评估板的测试和测量,对芯片的性能进行评估,包括功耗、速度、时延等。

数据分析:对功能验证和性能评估的结果进行数据分析和处理,评估芯片的功能和性能是否满足设计要求。

验证报告:根据功能验证和性能评估的结果,生成验证报告,记录芯片的验证情况和结果,以便后续的评估和验证。

EVB功能验证是在芯片设计完成后,对芯片的功能和性能进行初步验证和评估的重要环节,它可以帮助设计团队了解芯片的工作情况和性能表现,为后续的调整和优化提供指导和依据。

2.7 CP测试

CP测试是指芯片的Chip Probe测试,也称为芯片探针测试。它是在芯片制造过程中的一个关键步骤,用于验证芯片的电气特性和功能是否符合设计规格和要求。 CP测试通常在芯片封装之前进行,它涉及以下主要步骤:

芯片准备:在CP测试之前,需要对芯片进行准备工作,包括去除芯片表面的污染物和氧化物,以确保良好的接触性能。

探针制备:制备用于探测芯片引脚的探针。探针通常由细小的金属针组成,可以与芯片引脚接触并传递信号。

探针安装:将探针安装在探针卡上,探针卡是一个具有多个探针位置的载体,用于将探针与芯片引脚对齐。

探针测试:将芯片放置在测试台上,将探针卡与芯片引脚对齐,并施加适当的压力,使探针与芯片引脚接触。然后,通过测试设备向芯片引脚发送测试信号,并读取响应信号,以验证芯片的电气特性和功能。

数据分析:对探针测试的结果进行数据分析和处理,评估芯片的电气特性和功能是否符合设计规格和要求。

CP测试是芯片制造过程中的一个重要环节,它可以帮助检测和排除芯片制造过程中的缺陷和问题,确保芯片的质量和可靠性。同时,CP测试也可以提供有关芯片的电气特性和功能的重要信息,为后续的封装和测试工作提供指导和依据。

2.8 Bonding与封装

Bonding是指将芯片与封装基板之间进行电连接的过程。它是将芯片的引脚与封装基板上的金属线(或称为焊线)相连接的关键步骤。芯片bonding通常使用微焊接技术,可以分为以下几种常见的类型:

焊线键合(Wire Bonding):这是最常见的芯片bonding技术。它使用金属线(通常是金或铝)将芯片的引脚与封装基板上的焊盘连接起来。焊线键合可以分为球形焊线键合(Ball Bonding)和楔形焊线键合(Wedge Bonding)两种。

无线键合(Wireless Bonding):与焊线键合不同,无线键合使用无线连接器(Wireless Interconnects)将芯片的引脚与封装基板上的焊盘连接起来。无线键合通常使用微弹簧或弹性接触器来实现。

直接焊接(Flip Chip Bonding):这种bonding技术将芯片的引脚直接与封装基板上的焊盘相连接。芯片被翻转放置,使其引脚与焊盘对齐,并使用焊料将其连接起来。直接焊接可以提供更短的信号路径和更好的电气性能。

涂覆键合(Underfill Bonding):这是一种在焊线键合或直接焊接后使用的补充技术。涂覆键合使用特殊的填充材料(通常是环氧树脂)填充芯片和封装基板之间的空隙,以提供额外的机械支撑和保护。

Bonding是芯片封装过程中非常重要的一步,它确保芯片能够与封装基板之间进行可靠的电连接。不同的bonding技术适用于不同的应用和封装类型,选择适合的bonding技术可以提高芯片的可靠性和性能。 芯片封装是将芯片封装在外壳中,以保护芯片、提供引脚连接和散热等功能的过程。封装可以将芯片连接到外部电路和系统中,使其能够正常工作。 芯片封装的主要目的包括以下几个方面: