引言

ECC是微控制器系统中用于保障信息安全的常用机制,主要是避免存储设备中存放的数据因硬件干扰被篡改。国产车规微控制器原厂云途半导体设计和发布的YTM32微控制器芯片,全系配备了存储器的ECC机制,可以有效的增强芯片运行稳定性,避免因为内存位翻转导致芯片产生严重故障。本文将以YTM32微控制器芯片为例,对内存ECC的基本机制、实现原理和使用时的注意事项等进行介绍。

ECC的基本原理

ECC全称 Error Checking and Correcting,属于一种错误检查和纠正算法,典型的ECC算法一般可以做到纠正单比特错误和检查2比特错误。

在介绍ECC算法之前,先看一种简单的校验算法:奇偶校验。奇偶校验是在传输数据流的末尾,增加1个比特的校验信息,以保证完整的数据流中比特位的累加值一定是奇数或者偶数:若采用偶数校验的方式,发送方对偶数数据补充比特0,对于奇数数据补充比特1,这样发送的数据一定是偶数,接收方收到数据之后就对完整的数据帧进行判断, 如果不是偶数则代表数据出错。通过增加1个比特的额外数据,接收方就可以判断数据流是否正确,以实现对数据的校验。

但是,使用奇偶校验机制对数据有效性的判定能力有限:

若有2个比特数据发生反转,那么接收方依然会判定接收到的数据是正常数据;

如果有1个比特数据异常,接收方只能判断数据是异常的,并不能从接收到的数据恢复出正确的数据(因为无法判断具体是哪一位出现了异常)。

从上面两种情况来看,奇偶校验只能检验单个比特的数据错误。

基于奇偶校验算法,ECC校验算法通过增加更多的额外校验数据,以实现对传输数据的错误检查和错误纠正。

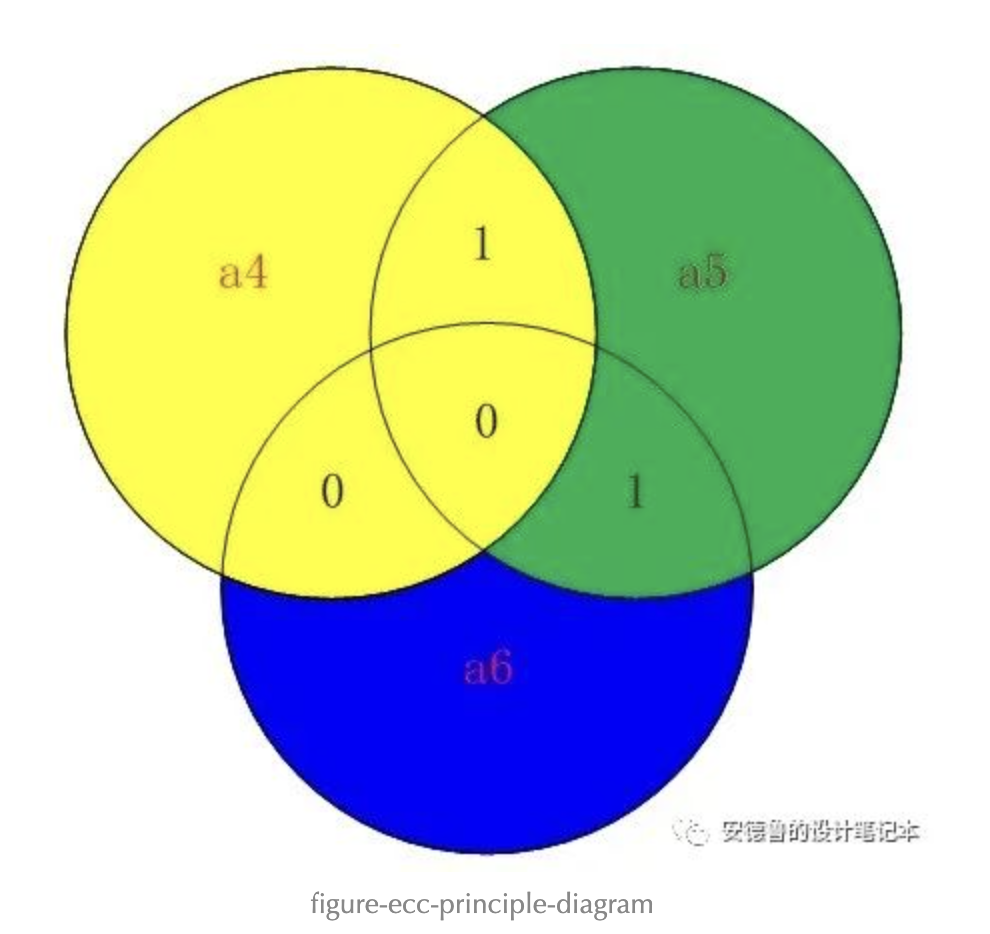

这里简单介绍ECC的实现原理。以4-bit ECC计算为例,如图x所示,假定3个不同颜色的圆相交的4个小格代表着4个bit的数据,与其他圆没有交集的那个格就代表着ECC bit,即a4,a5,a6。

figure-ecc-principle-diagram

图x 4-bit ECC计算方法

这里,人为设定一个规则: 每个圆内的4个bit异或结果为0 (类似于奇偶校验的机制)。当4个bit的数据位确定后,例如图中的1001,即可确定唯一ECC bit结果,即:a4=1,a5=0,a6=1。此时,发生任何1个bit的跳变(包括ECC bit),均可被检查出来并纠正,从而达到ECC的目的。此处描述的是,每个数据位都会和一些ECC位建立约束关系,但这些数据位同时还会同另一些ECC位存在约束关系,如此,通过数据冗余,形成“铁索连环”,相互照应。以此为基础,使用更多的ECC位(增加数据冗余),可以让数据更加“稳固”,但也会付出更多存储空间的代价。

最小ECC bit位数n要求 :2^n>数据位数+ECC位数n。

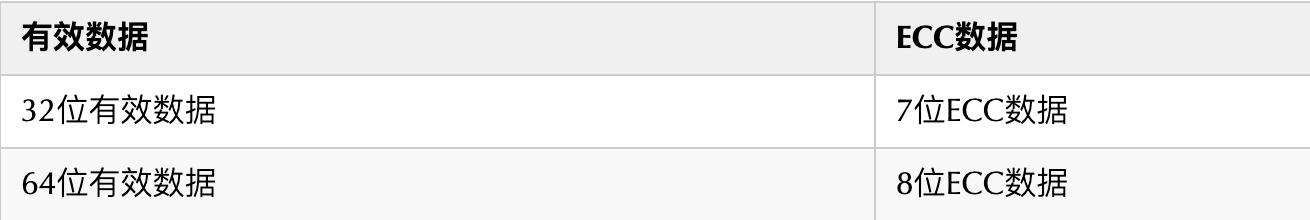

数据位每增加1倍,ECC只增加1位检验位。设计ECC时,可以设计数据位是8位对应的ECC需要增加5位来进行ECC错误检查和纠正,当数据位为16位时ECC位为6位,32位时ECC位为7位,数据位为64位时ECC位为8位,依此类推。

在实际应用芯片的场景中,存储单元(包含芯片内部SRAM和Flash)通常发生的是位数据的翻转,也就是单比特错误居多。针对这种错误,ECC一般可以实现1个比特的错误纠正和2个比特错误的检查,芯片的ECC组合一般是32+7和64+8的组合方式。如表x所示。

表x 常用的ECC数据长度

根据处理器特性和SRAM以及Flash的应用特性,通常在MCU中,一般对SRAM采用32+7的ECC校验方式,对Flash采用64+8的校验方式。

ECC RAM的访问方式和初始化

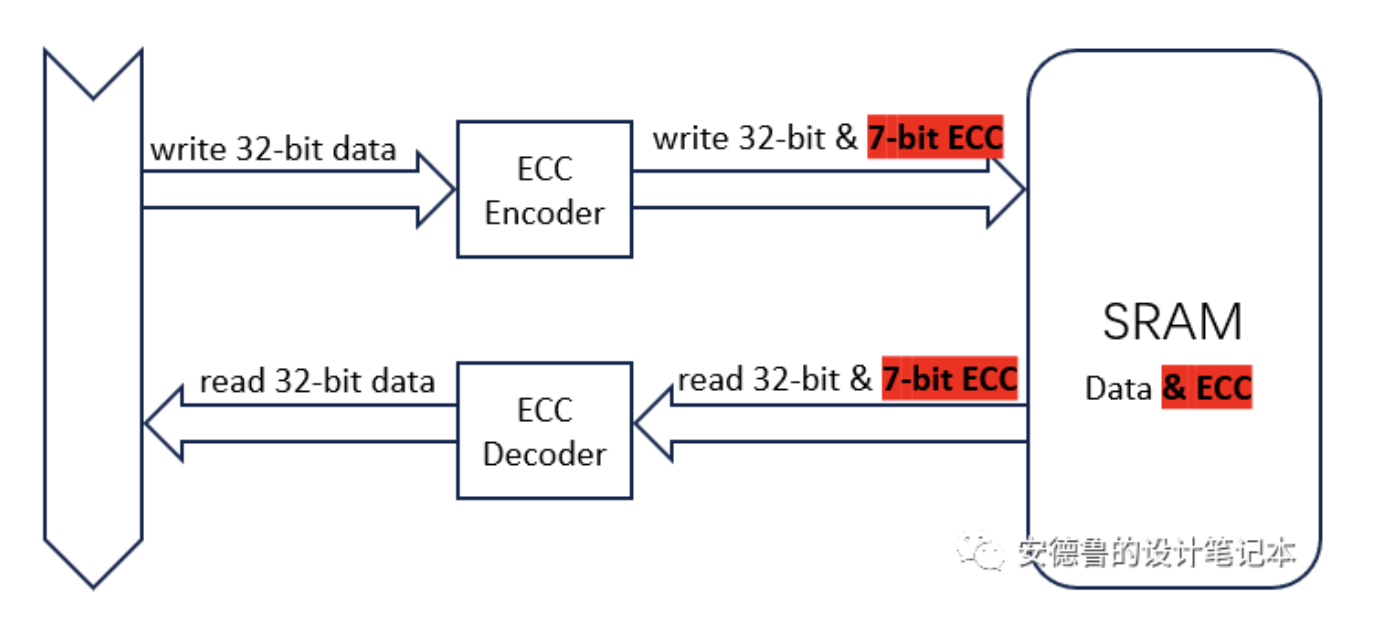

微控制器系统中的总线在读写支持ECC的SRAM时,会通过ECC编码器(Encoder)和ECC解码器(Decoder)对写入和读出的数据进行处理,如图x所示。

写入SRAM数据时,总线将计算好该数据对应的ECC,一并写入

从SRAM读数据时,总线同时读取数据和ECC校验信息,之后根据ECC对数据进行校验,然后才将数据返回系统中使用

figure-bus-access-ecc-mem

图x MCU总线读写带有ECC的SRAM

在图x中可以看到,总线对于SRAM的读写都是以32位的带宽进行操作的,嵌入在32位总线上的ECC编码器和解码器也是基于32位数操作的,但是,软件中有很多基于字节或者半字的操作方式,对于这种情况,总线并不能直接以字节或者半字节的方式向SRAM存储区中写数,SRAM控制器首先会读出SRAM中原有的32位数,修改这个数,重新计算ECC,然后将新的数据和ECC计算的结果一并写入到SRAM中。

SRAM存储器中的内容在上电之后内容是随机的,其中的有效数据和ECC数据并未建立起关联。此时,如果读取SRAM的内容并进行ECC校验,大概率上是会出现ECC错误的。因此,在使用支持ECC的SRAM之前,需要手动对SRAM进行初始化操作。初始化SRAM的操作,就是简单地向SRAM中按照32位的宽度写入一个任意值,通过ECC编码器计算好ECC数据并填充SRAM存储器即可。注意,初始化的时候必须要按照32位的形式写入,否则若按照字节或者半字的方式写入的时候,系统会先读后写,最初读到的数也是错的,会出现ECC错误。

ECC的初始化过程一般会被放在MCU的启动汇编代码中,此时尚未初始化ECC,不能使用建立在ECC内存中的堆栈。以YTM32微控制器芯片为例,其启动程序使用如下代码实现对ECC的初始化:

#ifndef START_NO_ECC_INIT

/* Init ECC RAM */

ldr r1, =__RAM_START

ldr r2, =__RAM_END

subs r2, r1

subs r2, #1

ble .LC5

movs r0, 0

movs r3, #4

.LC4:

str r0, [r1]

add r1, r1, r3

subs r2, 4

bge .LC4

.LC5:

#endif

上述代码中,可以通过定义

START_NO_ECC_INIT

宏配置初始化时绕过ECC初始化,ECC的初始化范围是从

__RAM_START

至

__RAM_END

,这两个地址是在linker文件中定义的,用户可以根据应用需求修改相应的地址范围。注意,这里设置初始化ECC的地址区域越大,系统启动的时间将会越长。

YTM32芯片在SRAM产生ECC错误时,会产生Bus Error或者Hard Fault。

用户在使用过程中,如果发现芯片在单步调试过程中使用正常(在断点时,调试器会扫描存储空间),但是在芯片重新上电之后就会出现异常,就可以检查一下是否SRAM ECC没有正常初始化,例如上述过程中的

START_FROM_FLASH

宏定义是否在汇编调试阶段有定义(针对旧版本SDK)。

还有一种判定ECC未正常初始化的方式,可通过调试器查看系统的SRAM,如果发现有的SRAM可以读,有的SRAM地址无法正确读,那么就是ECC没有正常初始化。

RAM ECC错误注入及EMU外设

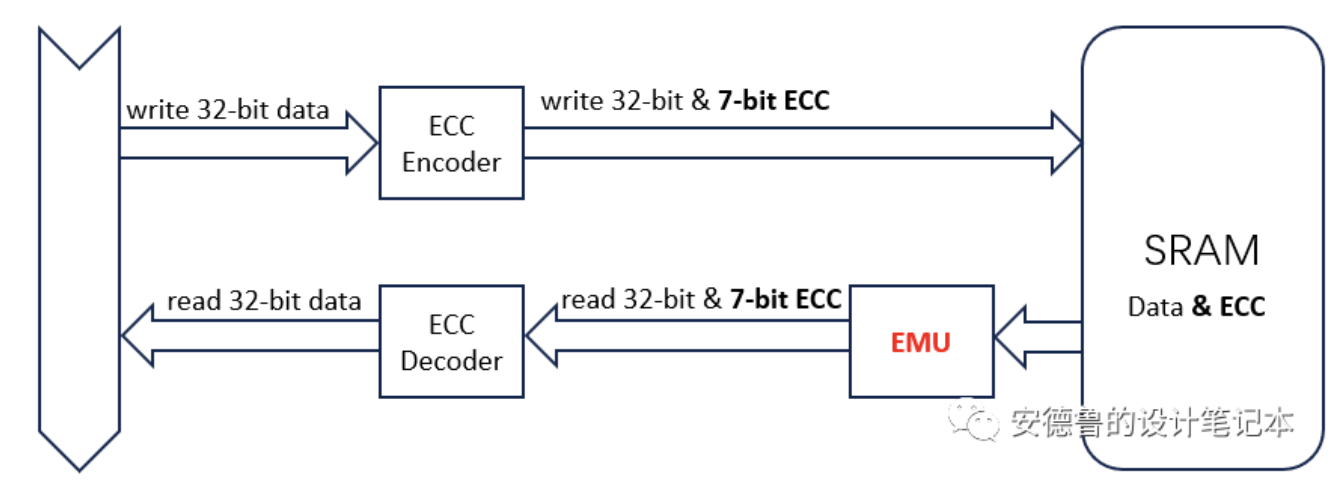

在程序开发过程中,考虑到功能安全的需求,还需要考虑出现ECC错误情况的处理机制。实际上,SRAM上比特位翻转是一个小概率事件,在常规测试过程很难复现。工程师圈子里有一句广为流传的口号,“有困难要上,没有困难制造困难也要上”。为了人为创造ECC错误的情况(以便开发ECC错误处理过程),YTM32的为控制上设计了一个EMU(ECC Management Unit)的外设模块,专门用于主动产生和捕获ECC错误。

EMU模块在ECC过程中的位置,如图x所示。

figure-emu-diagram

图x EMC在ECC过程中的位置

EMU实际上是在SRAM的读过程中增加的一个模块,将从SRAM的读取的数据同EMU设置的一个mask进行异或运算,从而对读取数据的某个位进行翻转(以产生错误数据),然后送入ECC解码器,从而模拟SRAM出现ECC错误。

另外,EMU还会监测ECC解码器的结果,当产生ECC错误的时候,EMU会捕获这个异常,并记录出现ECC错误的地址和异常类型(单比特错误还是多比特错误)。应用中,可通过读取EMU的错误信息,进而决定如何处理ECC错误。

对于ECC错误的处理方式,可以分为如下几种情况:

如果系统允许复位的话,可以直接记录诊断信息后复位运行,这样SRAM整体都会重新初始化成正常内容

针对单比特错误,因为ECC可以直接纠正结果,可以直接读取产生ECC错误地址上的内容,然后将内容重新写回到该地址,即可恢复正常。注意,如果ECC错误是通过EMU模拟实现的,此时就需要关闭EMU注入通道,否则再次读取的时候依然会有ECC错误,另外因为ECC是纠1检2的算法,如果出现多于2比特的错误,这种情况SRAM的读取结果可能会有正常、单比特错误和多比特错误几种结果。

针对多比特错误,因为无法恢复正确信息,应用只能向错误地址写入一个默认值,或者通过复位操作恢复正常值。

Flash ECC校验

Flash内部也是通过电荷状态来存储信息的,虽然Flash中电荷的状态大部分时间都是稳定的,但是当受到某些干扰之后,Flash中电荷状态也有可能发生反转。所以,车规芯片对Flash的ECC校验也提出了要求。因为Flash不支持随机的写入,所以ECC的操作方面相对SRAM比较简单。

首先,Flash初始时擦除状态,有效数据全是1,而对应的ECC算法可以保证全1的ECC校验值也是全1(巧妙啊),也就是说,Flash擦除状态下,对Flash的读操作并不会产生ECC错误。而对Flash的写入都是通过一系列的命令实现的,在写入的时候,硬件会自动计算好ECC,再将有效数据和ECC校验值一并写入到Flash的存储区中。写入完成之后,用户正常读取数据内容即可。这种情况,即使Flash出现单比特的错误,ECC解码器也可以正常纠正,以保证有效数据的完整性。

对于功能安全要求比较高的程序,应用程序还需要针对Flash的ECC进行处理,和SRAM ECC错误处理的方式类似,Flash ECC错误处理可以分为如下几种形式:

当出现单比特数据错误,由于总线可以自动恢复正确的原始数据,应用程序可以先记录相应的诊断数据,然后备份Flash出错数据所在的扇区,再将扇区擦除后,从备份地址将原有数据重新写入到擦除后到扇区。

当出现多比特数据错误,如果错误出现在程序区域,那么只能记录诊断数据,然后尝试运行备份APP程序,尝试系统复位,或者重新下载程序。

当出现多比特错误错误,如果错误出现在数据区域,那么应用程序需要尝试使用默认值填充错误区域,相当于重新下载程序。

总之,当检测到Flash出现ECC错误时,Flash存储器的内容已经有风险,必须将出现错误的扇区进行擦除和重新编程才能从根本上清除掉ECC错误。当然,同一个地址产生多位的翻转概率还是非常低的,考虑到设计实现这种自恢复的机制也需要消耗相当的成本(更长的开发周期,更复杂的应用程序,更大的物理存储空间),开发者可以酌情采取应对策略。