Ⅰ、概述

对于系统时钟应该都知道它的作用,就是驱动整个芯片工作的心脏,如果没有了它,就等于人没有了心跳。

对于使用开发板学习的朋友来说,RCC系统时钟这一块知识估计没怎么去配置过,原因在于开发板提供的晶振基本都是官方标准的时钟频率,使用官方的标准库,这样系统时钟就是默认的配置,也就是默认的频率。但对于自己设计开发板,或者想要改变系统时钟频率(如:降低功耗就需要降频)的朋友来说,配置系统时钟就有必要了。

关于时钟这一块对定时器(TIM、RTC、WDG等)相关的外设也比较重要,因为要求精准,就需要时钟频率精准。

Ⅱ、关于时钟

1.时钟分类

STM32芯片(所有型号)的时钟包含4类:

HSE(High Speed External)高速外部时钟

HSI(High Speed Internal)高速内部时钟

LSE(Low Speed External)低速外部时钟

LSI(Low Speed Internal)低速内部时钟

2.时钟源

STM32芯片(所有型号)驱动系统时钟的时钟源:

HSI内部高速时钟

HSE外部高速时钟

PLLCLK倍频时钟

STM32具有以下两个次级时钟源:

32 kHz 低速内部 RC (LSI RC),该 RC 用于驱动独立看门狗,也可选择提供给 RTC 用于停机/待机模式下的自动唤醒。

32.768 kHz 低速外部晶振( LSE 晶振),用于驱动 RTC 时钟 (RTCCLK)。对于每个时钟源来说,在未使用时都可单独打开或者关闭,以降低功耗。

3.时钟树(框图)

关于STM32的时钟树针对不同系列芯片可能存在差异。F0、F1和F3系列芯片(主流芯片,频率相对较低)有很多相似的地方,F2和F4(高性能芯片)系列芯片有很多相似的地方。但是,F3芯片和F4芯片的时钟树之间却存在很大差异,具体请看参考手册RCC相关章节。

STM32时钟控制器为应用带来了高度的灵活性,用户在运行内核和外设时可选择使用外部晶振或者使用振荡器,既可采用最高的频率,也可为以太网、 USB OTG FS 以及 HS、 I2S 和 SDIO等需要特定时钟的外设保证合适的频率。

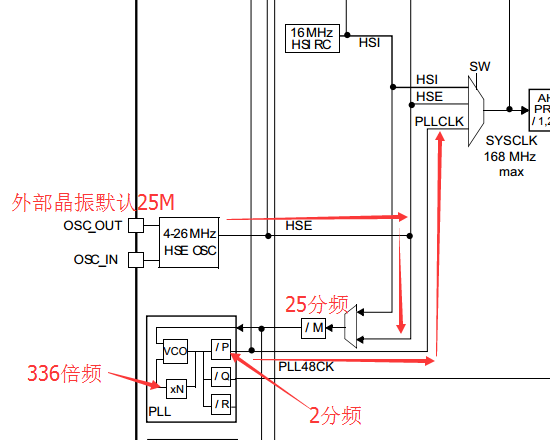

以F417芯片为例:可通过多个预分频器配置 AHB 频率、高速 APB (APB2) 和低速 APB (APB1)。 AHB 域的最大频率为 168 MHz。高速 APB2 域的最大允许频率为 84 MHz。低速 APB1 域的最大允许频率为 42 MHz。实际上输出的最大时钟可以适当提高一点,但为了保证在多种环境下,最好还是不要超过标准的最大值。

STM32F4xx 器件具有两个 PLL:

主 PLL (PLL) 由 HSE 或 HSI 振荡器提供时钟信号,并具有两个不同的输出时钟:

第一个输出用于生成高速系统时钟(最高达 168 MHz)

第二个输出用于生成 USB OTG FS 的时钟 (48 MHz)、随机数发生器的时钟

专用 PLL (PLLI2S) 用于生成精确时钟,从而在 I2S 接口实现高品质音频性能。

由于在 PLL 使能后主 PLL 配置参数便不可更改,所以建议先对 PLL 进行配置,然后再使能(选择 HSI 或 HSE 振荡器作为 PLL 时钟源,并配置分频系数 M、 N、 P 和 Q)。

PLLI2S 使用与 PLL 相同的输入时钟( PLLM[5:0] 和 PLLSRC 位为两个 PLL 所共用)。但是, PLLI2S 具有专门的使能/禁止和分频系数( N 和 R)配置位。在 PLLI2S 使能后,配置参数便不能更改。

Ⅲ、代码分析

以STM32F4x5、x7系列芯片为例来分析一下系统时钟的配置。

参考软件工程:

https://yunpan.cn/cRepWDShSK4yc访问密码 65b1

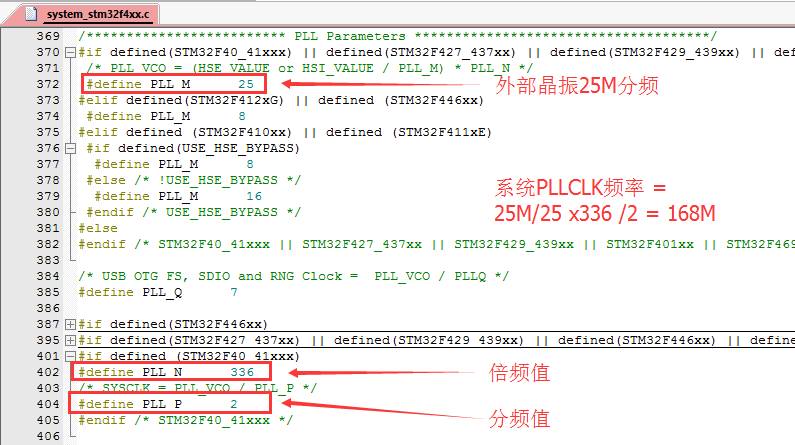

1.倍频参数

结合上面时钟树和源代码可以看得出来,系统时钟PLLCLK的计算主要是配置PLL_M、PLL_N、PLL_P这三个参数,最后168M是通过分频、倍频得出来的。

2.验证时钟频率

对于STM32芯片来说,验证系统时钟最终运行多大的速度,最准确的验证方法的用示波器测试它的系统时钟。

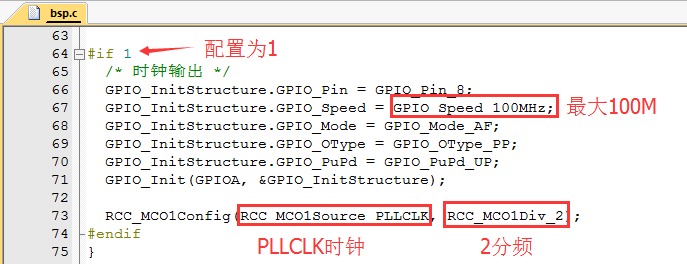

这里描述一下怎样用示波器来测试系统时钟。其实很简单,就是在软件代码里面配置时钟输出(这里可以输出多种类型的时钟HSE、HSI、PLLCLK等),根据代码配置不同,相应输出的时钟就不同。请看源代码:

我提供的代码里面就有这一选项,将定义配置为1,就打开了这个功能。时钟输出的参数有两个,时钟源,分频值。注意:这里的最大输出时钟是100M,所以PLLCLK时钟分频之后才能输出,不然你用示波器检测不到波形(我测试过了)。

最后输出的波形如图:

Ⅳ、说明

关于STM32的开发,软件兼容性是很好的,不要觉得你的芯片和我总结的实例有差异就不看了,其实是错误的认识,特别是同一个系列的芯片基本上程序都兼容,也就是可以互相使用。