根据计划,台积电最新的N2(2nm)制程 将于明年下半年开始量产,目前台积电正在尽最大努力完善该技术,以降低可变性和缺陷密度,从而提高良率。不久前,一位台积电员工最近对外透露,该团队已成功将N2测试芯片的良率提高了6%,为公司客户“节省了数十亿美元”。 而根据最新的爆料称,台积电N2目前的良率已经达到了60%。不过这些信息尚未得到进一步证实。

而在上周于美国旧金山举行的 IEEE 国际电子设备会议(IEDM)上,台积电研发和先进技术副总裁Geoffrey Yeap披露了有关其 N2制程工艺的更多细节。

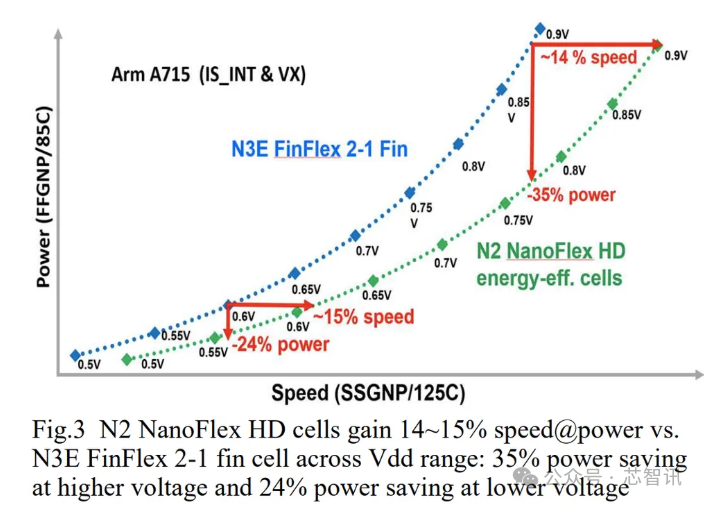

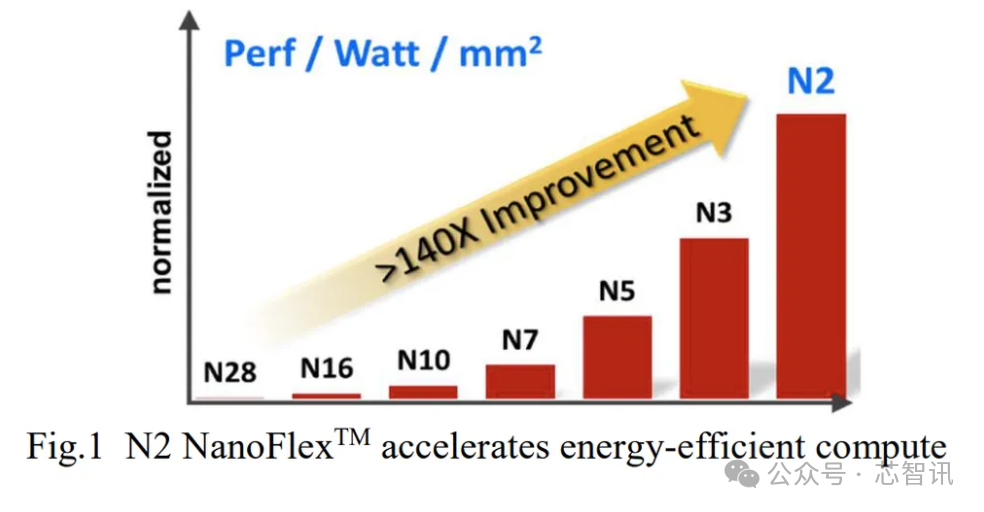

据介绍,N2制程在相同电压下可以将功耗降低 24% 至 35%,或将性能提高15%,晶体管密度比上一代 3nm 工艺高 1.15 倍。而这些指标的提升主要得益于台积电的新型全环绕栅极(GAA)纳米片晶体管,以及 N2 NanoFlex 设计技术协同优化和其他一些增强功能实现的。

其中, 全环绕栅极纳米片晶体管允许设计人员调整其通道宽度,以平衡性能和功率效率。

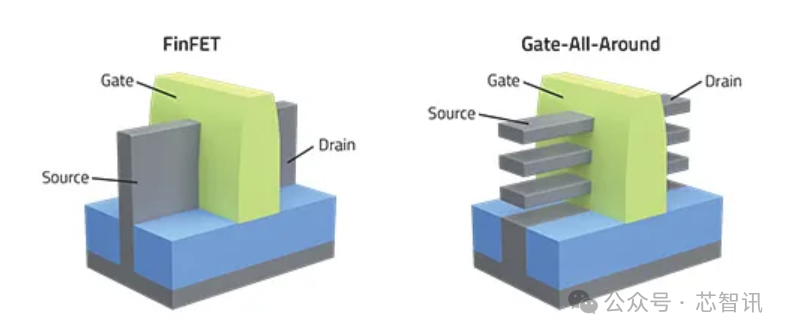

Geoffrey Yeap进一步解释称, N2是台积电“四年多的劳动成果”,今天的 FinFET 晶体管的核心有一个垂直的硅片,而全环绕栅极纳米片晶体管有一堆狭窄的硅带。这种差异不仅提供了对流经器件的电流的更好控制,还允许工程师通过制造更宽或更窄的纳米片来生产更多种类的器件。FinFET只能通过乘以器件中的翅片数量来提供这种多样性,例如具有一个、两个或三个翅片的器件。但 全环绕栅极纳米片 为设计人员提供了介于两者之间的渐变选择,例如相当于 1.5 个翅片或任何可能更适合特定逻辑电路的东西。

台积电将该技术称为 Nanoflex,允许在同一芯片上使用不同的纳米片宽度构建不同的逻辑单元。即由窄器件制成的逻辑单元可能构成芯片上的通用逻辑,而那些具有更宽纳米片、能够驱动更多电流和更快开关的逻辑单元将构成 CPU 内核。

简单来说,该技术使设计人员能够开发具有最小面积和更高功率效率的窄单元,或为实现最佳性能而优化的宽单元。该技术还包括六个电压阈值电平 (6Vt),范围为 200mV,使用台积电第三代基于偶极子的集成实现,同时具有 n 型和 p 型偶极子。

N2 制程在工艺和器件层面引入的创新不仅旨在通过细化片材厚度、结、掺杂剂活化和应力工程来提高晶体管驱动电流,还旨在降低有效电容 (Ceff) 以实现一流的能效。总的来说,这些改进使 N 型和 P 型纳米片晶体管的 I/CV 速度分别提高了约 70% 和 110%。

与 FinFET 晶体管架构相比,N2的 全环绕栅极 纳米片晶体管在 0.5V 至 0.6V 的低电源电压范围内可提供明显更好的每瓦性能,其中工艺和设备优化将时钟频率提高了约 20%,并在 0.5V 工作时将待机功耗降低了约 75%。此外,集成 N2 NanoFlex 和多阈值电压 (multi-Vt) 选项,为高逻辑密度的节能处理器提供了额外的设计灵活性。

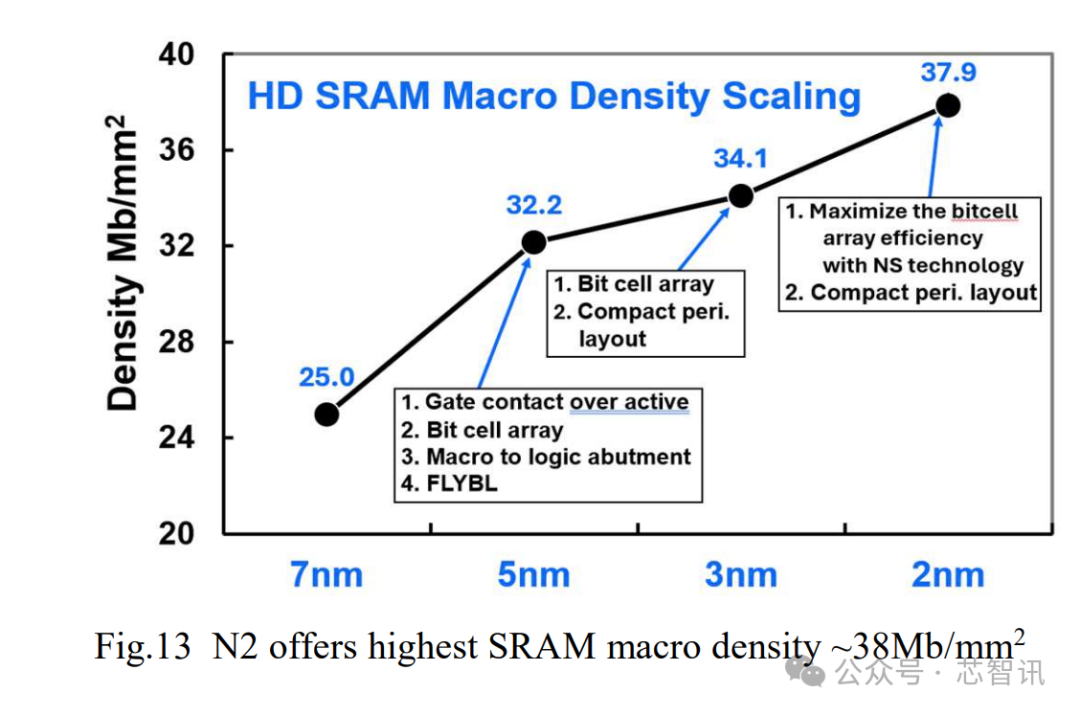

台积电N2的晶体管架构和 DTCO 优势直接影响 SRAM 可扩展性,而近年来,前沿节点很难实现这一点。

借助 N2,台积电成功实现了创纪录的约 37.9Mb/mm² 的 2nm SRAM 密度。而根据最新曝光的资料显示,Intel 18A 的SRAM密度约为31.8 Mb/mm² , 显然台积电N2的SRAM密度更高。同时也比N3制程提高了11%。而N3仅比自己的前代提高了6%。

除了创下创纪录的 SRAM 密度外,台积电N2还降低了其功耗。由于 GAA 纳米片晶体管具有更严格的阈值电压变化 (Vt-sigma),因此与基于 FinFET 的设计相比,N2 的大电流 (HC) 宏的最小工作电压 (Vmin) 降低了约 20mV,高密度 (HD) 宏的最小工作电压 (Vmin) 降低了 30-35mV。这些改进使 SRAM 读写功能稳定到大约 0.4V,同时保持稳健的良率和可靠性。

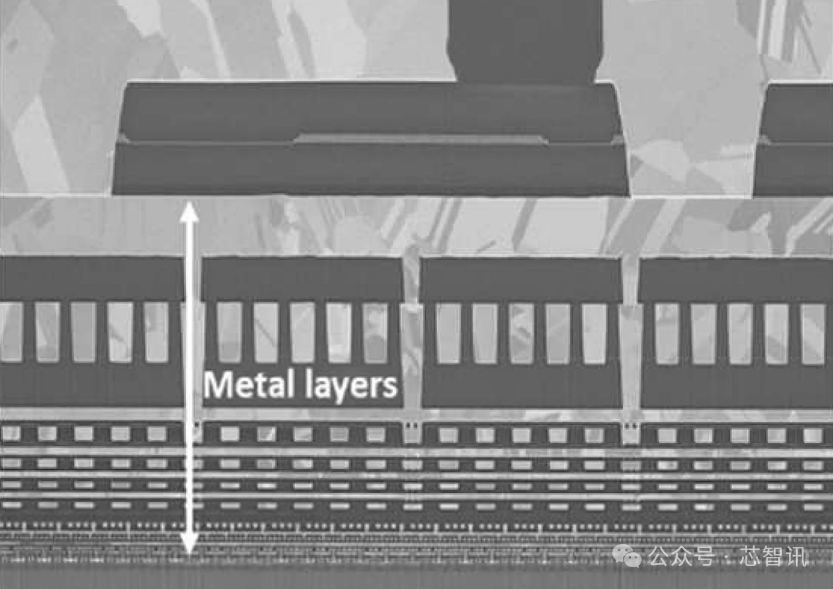

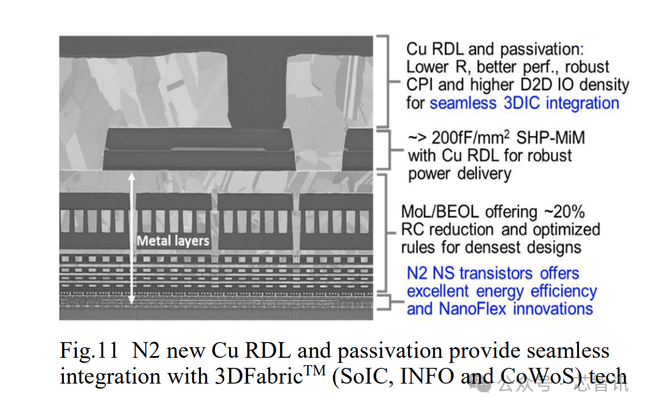

除了新的晶体管外,台积电N2还采用了全新的 无屏障的全钨 中间线 (MoL,middle-of-line)层、后端布线 (BEOL,back-end-of-line) 和远 BEOL 布线,将电阻降低了 20% 并提高了性能效率。N2 的 MoL 现在使用无障碍钨丝,将垂直栅极接触 (VG) 电阻降低了 55%,并将环形振荡器的频率提高了约 6.2%。

此外,第一个金属层 (M1) 现在在一个 EUV 曝光通道中创建,然后是一个蚀刻步骤 (1P1E),从而降低了复杂性,减少了掩模数量,并提高了整体工艺效率。

Yeap 表示, 优化的 M1 采用新颖的 1P1E EUV 图形,使标准电池电容降低了近 10%,并节省了多个 EUV 掩模。“总之,N2 MoL 和 BEOL RC 降低了约超过20%,为节能计算做出了重大贡献。”

此外,N2 用于 HPC 应用的额外功能包括超高性能 MiM (SHP-MiM) 电容器,可提供约 200fF/mm² 的电容,这有助于通过减少瞬态电压下降来实现更高的最大工作频率 (Fmax)。

据台积电称,N2 技术具有具有平坦钝化和 TSV 的新型 Cu RDL 选项,该选项针对面对面和面对面的 3D 堆叠进行了优化,SoIC 键合间距为 4.5 μm,这将成为 AI、HPC 甚至移动设计的可用功能。

目前台积电 N2 处于风险生产阶段,并 计划于 2025 年下半年量产。另一种被称为 N2P 的工艺正在开发中。N2P 是 N2 的增强版本,预计将带来5%的性能提升,具有完全的 GDS 兼容性。预计将于 2025 年完成资格认证阶段,计划于 2026 年量产。

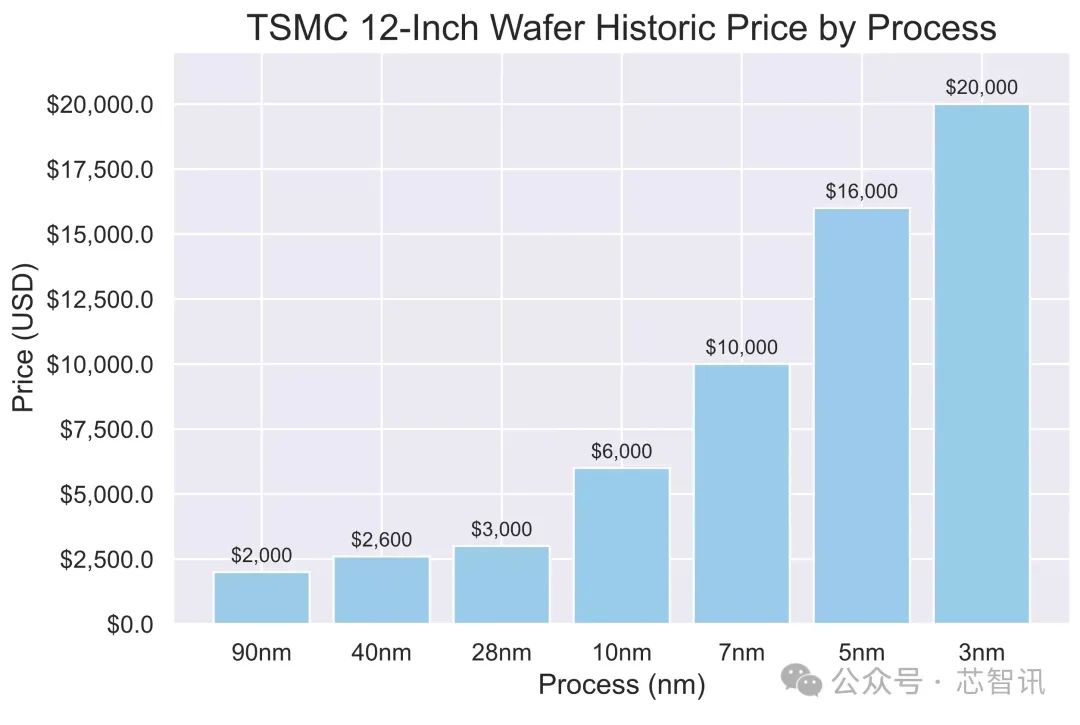

对于客户来说,随着台积电N2的量产,届时2nm晶圆的代工报价可能将达到2.5万-3万美元/片,远高于当前3nm晶圆约2万美元/片的价格。

但是N2所能够带来的晶体管密度提升、性能提升或功耗降低则相对有限,再加上初期的良率问题,这也意味着一片12英寸2nm晶圆所能够切出来的可用的单颗芯片的成本将会大幅提升,显然这将会抑制可能客户对于2nm制程的采用。

预计初期能够用得起台积电2nm制程的客户只有苹果公司、英伟达、AMD、高通和联发科等少数头部客户,但是从产品规划来看,英伟达和AMD在2026年可能都将不会采用2nm制程,相对来说苹果、高通、联发科则有可能会在2026年的旗舰芯片上采用。

来源:芯智讯-浪客剑