近年来,SiC MOSFET作为一种开关器件,被广泛用于各种电源应用和电源线路中。之所以得以快速普及,原因之一是与传统功率半导体相比,它支持高速开关工作。然而,由于开关时电压和电流急剧变化,器件本身的封装电感和外围电路的布线电感的影响已经不容忽视,最终导致漏极和源极之间会产生较大的浪涌。需要确保这种浪涌不超过所用SiC MOSFET的最大额定值,有多种抑制浪涌的方法可以达到这个目的,其中之一便是添加缓冲电路。

在本系列文章中,我们将为您介绍如何设计缓冲电路。

-

漏极和源极之间产生的浪涌

-

缓冲电路的种类和选择

-

C缓冲电路的设计

-

RC缓冲电路的设计

-

放电型RCD缓冲电路的设计

-

非放电型RCD缓冲电路的设计

漏极和源极之间产生的浪涌

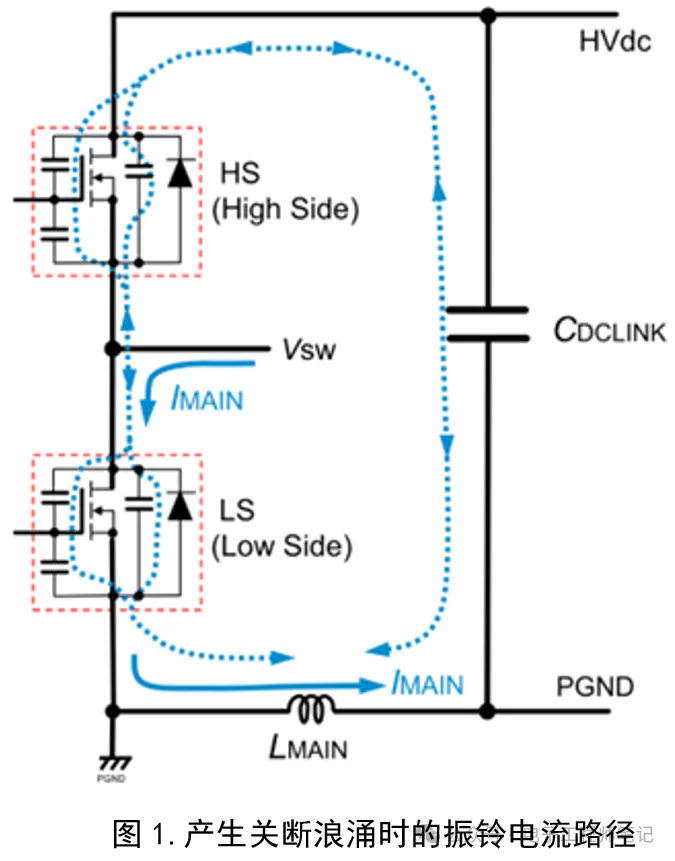

开关导通时,线路和电路板版图的电感之中会直接积蓄电能(电流能量)。当该能量与开关器件的寄生电容发生谐振时,就会在漏极和源极之间产生浪涌。下面将利用图1来说明发生浪涌时的振铃电流的路径。这是一个桥式结构,在High Side(以下简称HS)和Low Side(以下简称LS)之间连接了一个开关器件,该图是LS导通,电路中存在开关电流IMAIN的情形。通常,该IMAIN从VSW流入,通过线路电感LMAIN流动。

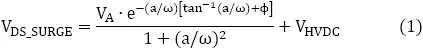

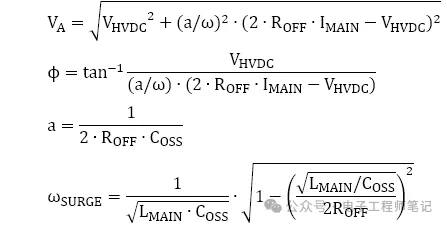

接下来,LS关断时,流向LMAIN的IMAIN一般是通过连在输入电源HVdc和PGND之间的大容量电容CDCLINK,经由HS和LS的寄生电容,按照虚线所示路径流动。此时,在LS的漏极和源极之间,LMAIN和SiC MOSFET的寄生电容COSS(CDS+CDG)就会产生谐振现象,漏极和源极之间就会产生浪涌。如果用VDS_SURGE表示施加在HVdc引脚的电压,用ROFF表示MOSFET关断时的电阻,则该浪涌的最大值VHVDC可以用下述公式表示(*1)。

但是,

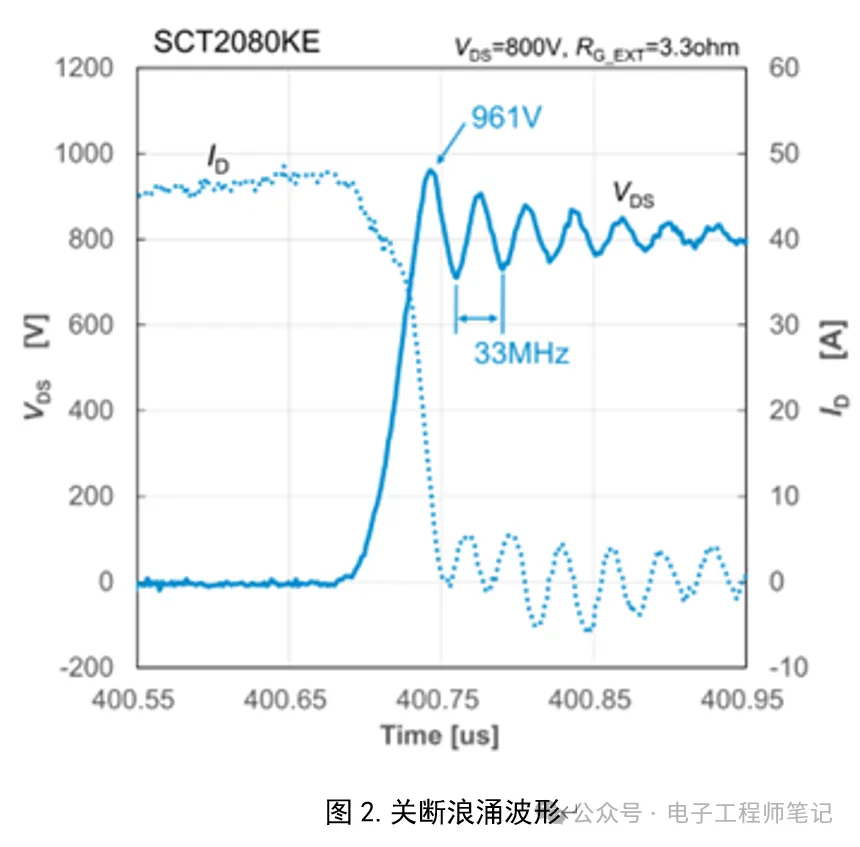

图2是使用SiC MOSFETSCT2080KE进行测试时关断时的浪涌波形。当给HVdc施加800V的电压时,可以算出VDS_SURGE为961V,振铃频率约为33MHz。利用公式(1),根据该波形,可以算出LMAIN约为110nH。

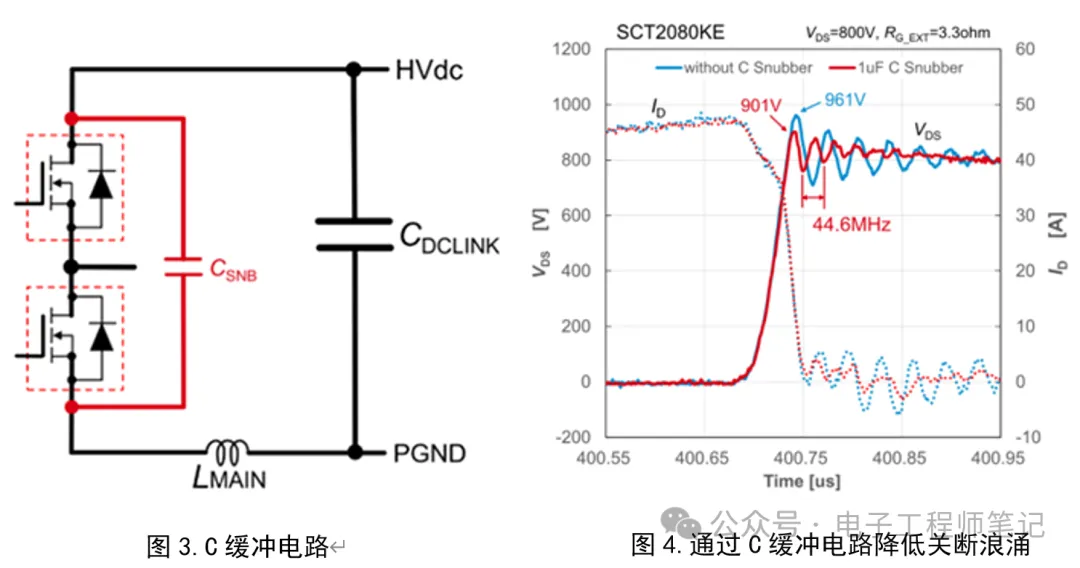

再接下来,增加一个图3所示的缓冲电路CSNB,实质性地去掉LMAIN后,其关断浪涌的波形如图4所示。

可以看到,增加该CSNB之后,浪涌电压降低50V以上(约901V),振铃频率也变得更高,达到44.6MHz,而且包括CSNB在内,整个电路中的LMAIN变得更小。

同样,利用公式(1)计算LMAIN,其结果由原来的110nH左右降低至71nH左右。原本,最好是在进行版图设计时,将线路电感控制在最低水平。但是,在实际设计过程中,往往会优先考虑器件的散热设计,所以线路并不一定能够按照理想进行设计。

在这种情况下,其对策方案之一就是尽可能在开关器件附近配置缓冲电路,使之形成旁路电路。这样既可以将线路电感这一引发浪涌的根源降至最低,还可以吸收已经降至最低的线路电感中积蓄的能量。然后,通过对开关器件的电压进行钳制,就可以降低关断浪涌。

缓冲电路的种类和选择

缓冲电路包括由电阻器、线圈、电容器等无源元件组成的电路,以及由半导体元器件组成的有源电路 (*1)。在这里将为您介绍无需控制且具有成本优势的电路方式。

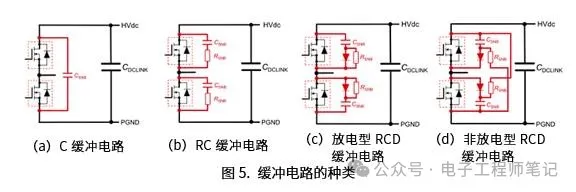

图5为缓冲电路示例。四个电路分别是:在桥式结构的SiC MOSFET上下方一并连接电容器CSNB的(a)C缓冲电路、在各开关器件的漏极和源极之间连接电阻器RSNB和电容器CSNB的(b)RC缓冲电路、在RC缓冲电路中添加了二极管的(c)放电型RCD缓冲电路、以及将RDC缓冲电路的放电路径改变后的(d)非放电型RCD缓冲电路。

为了使这些缓冲电路充分发挥其效用,必须将它们尽可能地靠近开关器件进行安装。

(a)C缓冲电路的元器件数量较少,但由于必须配置在桥式结构的上下之间,因此存在布线长度较长的缺点,这种电路方式多用于由分立结构二合一组成的模块中。

(b)RC缓冲电路可以配置在各开关器件的附近,但每当开关器件导通时,存储在CSNB中的能量必须由RSNB全部消耗掉(在桥式结构的情况下,同步侧存储在CSNB中的能量在死区时间内被回收)。因此,在这种方式中,当开关频率提高时,RSNB消耗的功率甚至达到几瓦的程度,而CSNB不能过大,浪涌抑制效果往往有限。另外,RSNB限制了浪涌吸收能力,这也导致浪涌抑制效果受限。

对于(c)放电型RCD缓冲电路而言,RSNB消耗的功率与(b)RC缓冲电路相同,但由于浪涌仅经由二极管来吸收,因此其浪涌吸收效果优于(b),更具实用性。但是,需要注意所用二极管的反向恢复特性,另外还要考虑到吸收浪涌时的电流变化较大,需要尽量减小缓冲电路的布线电感等。此外,即使将RSNB与CSNB并联连接,它们在工作上也是相同的。

至于(d)非放电型RCD缓冲电路,RSNB只消耗CSNB所吸收的浪涌能量,所以不必在每次开关时将CSNB中存储的能量全部放电。因此,即使提高开关频率,RSNB的功耗也不会增加太多,故可增加CSNB的容量,从而可构建出浪涌抑制效果非常出色的电路。然而,这种方式的缓冲电路,其布线布局更复杂,除非使用四层以上的电路板,否则很难实现。

前面介绍的缓冲电路各有优缺点,因此需要根据电源电路的结构和转换功率容量来选择最合适的缓冲电路。

C缓冲电路的设计

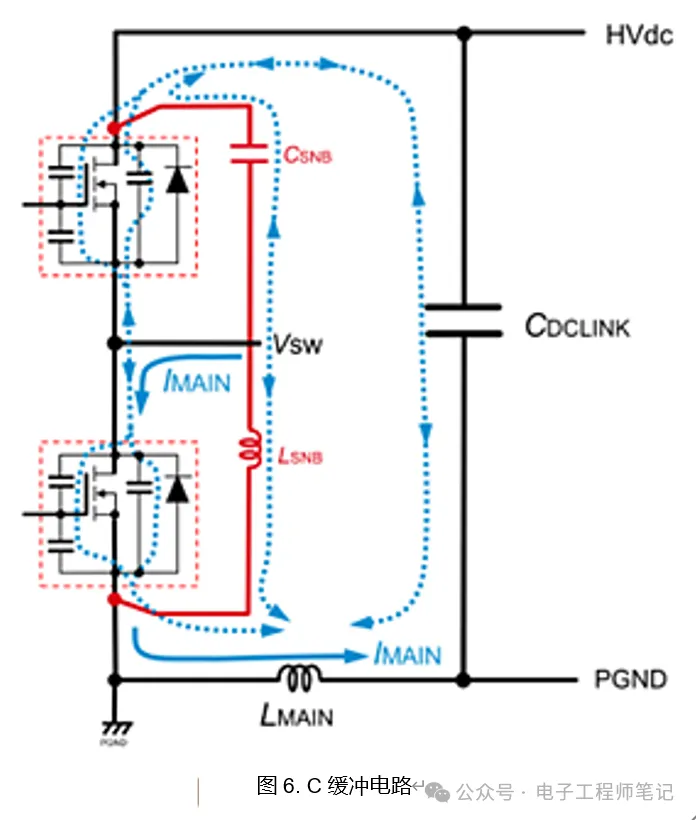

图6所示的C缓冲电路是通过CSNB吸收LMAIN积蓄的能量的。因此,缓冲电路中形成的LSNB需要低于LMAIN。CSNB中积蓄的能量基本上不会被释放(放电),因此电容量越大,浪涌抑制效果越好,但关于LSNB,还需要考虑所用电容器的等效串联电感(ESL)。

通常ESL会随着电容器尺寸的增大而增大,因此在选择电容量时需要注意这一点。假设LMAIN中积蓄的能量全部被CSNB吸收,那么可以根据公式(2)计算得出的电容量来选择电容器。

RC缓冲电路的设计

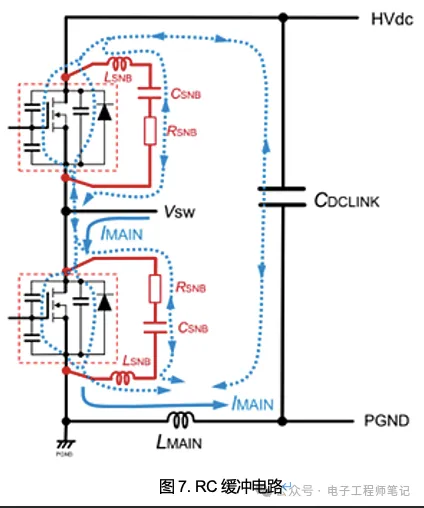

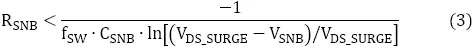

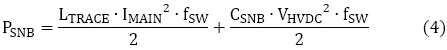

图7表示RC缓冲电路工作时的电流路径。按照与“C缓冲电路的设计”中相同的公式(2)来确定CSNB。RSNB的参考值可通过下面的公式(3)求得。

fSW:开关频率

VSNB:放电缓冲电压(VDS_SURGE的0.9倍)

确定RSNB后,利用公式(4)计算RSNB消耗的功率PSNB,然后选择能够容许该损耗的电阻器。

在RC缓冲电路中,增加了公式(4)中的第二项,fSW或VHVDC越高,RSNB消耗的功率就越大,因此,当PSNB很大、电阻器选型困难时,需要降低CSNB的电容值并重新计算。

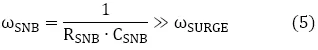

另外,要想使RC缓冲电路能够充分吸收浪涌,RSNB和CSNB的谐振角频率ωSNB必须充分高于浪涌的谐振角频率ωSURGE,所以需要确认公式(5)中的RC缓冲电路的谐振角频率ωSNB。

放电型RCD缓冲电路的设计

放电型RCD缓冲电路的设计与RC缓冲电路的设计基本相同,但由于浪涌被二极管吸收,因此无需使用“RC缓冲电路的设计”一文中所示的公式(5)来确认谐振频率。

但是,如果所使用的二极管的反向恢复电流较大,则在高频工作时二极管的损耗也会比较大,因此要想减少缓冲电路的损耗,就需要选择反向恢复电流尽可能小的二极管。

另外,由于吸收浪涌时的电流变化较大,所以还需要考虑尽量减小缓冲电路中的布线电感。

部分电子书籍截图