作者:电子创新网张国斌

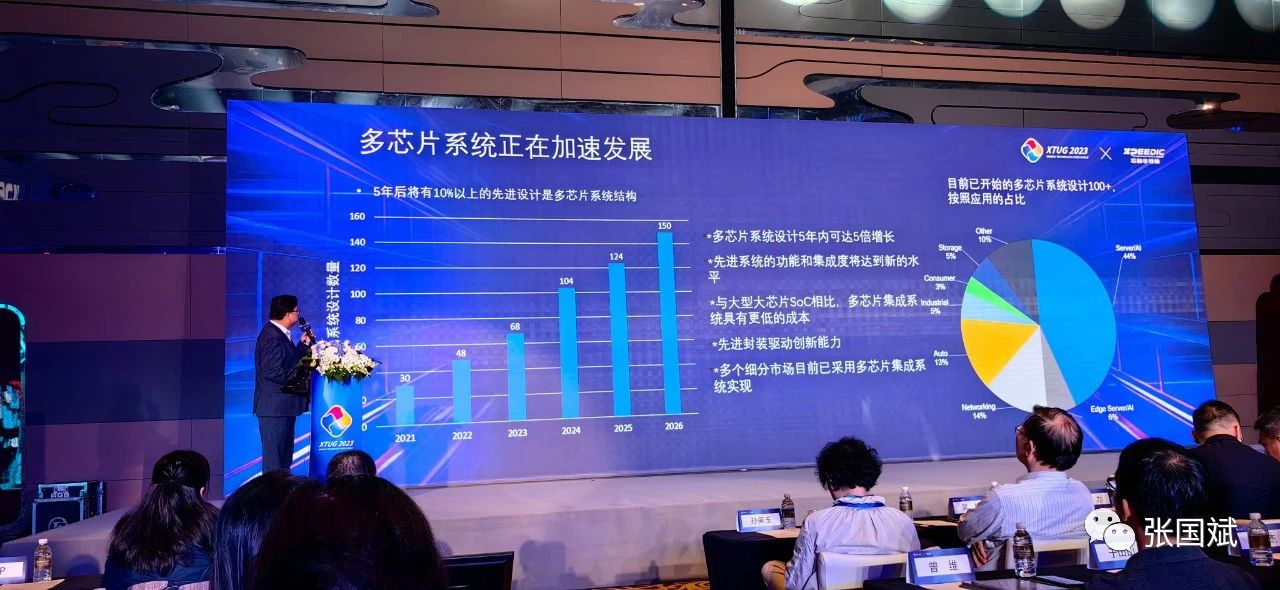

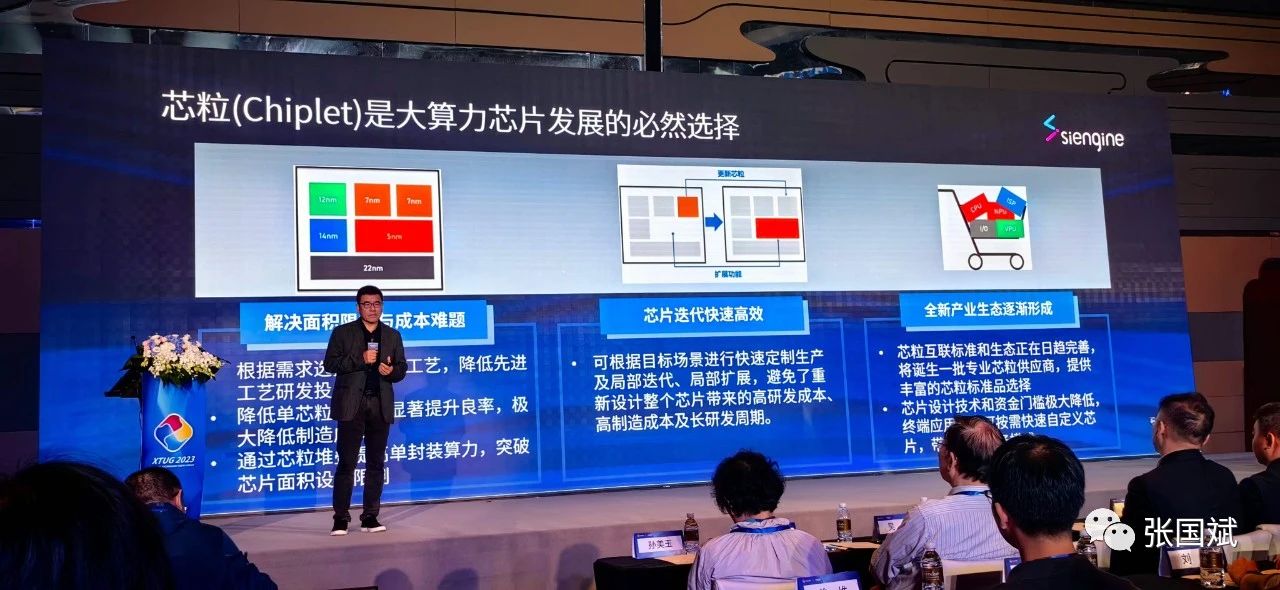

高性能计算和人工智能正在形成推动半导体行业飞速发展的双翼。面对摩尔定律趋近极限的挑战,3DIC Chiplet先进封装异构集成系统越来越成为产业界瞩目的焦点。这种创新的系统不仅在Chiplet的设计、封装、制造、应用等方面带来了许多突破,同时也催生了全新的Chiplet EDA平台,共同为创造下一代数字智能系统赋能。

10月25日,2023芯和半导体用户大会在上海召开,超过600人涌进会场,站无虚席,聆听嘉宾精彩分享。

本次大会以“极速智能,创见未来”为主题,以“系统设计分析”为主线,以“芯和Chiplet EDA设计分析全流程EDA平台”为旗舰,以“EDA²,上海市集成电路行业协会和上海集成电路技术与产业促进中心”为指导单位,包含主旨演讲和技术分论坛两部分,主题涵盖芯片半导体与高科技系统领域的众多前沿技术、成功应用与生态合作方面的最新成果。

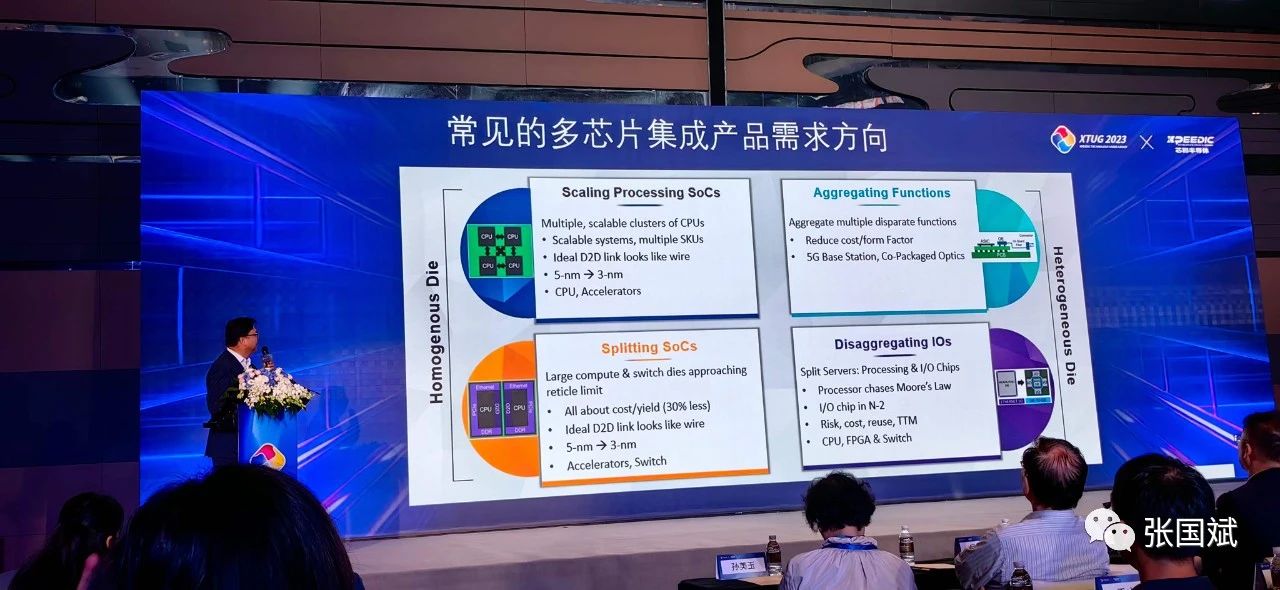

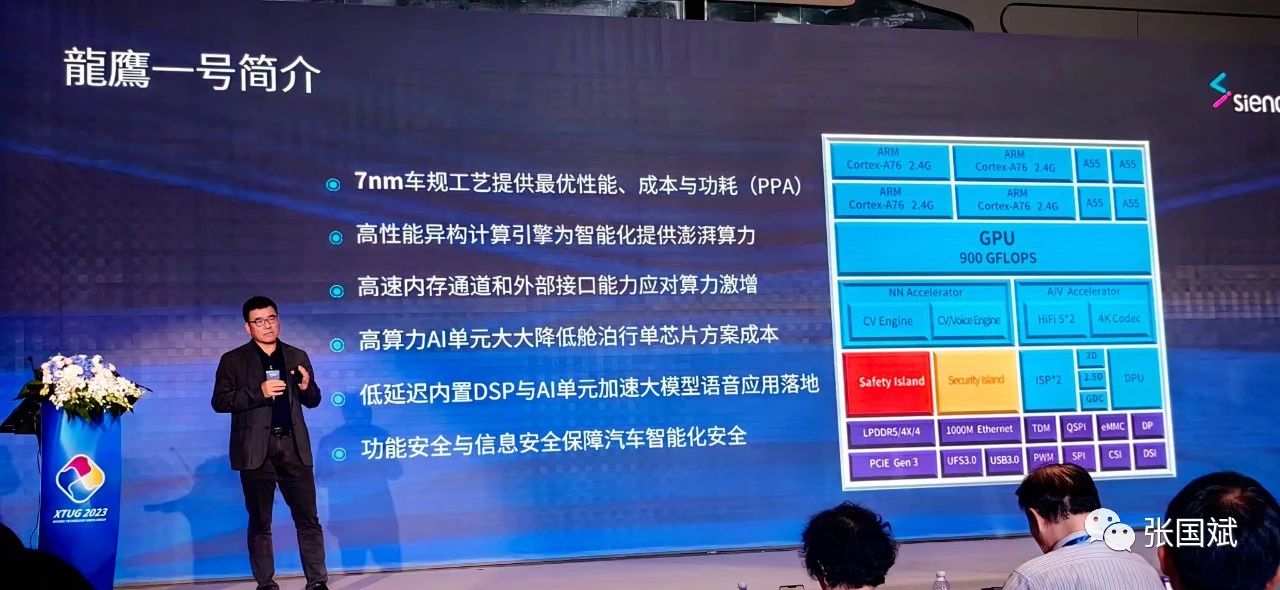

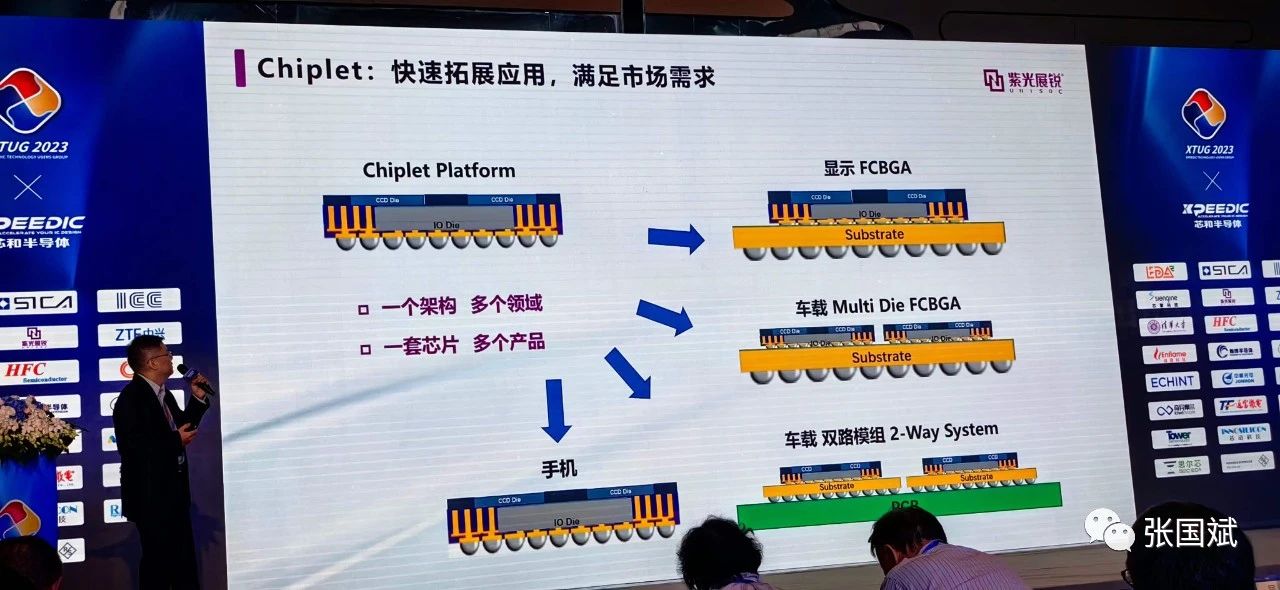

主旨演讲部分,由中国集成电路协会副理事长于燮康作开幕致辞。芯和半导体的几位重量级用户和生态合作伙伴大咖纷纷上台,从汽车电子、5G通讯、数据中心等方面发表演讲,芯擎科技的创始人、董事兼CEO 汪凯博士的演讲主题是《高算力车规芯片推动域控融合新趋势》,紫光展锐封装设计工程部部长姚力的演讲主题是《设计仿真合作共赢》,中兴微高速互连总工程师吴枫的演讲主题是《算力时代的Chiplet技术和生态发展展望》,清华大学集成电路学院副院长尹首一教授的演讲主题是《大算力芯片发展路径探索》。

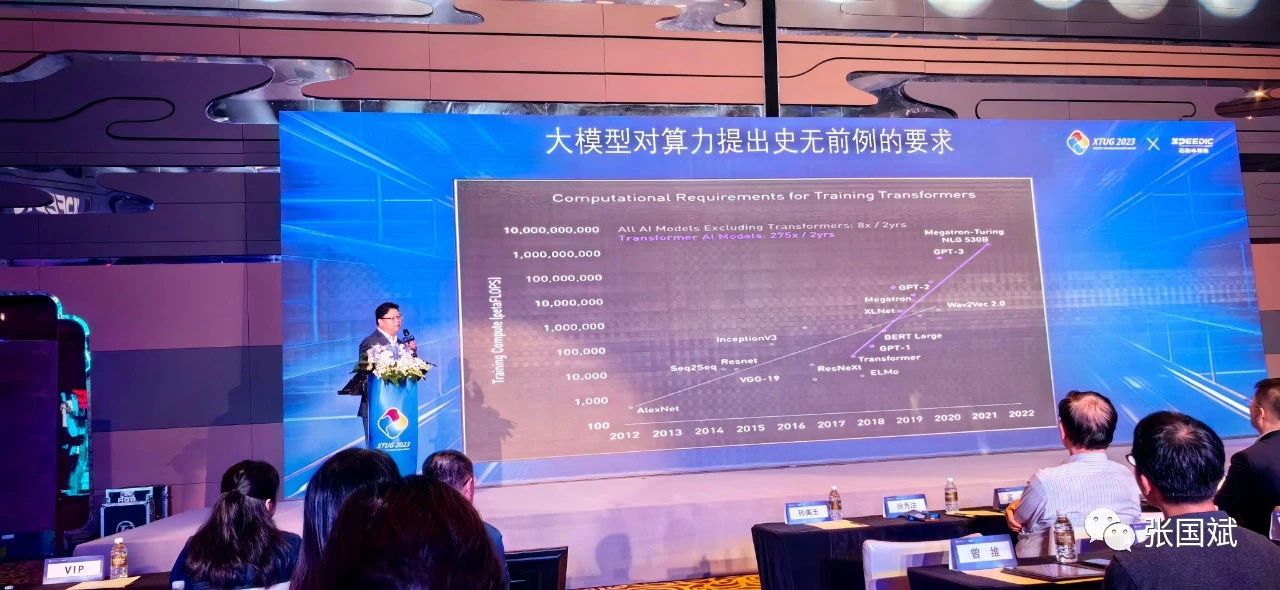

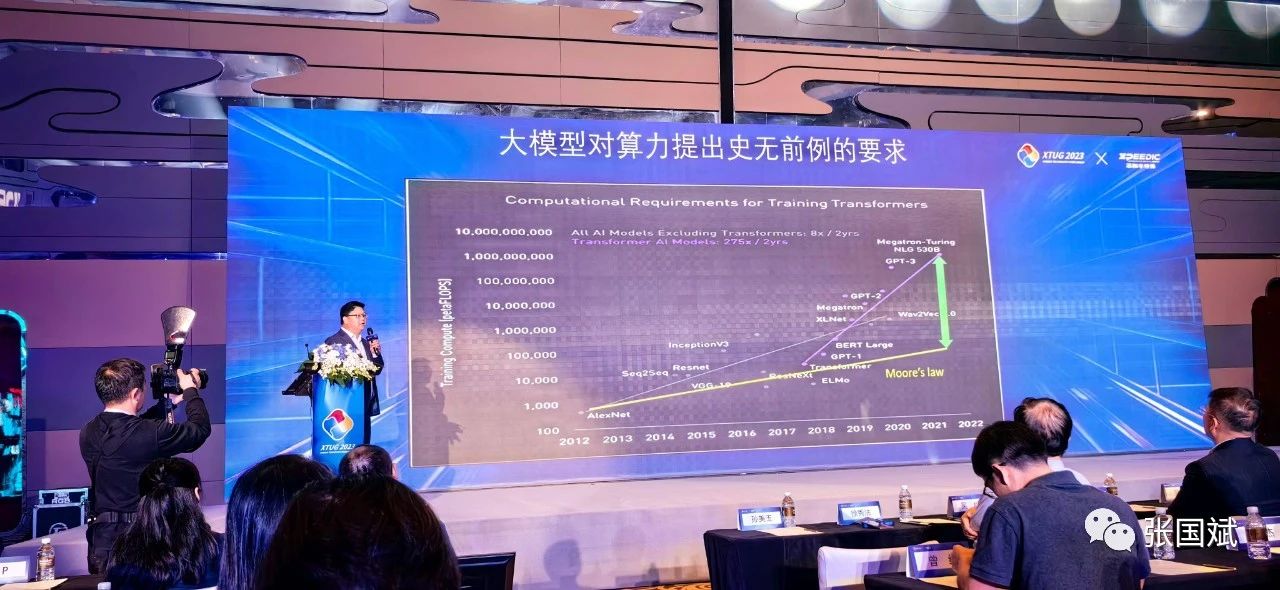

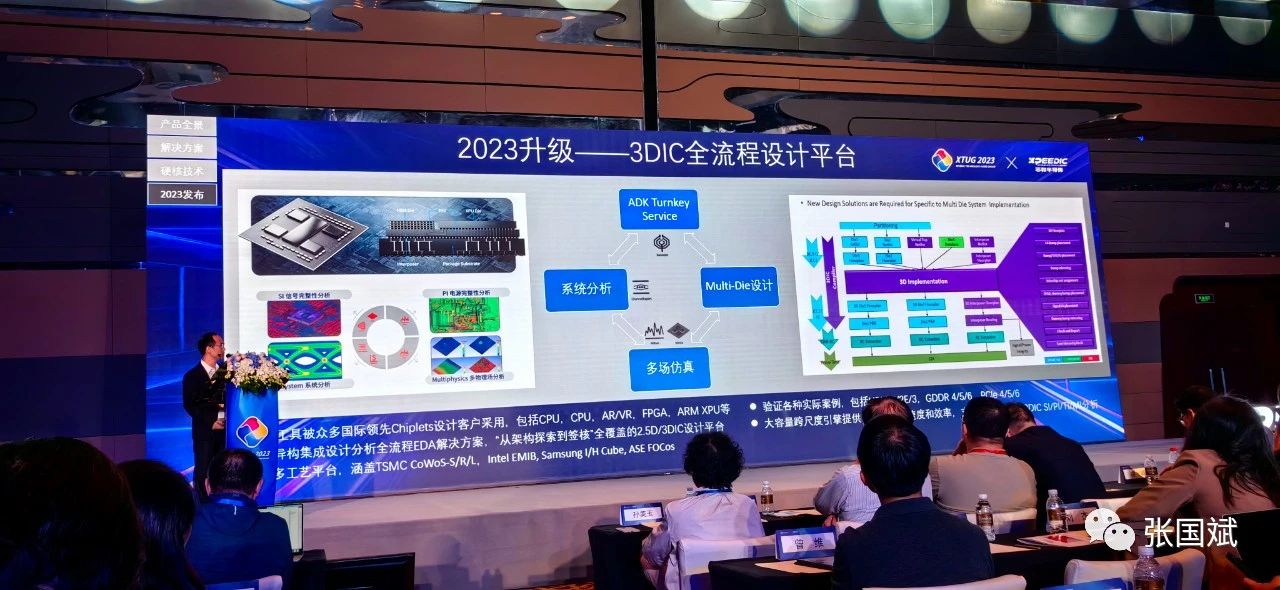

“数据爆炸增长激发了对算力的持续需求,随着摩尔定律放缓,处理器架构正从单芯片系统发展到多芯片系统,目前多芯片系统正在快速发展,chiplet技术受到追捧,从基于chiplet的芯片案例来看,异构集成成为主流。他认为chiplet的核心要素就是IP、EDA和封装。”芯和半导体创始人、CEO凌峰博士在致辞中表示:“大算力时代正在深刻改变我们半导体产业链的方方面面,带来各种新的创新和应用。芯和的Chiplet EDA设计平台,在过去几年已被多家全球领先的芯片设计公司采用来设计他们下一代面向数据中心、汽车和AR/VR市场的高性能计算芯片。我们将继续与用户和生态圈合作伙伴紧密合作,解决Chiplet和高速高频系统带来的挑战。”

芯擎科技CEO汪凯博士分享了汽车智能座舱芯片以及未来智驾芯片发展趋势。

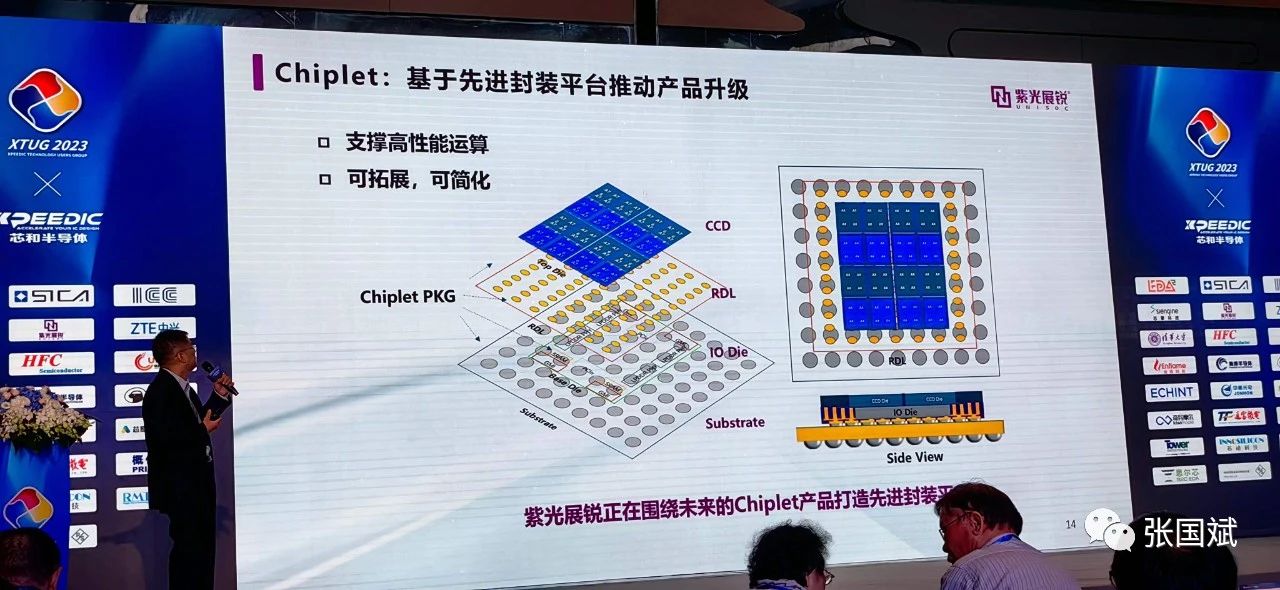

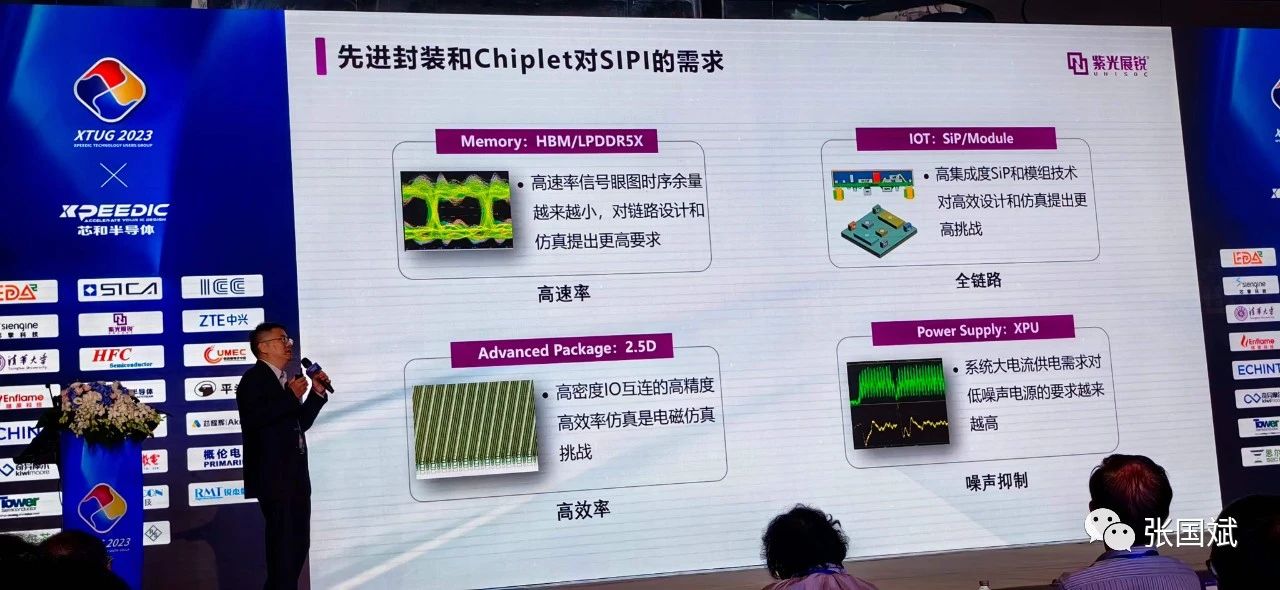

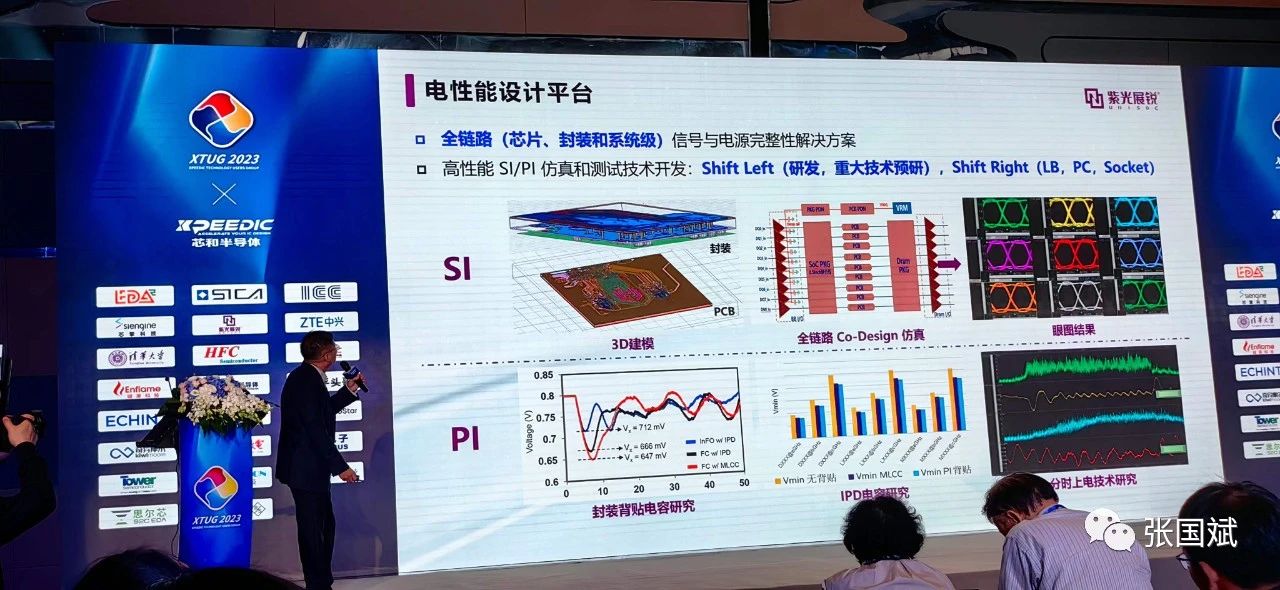

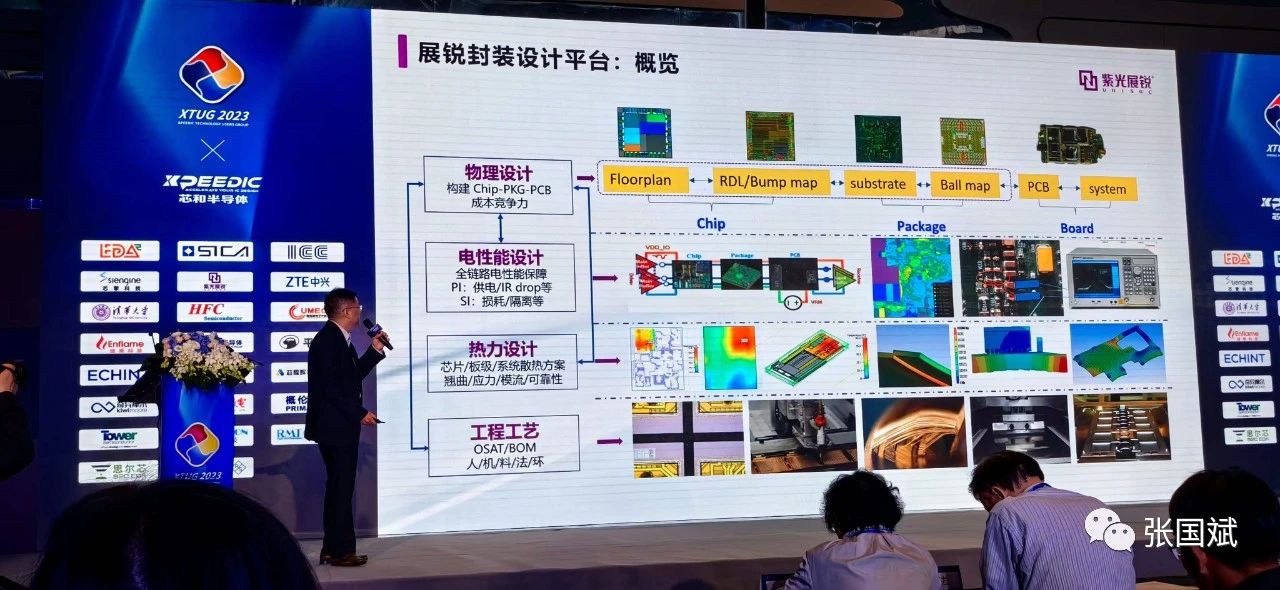

紫光展锐在chiplet技术上的布局以及一些和芯和的合作案例。

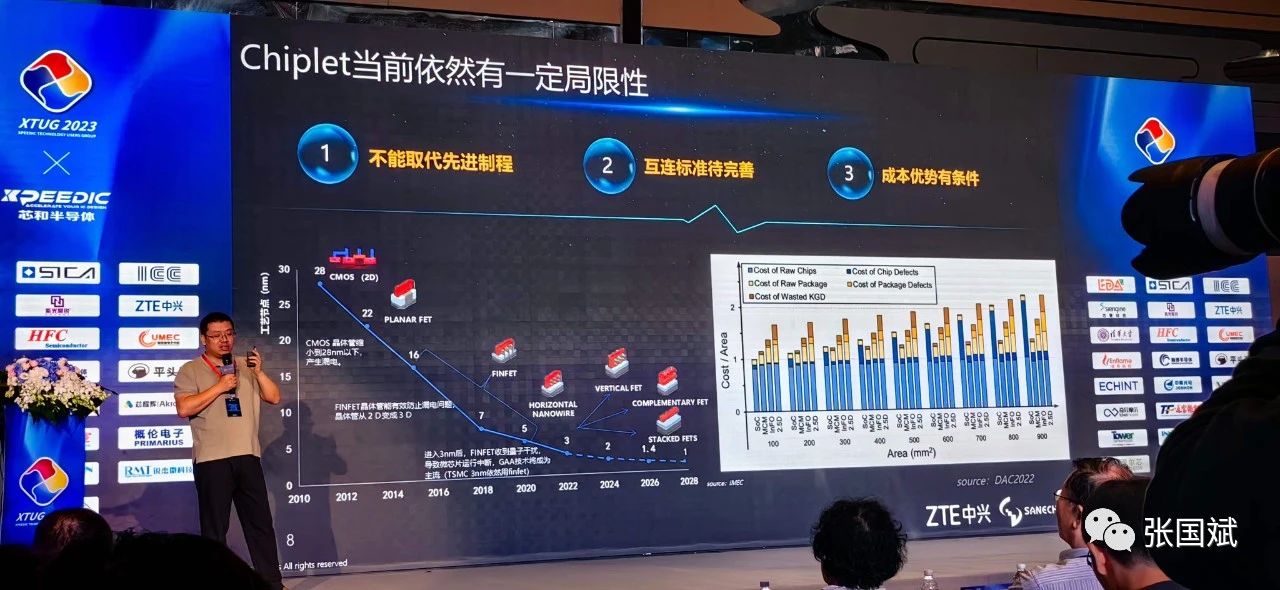

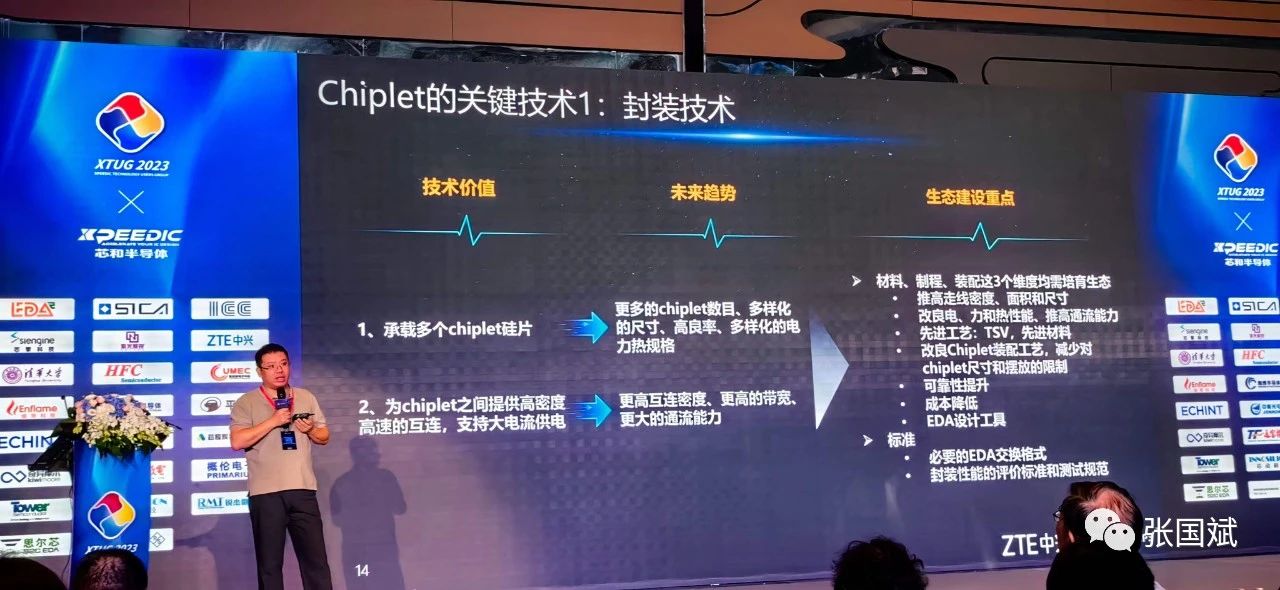

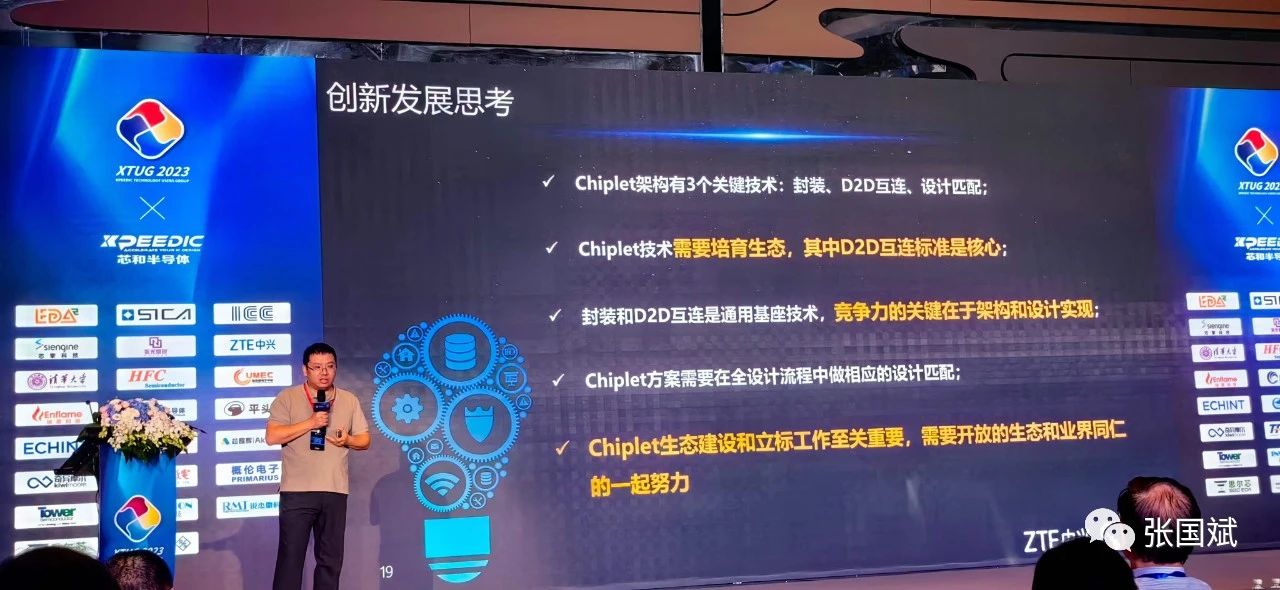

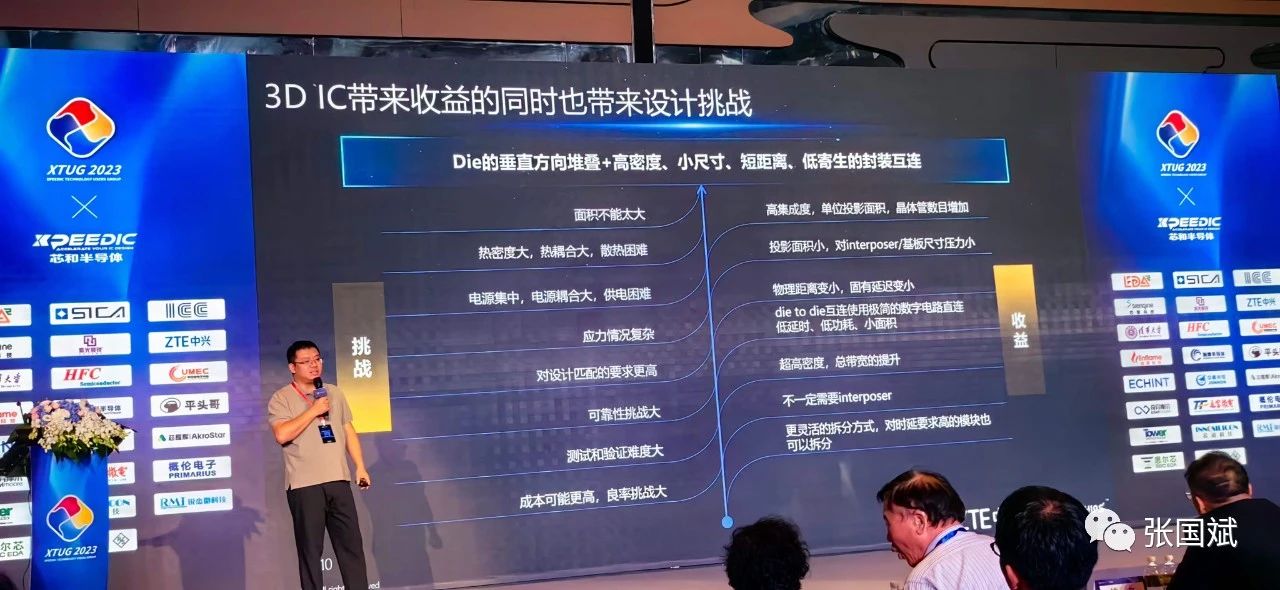

中兴微电子认为chiplet要从产品族来看才能体现出优势,chiplet目前还有三个局限性,一个是能不能取代先进制程,二是互联标准取代完善,三是成本优势有条件--不能只看硅成本要从系统角度看,从未来趋势看3D IC是趋势,2D会有一些信号存在延迟。chiplet需要生态助力,他认为chiplet三大关键技术是:一是封装设技术,二是die to die高速接口,三是系统级协同设计。它是基座技术,最终产品竞争力要靠设计,差异化是系统级协同设计。chiplet的生态和标准需要开放的生态和业界各方协作。

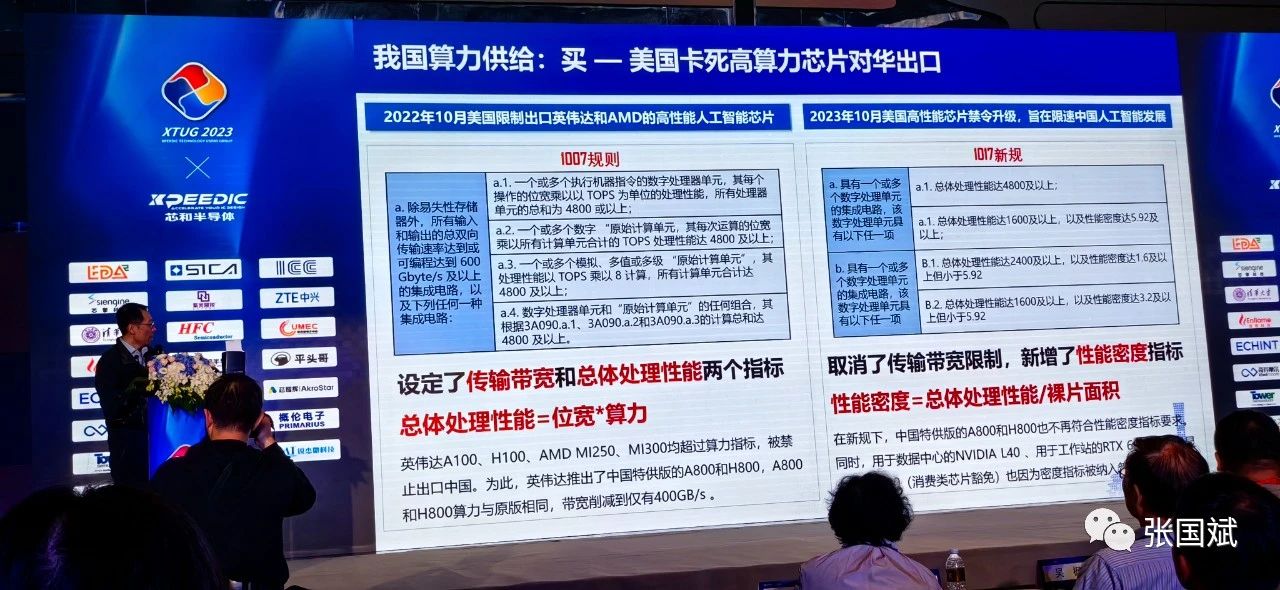

清华大学集成电路学院副院长尹首一教授的演讲主题是《大算力芯片发展路径探索》,他在演讲中分析了美国政府最新对中国人工智能出口限制规则,指出本次限制提出了性能密度的概念,基本堵死了购买渠道。

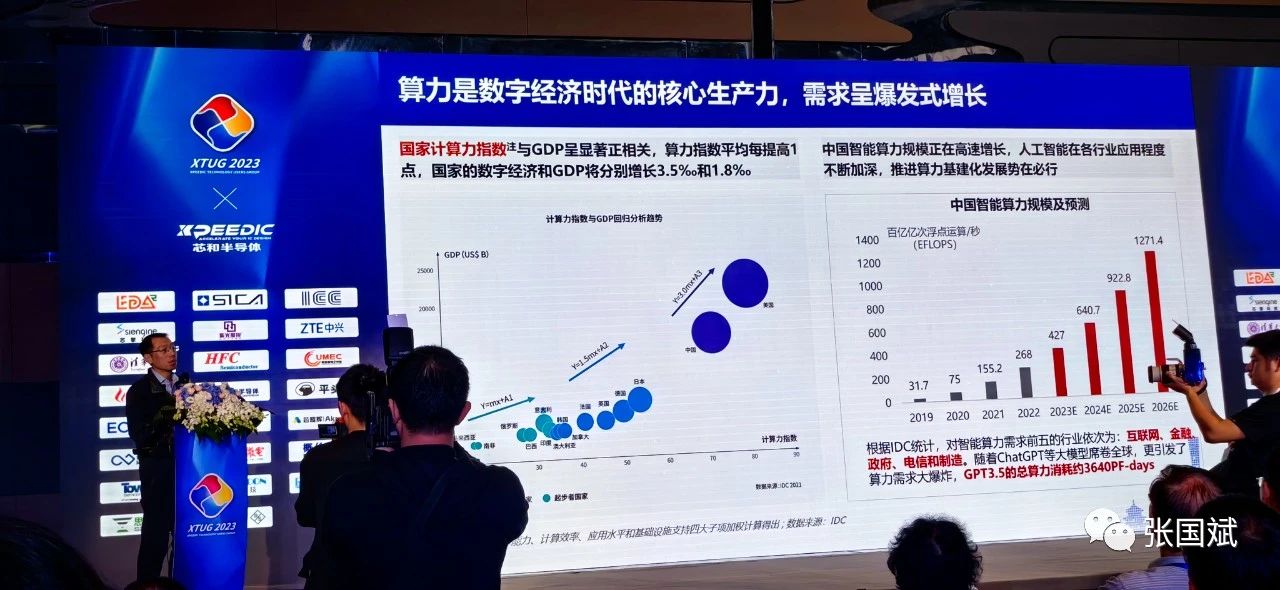

他指出算力是数字经济的核心竞争力,呈现爆炸性增长,而国家计算力指数和GDP是正相关的,计算力指数每提高一点,国家的数字经济和GDP分别提升3.5%和1.8%!

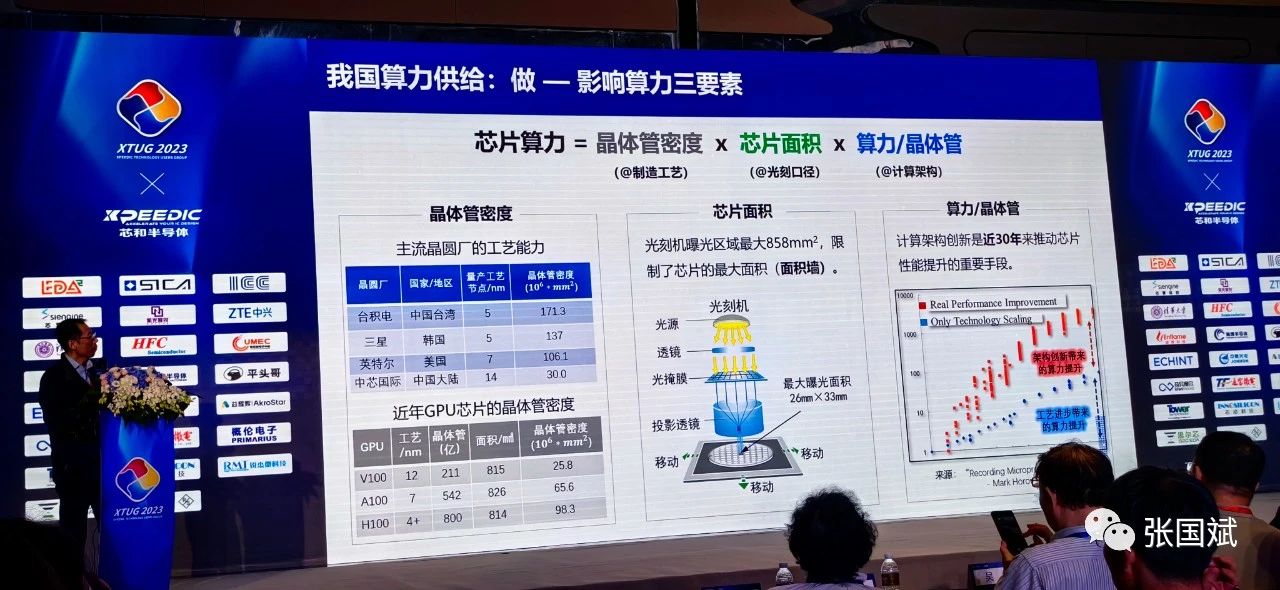

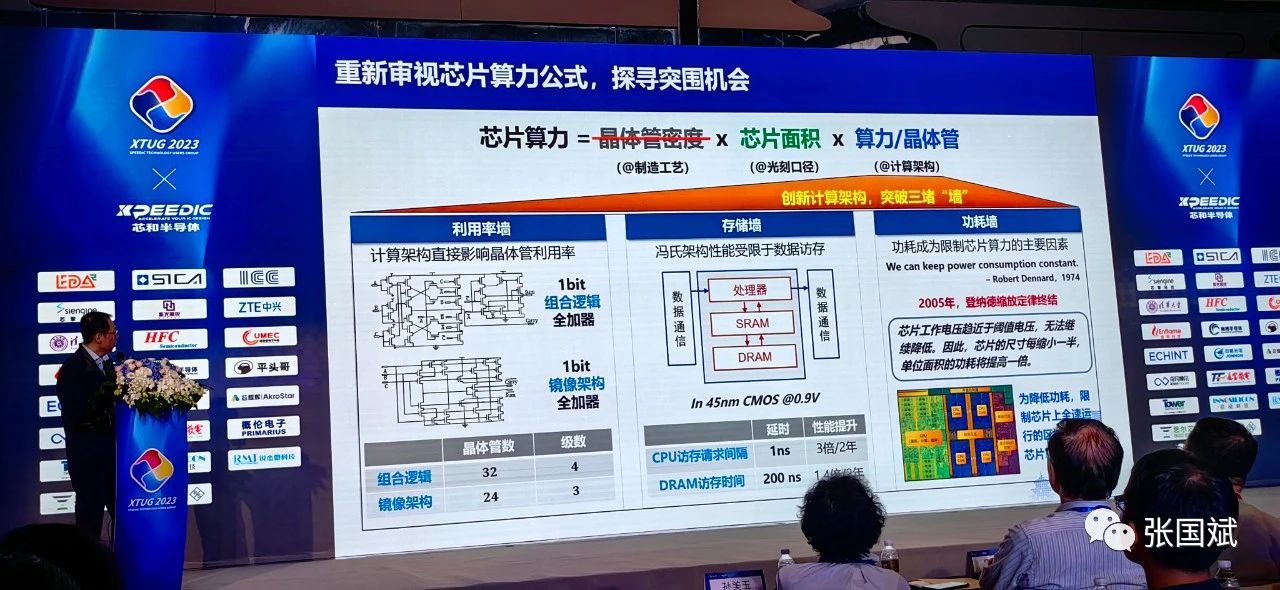

他指出要提升芯片算力,要通过这三个途径来实现,分别是晶体管密度、芯片面积和算力/晶体管(计算架构)。

他指出由于美国对中国人工智能芯片的工艺封锁,所以晶体管密度这条路也被堵死。

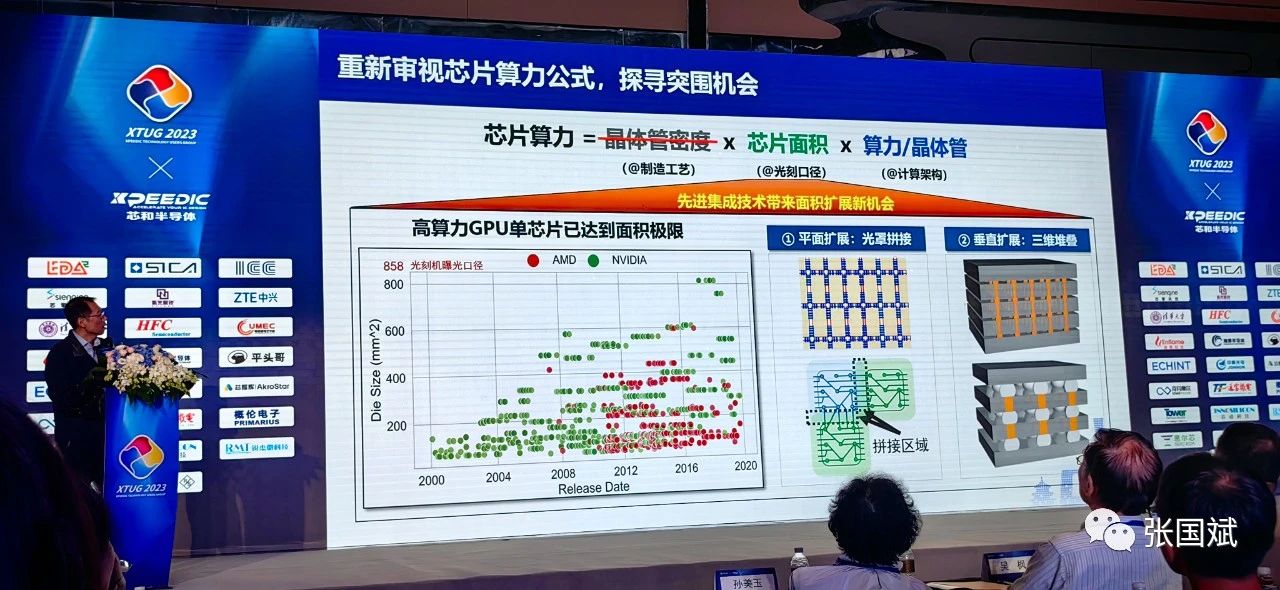

而高算力GPU单芯片已达到面积极限所以芯片面积这条路也基本走不通。

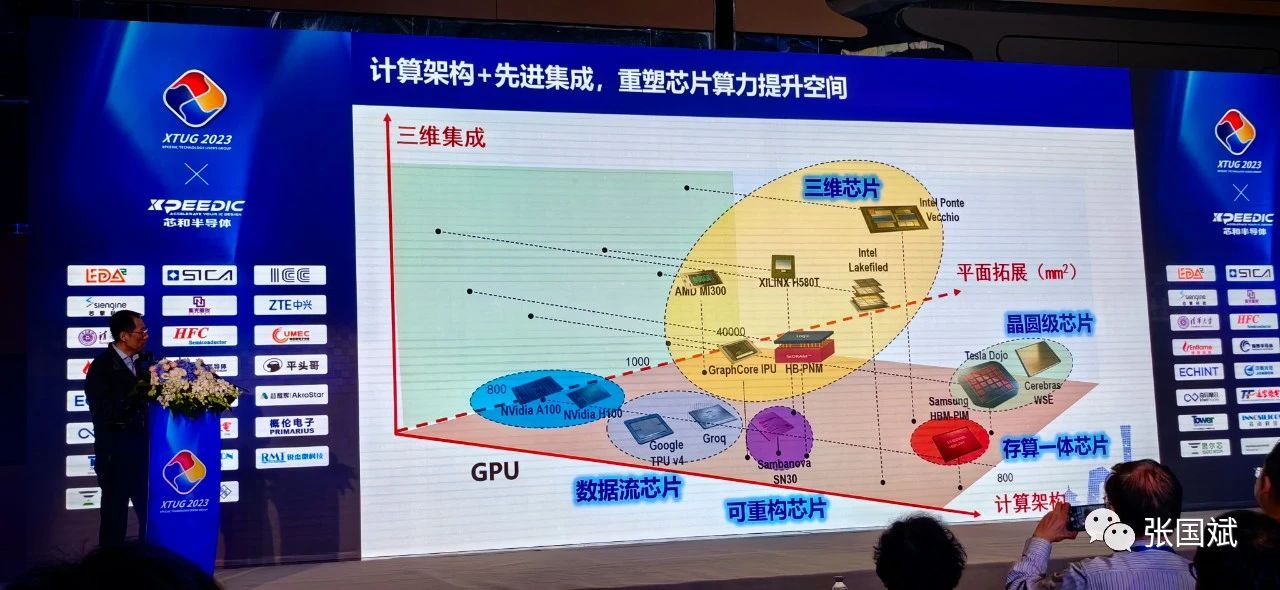

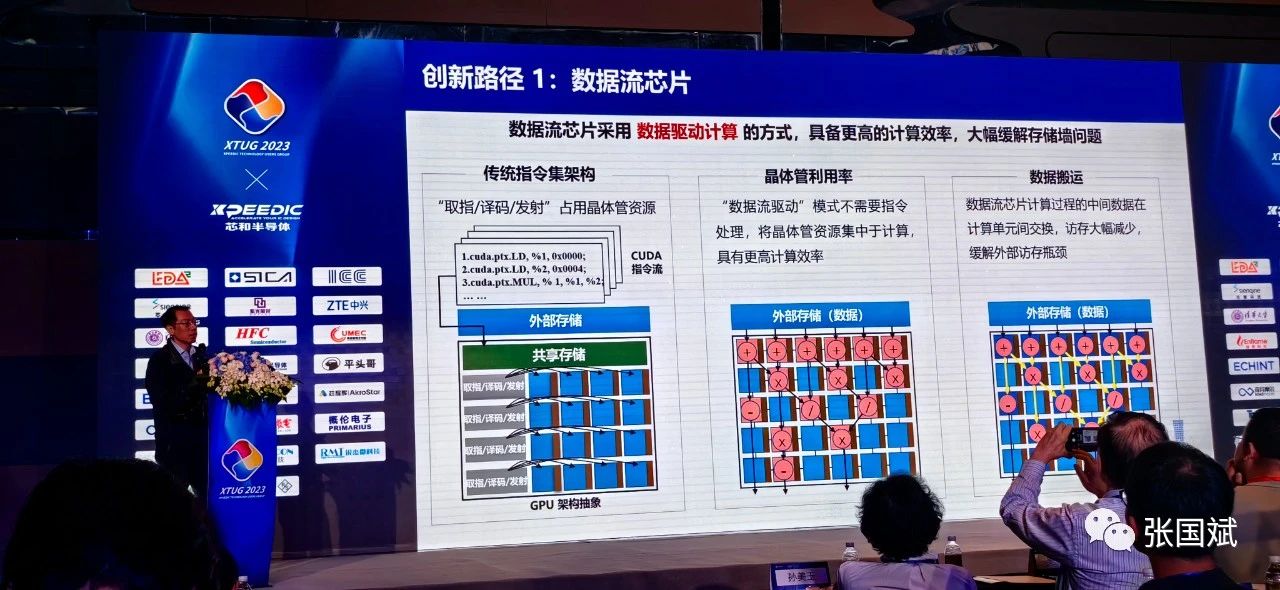

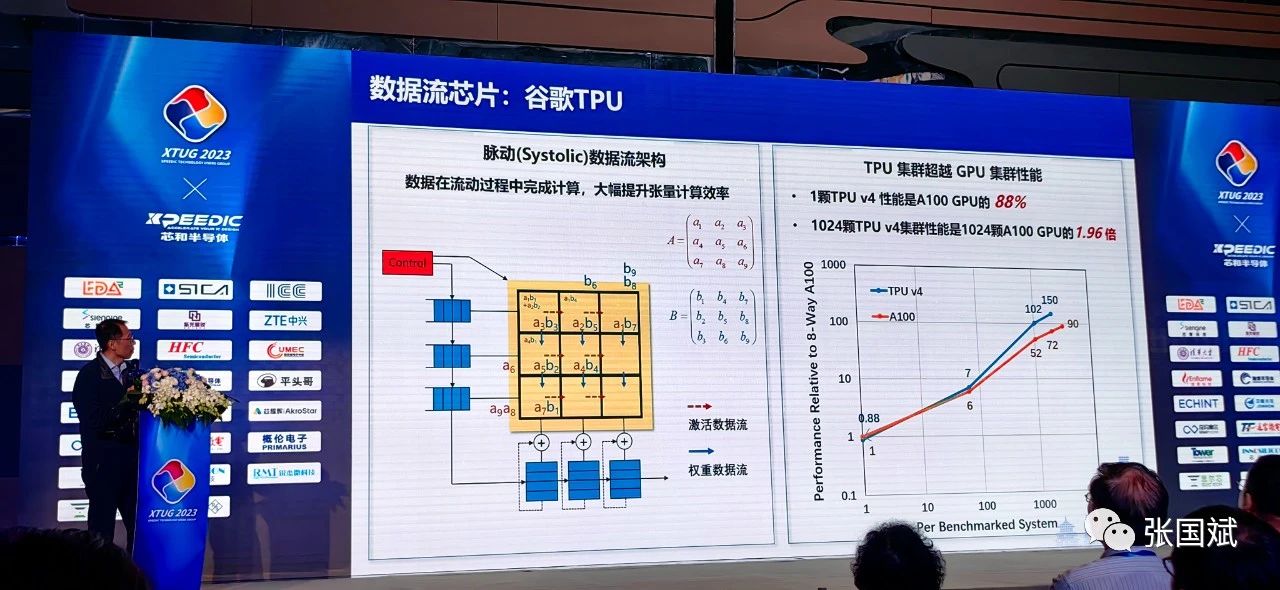

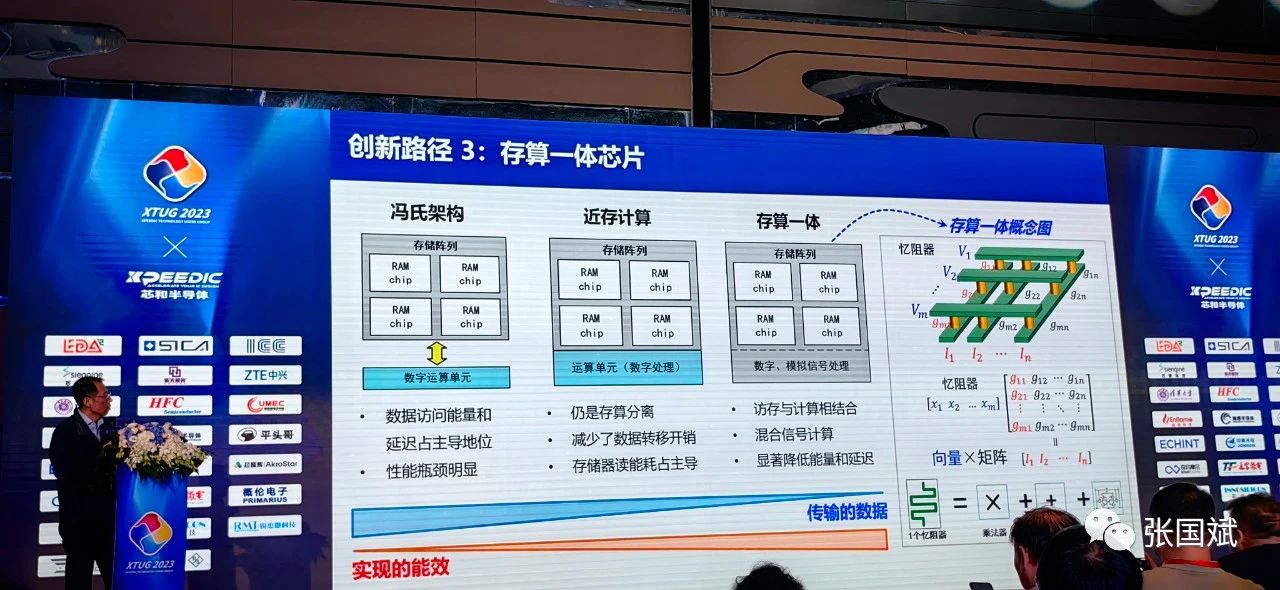

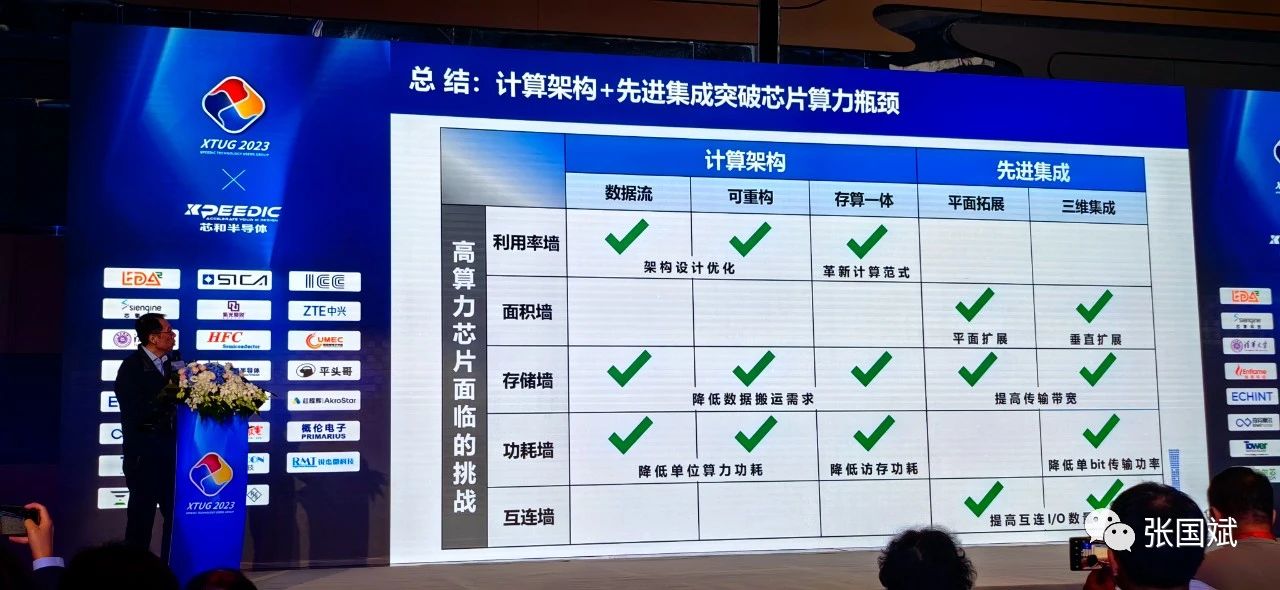

剩下的就是走芯片架构创新这条路,他举出了几个创新的思路,例如三维集成、数据流芯片、晶圆级芯片、存算一体芯片等等。

最后他指出架构创新+先进集成可以突破芯片算力瓶颈!

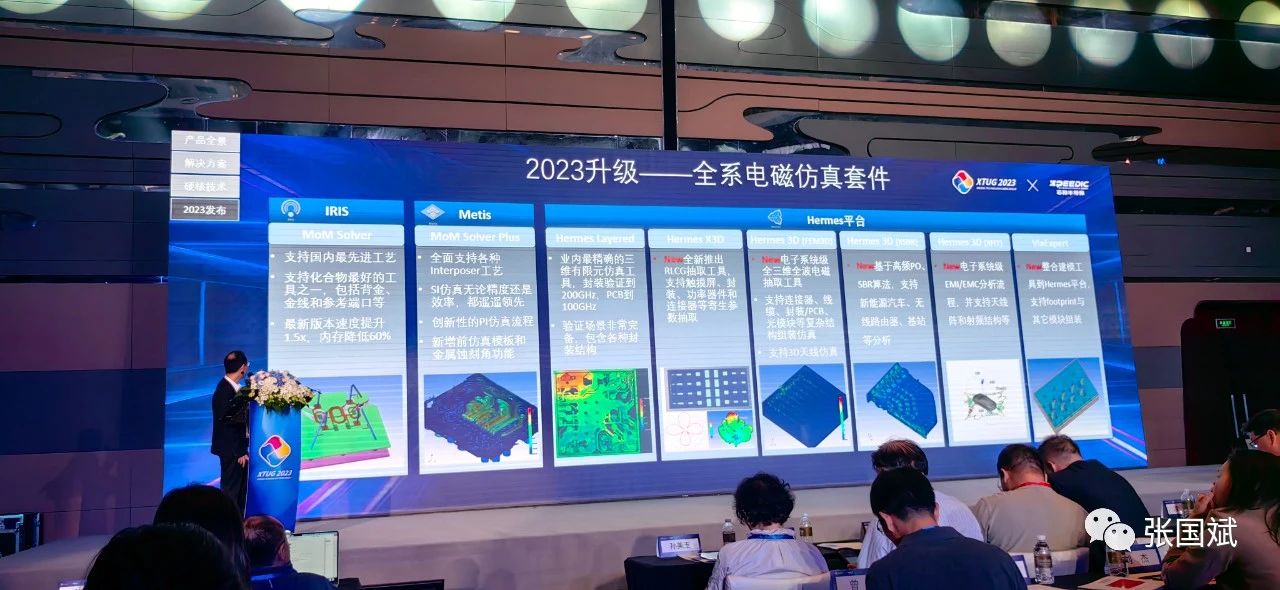

在大会主旨演讲的最后,芯和半导体进行了盛大的2023EDA发布。通过研发开拓创新与客户应用支持的内外联动,芯和不断夯实三大硬核科技:差异化的仿真引擎技术、AI智能网格剖分融合技术、HPC高性能分布式计算技术;形成了从芯片、Chiplet、封装到PCB的半导体设计分析全流程EDA平台;发布了20多款EDA工具横跨12大应用解决方案,服务智能终端、通信基站、数据中心、物联网、汽车电子、新能源、工业装备7大终端行业。其中,2023年的两款旗舰产品——3DIC Chiplet 全流程设计平台和封装与PCB一站式设计平台更是屡获殊荣。

本届大会共安排了两个分论坛,其中高速高频分论坛中,芯和半导体携积海半导体、燧原科技、中兴通讯、中航光电等用户专家分享了众多高速数字设计和射频微波设计的最新应用;而在AI-HPC-Chiplet分论坛,来自CUMEC、芯耀辉、奕成科技、瀚博半导体和奇异摩尔的专家演示了Chiplet技术在设计、分析、工艺等在人工智能、高性能计算方面的各种进展和案例。

被称为半导体芯片之母的EDA的成功有赖于生态圈伙伴的鼎立合作,本届大会的芯和EDA生态伙伴展示区中云集了来自EDA、IP、晶圆制造、封装、测试行业的佼佼者,包括概伦电子、思尔芯、芯耀辉、芯动科技、Tower半导体、通富微电、锐杰微和罗德与施瓦茨等,他们与芯和半导体一起,共同展示了最新的产品和应用,助力用户的产品成功。

这是一个展现中国EDA创新实力的舞台,这是一个预见下一代中国数字智能系统的舞台。通过这个专业的技术交流平台,设计师与来自芯片设计、制造、封装等企业的专家和工程师分享设计理念和成功经验,畅享行业智慧,拥抱国内集成电路发展的新机遇。

关于芯和半导体

芯和半导体是一家从事电子设计自动化(EDA)软件工具研发的高新技术企业,以仿真驱动设计,提供覆盖IC、封装到系统的具备完全自主知识产权的全产业链 EDA 解决方案,支持先进工艺与先进封装,致力于赋能和加速新一代高速高频智能电子产品的设计,已在5G、智能手机、物联网、人工智能和数据中心等领域得到广泛应用。

芯和半导体创建于2010年,运营及研发总部位于上海张江,在苏州、武汉、西安设有研发分中心,在美国硅谷、北京、深圳、成都、西安设有销售和技术支持部门。如欲了解更多详情,敬请访问www.xpeedic.com。