2.1 冯式结构与哈佛结构

2.1.1 两者的区别

如果是独立的存储架构和信号通道那就是哈佛结构,否则就是冯式结构

结构与是否统一编址没有关系,也与 CPU 没有关系,与计算机的整体设计有关

CACHE 的引入(CPU 内部哈佛结构)

总结:高性能单片机的为冯式结构,单片机为哈佛结构

| 8086 | 冯式结构 |

相同存储(RAM) 相同的通道 |

统一编址 |

| STM32F103 | 哈佛结构 |

不同的存储(ROM/RAM) 不同的通道 |

统一编址 |

| 8051 | 改进型的哈佛结构 |

不同的存储(ROM/RAM) 相同的通道 |

独立编址 |

| ARM9 | 改进型的冯式结构 |

相同的存储(RAM/ROM) 不同的通道 |

统一编址 |

2.1.2 总线与 IO 访问

ARM 总线结构(AHB, APB, AXI)与内部外设进行通讯方式:

区别于单片机中的 GPIO 通信访问,GPIO 本身是一个内部外设

IO 接口中能被 CPU 访问的寄存器称为端口/寄存器

端口与存储器统一编址(ARM) uart gpio

端口与存储器独立编址(X86) 8259A 8255(并口) 8253(定时器)

通过 MEMR/MEMW 和 IOR/IOW 两组控制信号来实现对 I/O 端口和存储器的不同寻址

(系统总线)访问与IO访问(独立与统一)

IO 就是指 CPU 的各种内部与外部外设

IO 接口的编址方式:

2.2 ARM处理器状态和处理器模式

注意: 在不同的体系下一些概念有所不同, 在这里我们使用 S3C2440 手册进行参考

2.2.1 处理器状态

从程序员的角度看,ARM920T 处于以下两种状态之一:

ARM 状态:执行 32 位以字对齐的 ARM 指令。

Thumb 状态:执行 16 位以半字对齐的 Thumb 指令。在此状态下,程序计数器(PC)使用位 1 来切换半字。代码密度好

两种状态的切换并不影响处理器模式或寄存器内容。

进入 Thumb 状态

执行一个 BX 指令可以实现进入到 Thumb 状态,操作数寄存器设置状态位(位[0])

如果处理器在 Thumb 状态进入发生异常(如 IRQ、FIQ、UNDEF、ABORT、SWI 等),异常处理返回时也将自动切换回 Thumb 状态。(异常都是在 ARM 状态中执行)

进入 ARM 状态ARM 状态的进入可以通过下列方法:

执行 BX 指令,并且操作数寄存器清除状态位。

处理器发生异常(如 IRQ, FIQ, RESET, UNDEF, ABORT, SWI 等)。此情况下,将程序计数器的内容复制到异常模式的链接寄存器中,并且异常处理将从异常向量地址开始

2.2.2 处理器模式

ARM920T 支持 7 种运行模式:

用户(usr):正常 ARM 程序执行状态快中断(fiq):为支持数据传输或通道处理设计

中断(irq):用于一般用途的中断处理

管理(svc):操作系统保护模式

中止(abt): 数据或指令预取中止后进入

系统(sys):操作系统的特权用户模式

未定义(und):执行了一个未定义指令时进入

模式的改变可由软件控制,或者由外部中断或进入异常引起。大部分应用程序都将在用户模式执行。 被称为特权模式的非用户模式,都将进入到中断服务或异常中去,或者访问受保护的资源。

设计的目的: 提高响应速度, 注意: 保护模式/特权模式, 需要 MMU 和代码支持

2.2.3 ARM 流水线设计

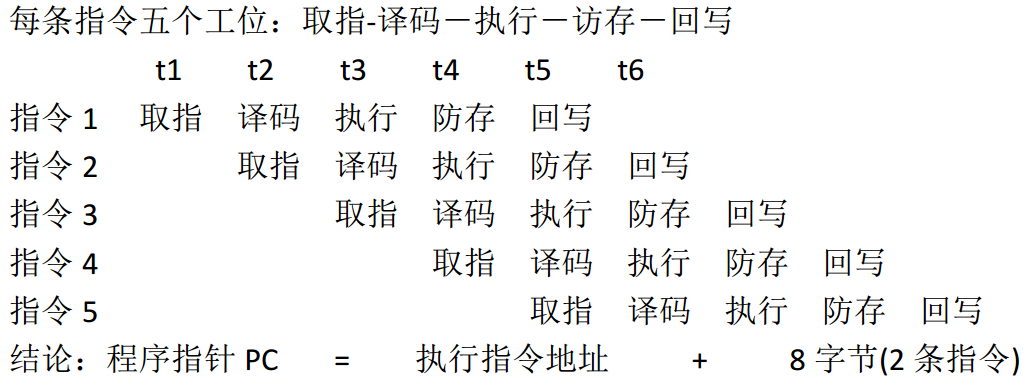

ARM9 为 5 级流水线