项目背景: 项目为一个云端运算的产品,所有的高速和低速信号都要进行信号完整性测试,其中包括高速串行信号PCI-Express Gen1( 简称PCIe Gen1)。PCIe Gen1信号分为CEM和base两种情况,CEM的测试可以使用 PCI-sig协会的fixture直接进行测试;base的测试直接使用探头探测最终端的测试点,这样就会带来一个问题,如何才能测试到芯片的的最终端?因为,信号的互连通道不仅仅包含了PCB走线,还包含了芯片内部的布线,一般我们认为测量到芯片内部的Die才算最终端。

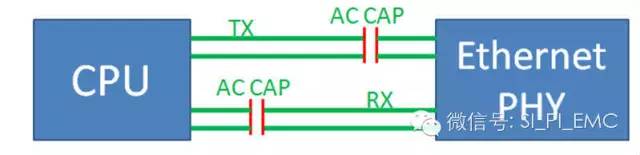

该项目的PCIE 1.0是属于PCIe base的,互连CPU与以太网PHY,如下图1所示:

图1 原理框图

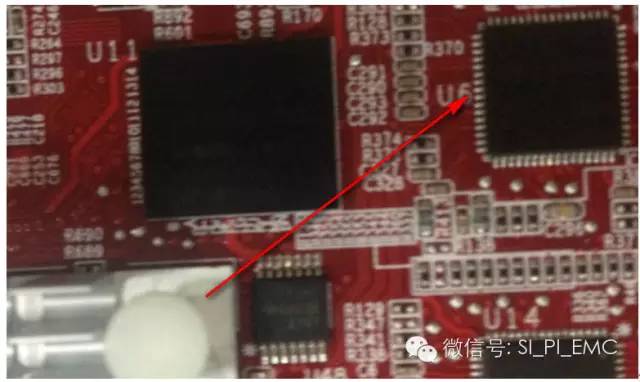

所以测试的时候,需要将probe探测到最终端,但是对于目前示波器测试而言,都只能测试到芯片的引脚上,没有办法探测到最终端的Die上,如下图2所示。

图2 测试点只能探测到芯片的管脚

测试设备:示波器(16GHz),测试探头(16GHz),万用表,烙铁,校准板,网络分析仪(带TDR选件)

分析软件:Intel Sigtest

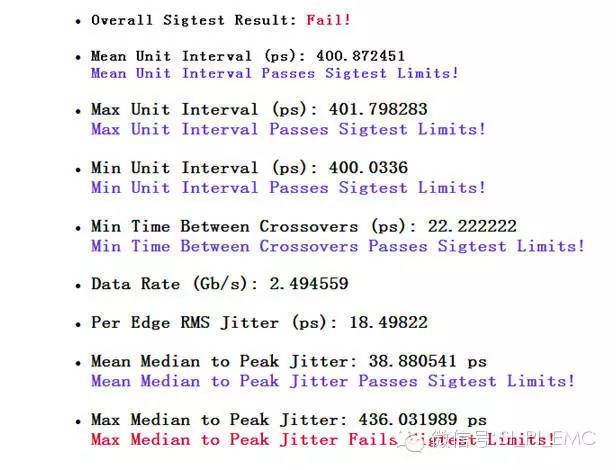

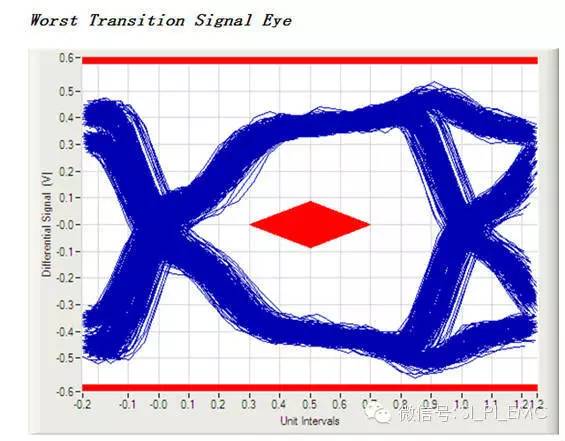

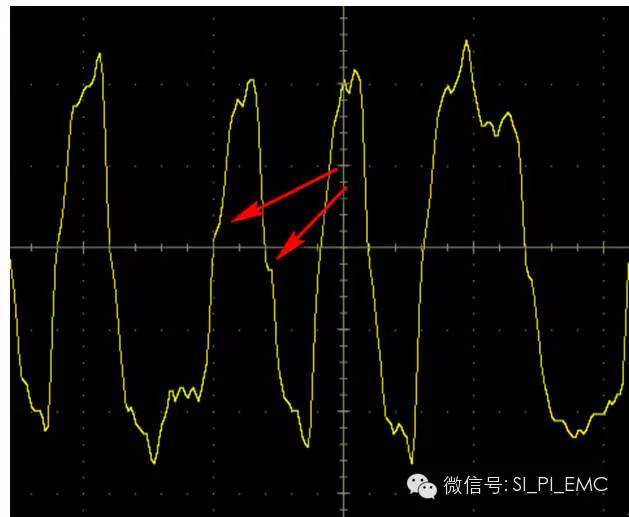

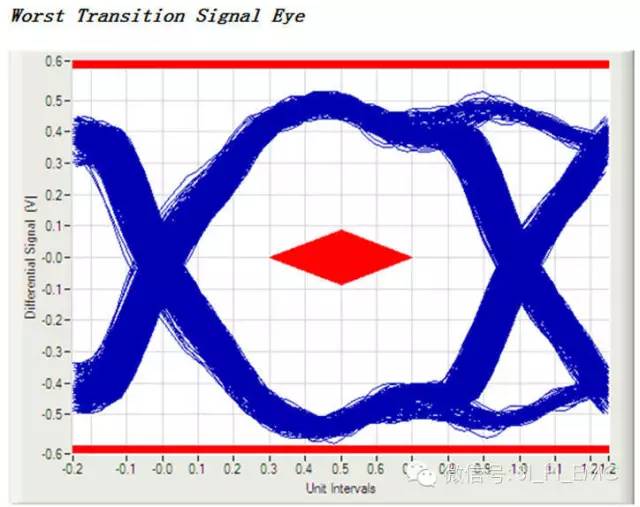

问题描述以及分析:在测试接收端(RX)的信号时,以太网PHY发送信号,测试点选在CPU BGA下方的过孔上,信号没有任何问题,眼图和jitter都能满足PCI-sig协会规范。测试发送端(TX)时,CPU发送信号,以太网PHY是接收端,由于PHY芯片封装是QFP的,所以探头点在引脚上。得到测试波形后,在分析软件中分析波形,能通过眼图模板测试规范,但是发现jitter过不了规范,重复几次测试都是如此。再校准示波器和测试探头再测试,依然如此。每次得到的结果如下图3所示:

图3 眼图和jitter测试

结果显示fail,而且是jitter fail。 jitter的问题一般都是比较麻烦的。从眼图上看,眼图的轨迹很稀松,也不是很光滑。

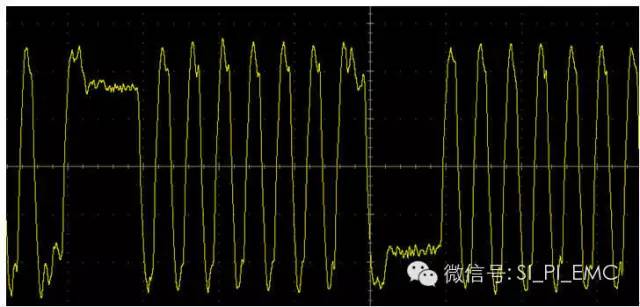

将示波器的原始波形展开放大观察,发现信号在上升和下降沿上出现了非单调的现象,对比眼图,正好能对应上眼图的交叉点处,如下图4所示。

图4 测试波形图

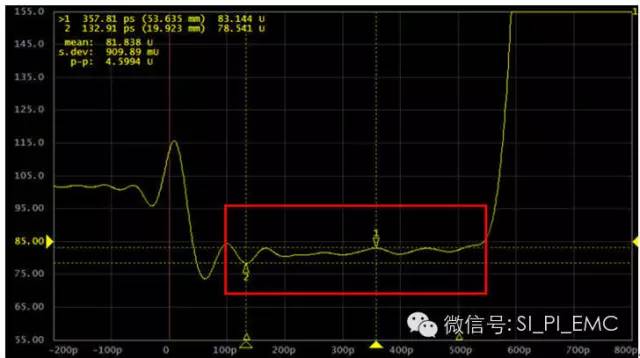

一般非单调是因为阻抗不连续造成的。在PCB生产完成之后,我们对高速信号进行了阻抗的测试,对应的阻抗如下图5所示:

图5 阻抗测试曲线

上图所示,这是使用网络分析仪的TDR软件测试得到的结果,信号线的设计阻抗为85ohm,有上图5红色框曲线所示,测试阻抗都能满足在85ohm +/-10以内的设计要求,可以认为其阻抗一致性比较好。不存在信号线阻抗突变的问题。如果阻抗没有突变,一般在测试时出现这种非单调的情况,大多时候都是由于测试不在最终端所造成的(当然,最终端的die达不到,那么至少要求stub最短)。

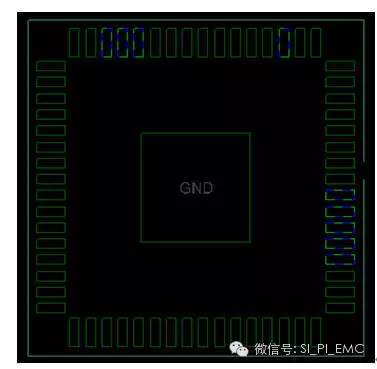

项目使用的以太网 PHY封装如下图6所示:

图6 芯片封装

这种封装,很多时候其芯片内部走线比较长,那么在测试的时候,其探测点在芯片的引脚上,那么内部的走线就是一段stub,显然,这一段stub很长,由于stub的作用,很可能最终导致其测试时信号波形出现非单调。进而影响眼图、jitter等信号完整性的表现。

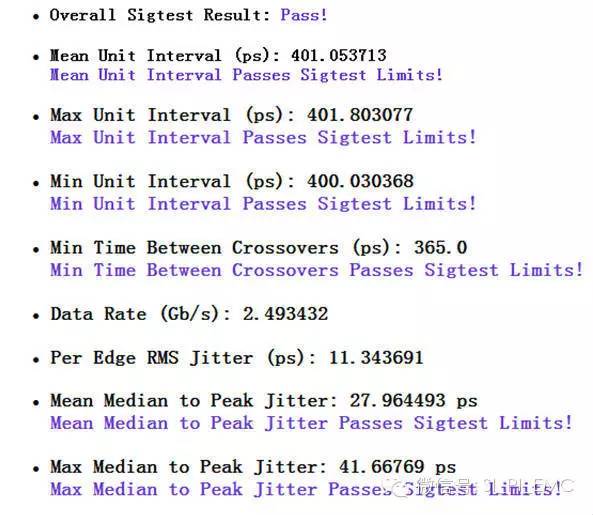

解决方案:分析了相关的原因后,怀疑就是在测试时芯片内部的走线形成了stub,那么在测试把芯片去掉,在PCIE信号两个引脚上分别焊接上50ohm的端接电阻,类似PCIE CEM的测试一样,探头连接在电阻端进行测试,这样就不会存在stub,如果信号波形是好的,都能满足眼图、jitter等性能指标,那么怀疑是芯片内部的走线引起的stub导致的反射,这就是成立的,这样的情况可以认为PCIe的互连通道的信号完整性能满足产品和规范的要求。

芯片去掉之后,端接上电阻,得到眼图和jitter分析结果如下图7所示:

图7 改变后测试眼图和jitter

下图8是端接后展开的波形,在上升和下降沿处都没有观察到非单调性。

图8 改变后测试波形图

综上所述,此处PCIe Gen1测试信号完整性fail的问题是由于测试点不在最终端测试所造成的结果,可以推断此PCIe互连通道的信号完整性没有问题。

如果其它的测试遇到这样的情况也是一样,特别是一些项目的芯片很大,像FPGA那样的,如果需要测试的信号线其能探测的测试点离最终端(Die)比较远,在测试的时候又出现了问题,这个时候就需要考虑是否是由于测试点不在最终端(或最靠近最终端)造成的。