接着上次的TIMER事件触发中断的响应话题继续聊聊。

情况是这样的,现在使用STM32G4系列的TIM8,工作在中心对齐计数,PWM单脉冲模式,使用内部系统时钟做时钟源,计数时不做分频,即PSC=0。CH2做PWM输出。启动时计数器从0开始计数,与RCR对应的计数器值为3。请问在0~ARR范围内调整CCR的值时,整个工作周期内进入基于通道比较事件的中断响应次数可能是下面哪些选项?

A:1 B:2 C:3 D:4 E:0

因为RCR=3和单脉冲模式。意味着从启动开始到计数停止,发生4次溢出后产生更新事件并停止计数,计数器刚好工作2个完整的计数周期。

如果说将通道比较事件的中断请求使能禁用掉或者将NVIC端与该事件有关的中断响应使能禁用掉,自然不会发生针对通道1比较事件的中断响应。从这个角度讲,选择E就很自然了。现在假设针对通道比较事件的中断请求以及NVIC端的中断响应允许都使能了,那还可能有哪些情形呢?有没有可能一次比较中断响应都不发生呢?

其实是可能的。

前面说过,STM32 TIMER采样中心对齐计数模式的话,又分三种计数模式【具体解读见前文《一个基于TIMER事件的中断响应话题》】。如果TIMER采样中心对齐计数模式1,且CCR=0时,是不会发生比较事件的,自然不会有相应的中断响应发生。

有没有可能在当前计数周期内只发生2次中断响应呢?这里有两种情况:

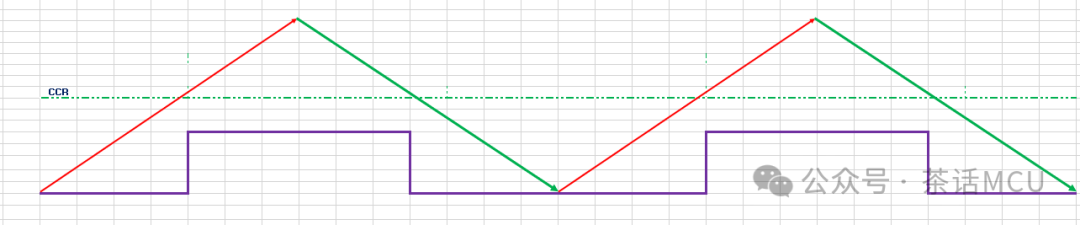

第一种情况,定时器工作在中心对齐计数模式1或模式2,CCR在(0,ARR)之间取值,则在一个周期内只发生1次比较事件,整个计数周期【这里就是2个计数周期】则仅发生2次比较事件,自然可以发生2次中断响应。

第二种情况,定时器工作在任一中心对齐计数模式,CCR取不小于ARR的值,这时每个计数周期仅发生1次比较事件,整个计数周期发生2次比较事件,进而发生两次中断响应。

显然,如果采用中心对齐计数模式3,即在向上计数和向下计数过程中都可以产生比较事件,CCR在(0,ARR)之间取值时,发生4次中断响应就不难理解了。

经过前面的分析,我们知道发生0次、2次、4次中断响应都是可能的。那么,只发生1次或3次中断响应有无可能呢?

这里的条件对ARR和CCR的值并未具体说明,中断响应持续时间也未明确。那么,即使定时器采用中心对齐模式3,中断响应次数一定就是4次吗?未必。

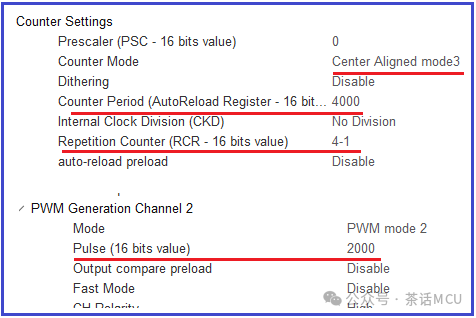

这里使用STM32G474的TIM8来进行验证,定时器计数时钟与主频170MHz一致,不做计数分频。设定RCR=3,CCR=2000,ARR=4000.

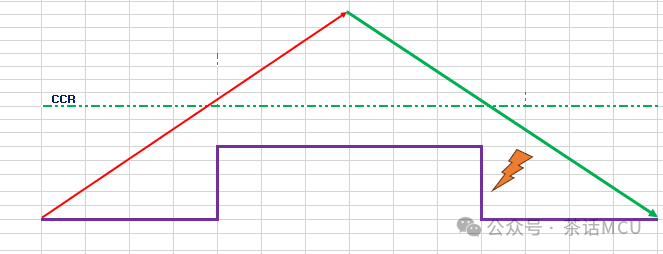

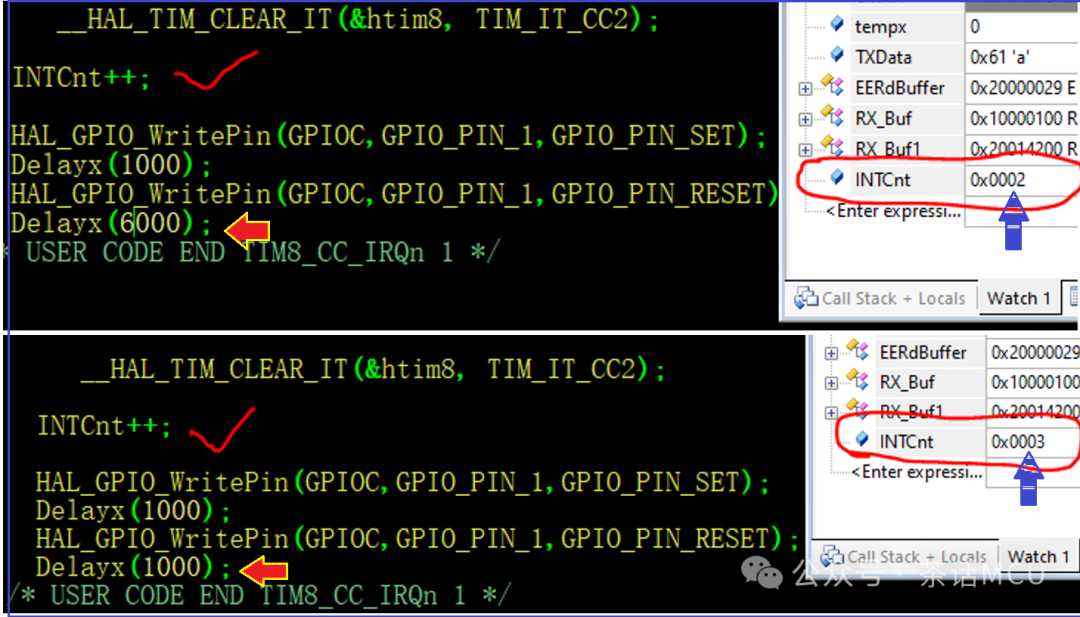

我们可以通过调整中断服务程序持续时间,在上述TIMER时基参数不变的情况下让比较中断只进2次或3次。见下面图示:

有没有可能即使在中心对齐模式3条件,整个计数周期内只发生一次中断响应呢?其实也是可能的。我们可以调整TIMER的时间参数,让比较事件的触发足够近并令中断服务程序也持续一定的时间,即使发生4次比较事件,完全可能最终只进1次比较中断服务程序。见下面测试结果示意图:【ARR=3,CCR=2,中心对齐模式3】

看来,前面提到的5种结果都是可能的。