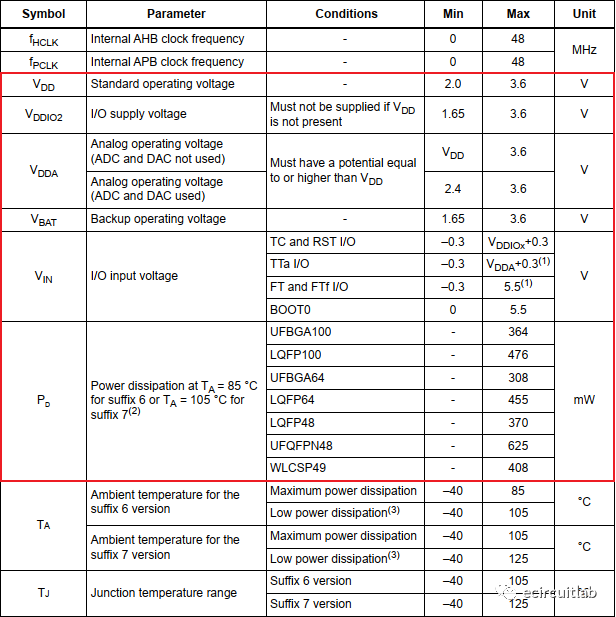

对于任何IC的电源设计要求,都可以在规格书中获取到需要的信息。STM32F0系列MCU电源轨信息和要求可以在规格书第53页的Table 24看到,如下图(图一)所示。

(图一)

如上图(图一)中圈出,STM32F0系列MCU主要有VDD、VDDIO2、VDDA和VBAT四组电源轨,在(图一)中可以看出,VDD和VDDA工作电压范围使用3.3V比较适合。VDDA为模拟电源轨,设计时建议串联一个100Ω/100M的磁珠做高频噪声隔离。

而VDDIO2和VBAT可以根据外围IO电平需求选择常规的1.8V、2.5V、3V、3.3V都可以。如果没有特别需求,可以全部3.3V供电,这样电源系统就比较简单,(图一)的PD项还详细的告诉了我们不同封装的功耗情况,有了这个信息,我们就很好的去评估选择电源方案。

通过上面(图一)提供的信息,我们假设所有电源轨供电都使用3.3V,芯片为LQFP64封装的MCU,通过功耗信息可计算评估芯片在最高负载时,电源系统至少给MCU提供138mA的电流,MCU才能正常工作。

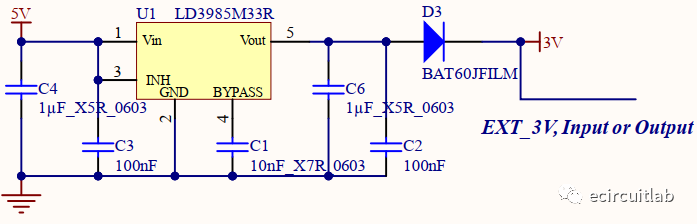

有这个功耗信息我们再评估其他外设芯片的电流后就可以把电源方案选定下来了,对于外设功耗的评估,如果外设没有什么功耗特别高的方案。如果范围在几十mA这样情况下,假定输入电压为5V,那么可以选择一颗最大输出不低于150mA连续输出的LDO即可,因为一般情况下,MCU不会满载运行,也到不了那么高的功耗,但保守起见还是按照评估的要求选择比较好,这里放上ST给一个参考设计如下图(图二)所示,参考设计里多串了个二极管,这个二极管防止外部供电倒灌到LDO上的而已,如果你的设计里不需要使用外部电源供电,直接把它拿掉即可。

(图二)

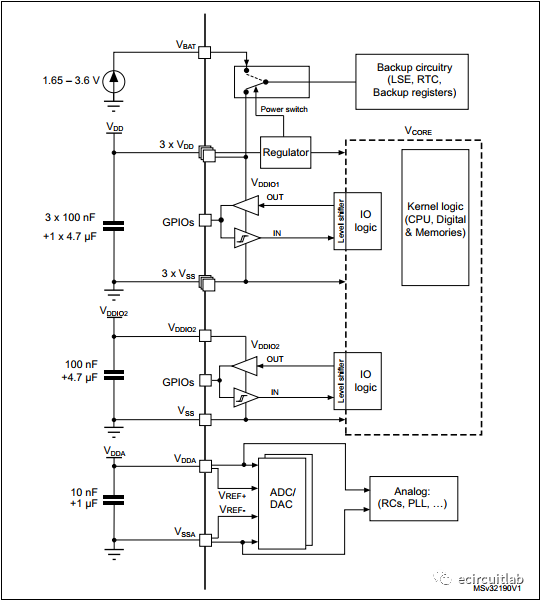

选择好电源方案后,可以参考规格书第49页的Figure 13放置去耦电容,如下(图二)所示,这个去耦方案是ST推荐的,不会有啥问题,如果担心的话可以在VDD、VDDIO2电源轨上多放两颗4.7uF或10uF的陶瓷电容。

(图三)

最后放上ST参考设计的电源部分,原理图如下图(图四)所示,参考设计里使用的芯片型号是STM32F072RBT6,参考规格书的引脚描述,会发现(图四)里的部分引脚信号跟规格书里不一样。原因是ST设计评估板时,考虑了板子能兼容其他系列同封装的芯片的问题,故意改的信号名,不影响实际电路正常工作。

(图四)

技术咨询

技术咨询 代买器件

代买器件 商务客服

商务客服 研发客服

研发客服