一、整体架构

S3C2440的主时钟源可以是外部谐振器(XTIpll),或者外部输入时钟(EXTCLK),经过锁相环MPLL、UPLL产生高频时钟信号,并经由分配传输给AHB总线,APB总线,USB设备,以及内核使用。其中UPLL是USB专用的PLL。以下是时钟体系的总体框架:

二、控制逻辑

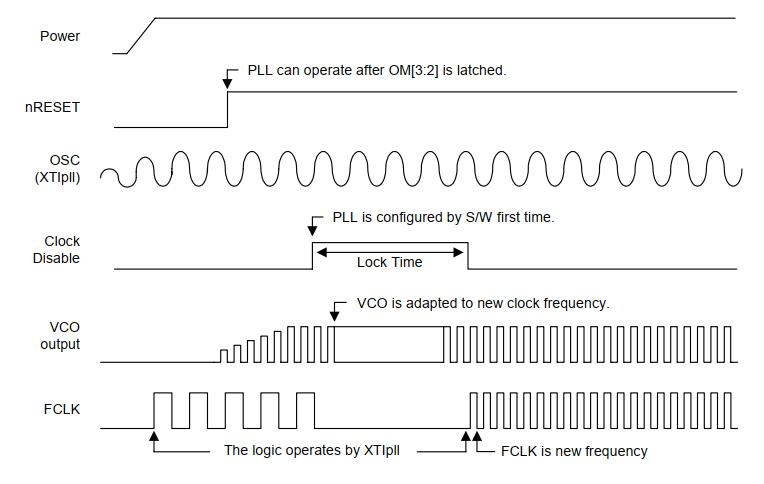

时钟控制逻辑的主要内容为时钟的开启、配置过程。首先是时钟的上电开启时序:

上图来自于芯片手册,是时钟的上电开启过程,经上电与复位,谐振器开始输入信号,此时PLL根据默认配置启动,进入LockTime,由于上电后PLL工作不稳定,其输出信号并不会接入FCLK等,而是接入谐振器输入频率信号,只有在软件配置PLL后才会接入到FCLK等,即使想要使用PLL默认配置,也要用软件重新配置一下。配置PLL即配置PLL CONTROL REGISTER ,配置完成后,PLL会自动进入锁定状态,此时FCLK等保持一段低电平,之后接入修改后的时钟信号。

三、工作模式

围绕着时钟设备,S3C2440的工作模式分为NORMAL mode、SLOW mode、IDLE mode、SLEEP mode,属于Power Management block。

NORMAL mode:该模式下,允许内核和所有外设使用对应的时钟。

SLOW mode:Non-PLL模式,锁相环关闭,芯片工作在外部时钟下,频率取决于外部时钟。

IDLE mode:仅断开内核的工作时钟,外设可正常工作,中断可唤醒。

SLEEP mode:休眠状态,内核和外设均断开时钟,时钟仅连接唤醒逻辑,使用该模式需要两个独立的时钟源,其中一个要保持唤醒程序始终活跃,以便唤醒CPU。

下图为Power Management block在时钟体系中的定位,可以看到,最终的FCLK等输出时钟信号需要Power Management的配合。

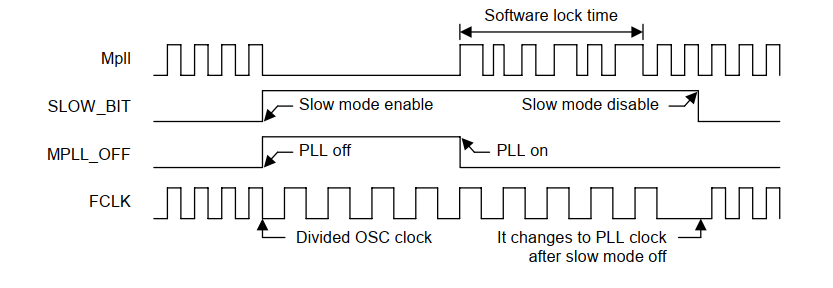

模式切换:以下是芯片手册中对于模式切换的图解:

其中SLEEP mode以及IDLE mode需要通过中断来返回NORMAL mode,着重记录NORMAL与SLOW模式间的切换问题:NORMAL==>SLOW:SLOWmode有专门的寄存器(CLOCK SLOW CONTROL (CLKSLOW) REGISTER)用于开启、配置和关闭,从NORMAL模式转换到SLOW模式时,需要首先配置SLOW_BIT再配置MPLL_OFF关闭MPLL,这时转换为SLOW模式,可以通过配置该寄存器的SLOW_VAL来控制分频,如下图:

其他模式可以参考芯片手册,当然我也是搬运工。

四、配置方法

1、在NORMAL模式下,修改PMS更改PLL配置,当然这会使PLL重新进入LoadTime,在此期间FCLK等持续低电平。

2、在NORMAL模式下,临时开启SLOW模式,并在SLOW期间关闭PLL,这期间FCLK等以SLOW模式下的频率输出,可以更改PLL配置而不至于使内核和外设停止工作。

五、寄存器说明

1、LOCK TIME COUNT REGISTER (LOCKTIME)

PLL的LockTime由该寄存器设置。

2、PLL CONTROL REGISTER (MPLLCON & UPLLCON)

对应上文PMS,可以参照一些经典值来设置PLL输出的频率。

3、CLOCK CONTROL REGISTER (CLKCON)

对应外设、内核的时钟使能等。

4、CLOCK SLOW CONTROL (CLKSLOW) REGISTER

SLOWmode的控制寄存器,可以配置SLOW_VAL,可以使能SLOWbit位,以及开关PLL。

5、CLOCK DIVIDER CONTROL (CLKDIVN) REGISTER

配置分频因子。

6、CAMERA CLOCK DIVIDER (CAMDIVN) REGISTER