近日,复旦大学和清华大学团队在存储芯片上创下新突破。复旦团队研发超快闪存集成工艺,可实现20纳秒超快编程、10年非易失;清华大学团队则提出一种基于磁振子的新型逻辑器件,有望重构逻辑存储器。

复旦团队研发超快闪存集成工艺,突破存储速度极限

非易失性存储器是指即使在存储器芯片的电源被关闭时,也可以保存数据的计算机存储器。常见的非易失性存储器包括闪存(Flash Memory)、只读存储器(ROM),以及一些新技术如磁性随机存储器(MRAM)、铁电随机存储器(FeRAM)、相变存储器(PCM)等。其中闪存是目前占主导地位的非易失性存储器技术,但在速度方面受到限制。

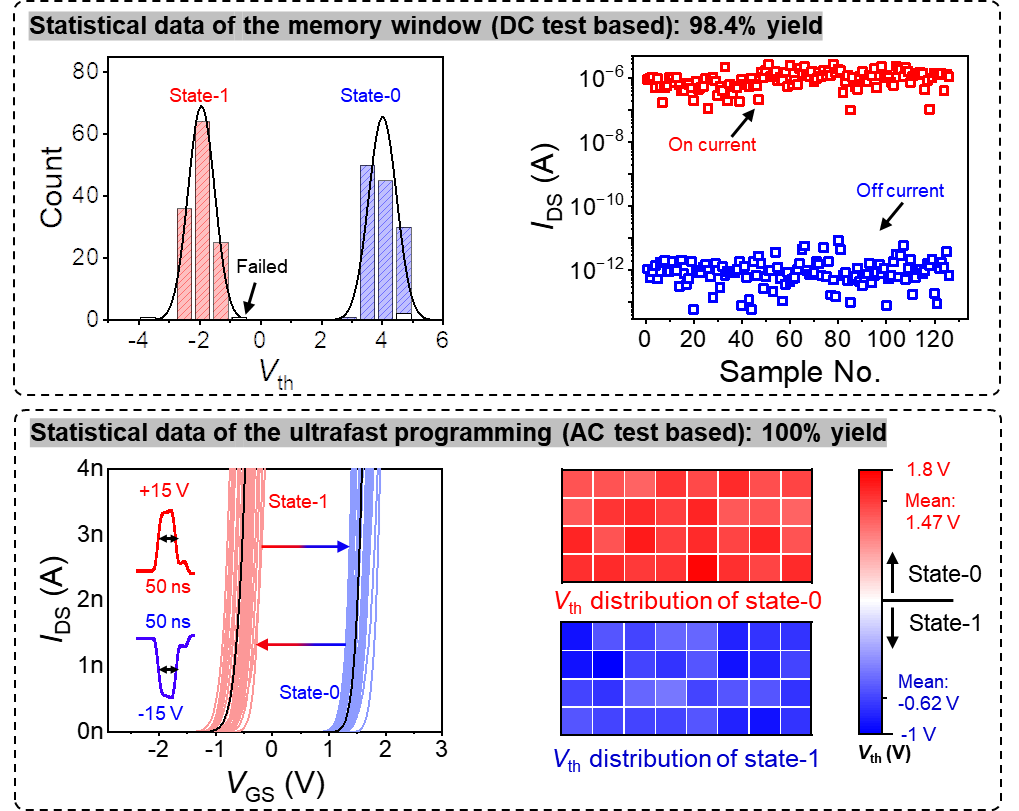

据复旦大学微电子学院官方消息,近日,复旦大学周鹏-刘春森团队《二维超快闪存的规模集成工艺》(“A scalable integration process for ultrafast two-dimensional flash memory”)论文发表于国际顶尖期刊《自然-电子学》(Nature Electronics)上,该团队报告了一种可扩展的超快2D闪存集成过程,可用于集成1,024 个闪存设备,产率超过98%。

复旦大学周鹏-刘春森团队从界面工程出发,团队在国际上首次验证了1kb超快闪存阵列集成验证,并证明了超快特性可延伸至亚10纳米。其前期研究表明二维半导体结构能够将速度提升一千倍以上,实现颠覆性的纳秒级超快存储闪存。然而,如何实现规模集成、走向实际应用极具挑战。

超快闪存集成工艺和统计性能

团队开发了超界面工程技术,在规模化二维闪存中实现了具备原子级平整度的异质界面,结合原子级精度的表征技术,验证集成工艺显著优于国际水平。通过严格的直流存储窗口、交流脉冲存储性能测试,证实了二维闪存在1Kb存储规模中,纳秒级非易失编程速度下良率高达98%,这一良率已高于国际半导体技术路线图(International Technology Roadmap for Semiconductors)对闪存制造89.5%的良率要求。

同时,研究团队研发了不依赖先进光刻设备的自对准工艺,结合原始创新的超快存储叠层电场设计理论,成功实现了沟道长度为8纳米的超快闪存器件,是目前最短沟道闪存器件,并突破了硅基闪存物理尺寸极限(约15纳米)。在原子级薄层沟道支持下,这一超小尺寸器件具备20纳秒超快编程、10年非易失、十万次循环寿命和多态存储性能。有望推动超快颠覆性闪存技术产业化。

据悉,复旦大学集成芯片与系统全国重点实验室、芯片与系统前沿技术研究院刘春森研究员和微电子学院周鹏教授为论文通讯作者,刘春森研究员和博士生江勇波、曹振远为论文第一作者。研究工作得到了科技部重点研发计划、基金委重要领军人才计划、上海市基础特区计划、上海市启明星等项目的资助,以及教育部创新平台的支持。

清华集成电路学院南天翔课题组合作提出一种基于磁振子的新型逻辑器件

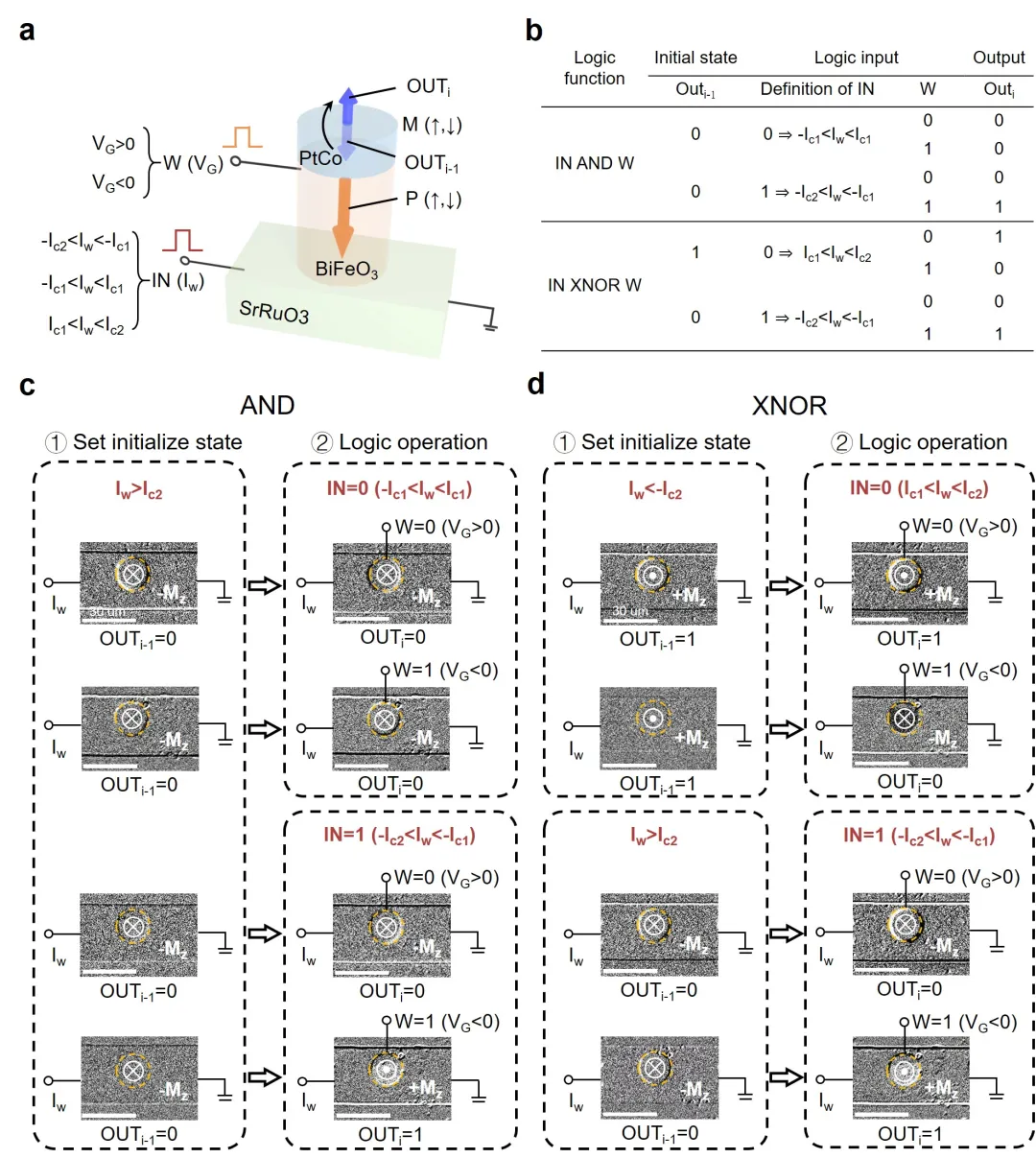

此外,近日清华大学集成电路学院南天翔课题组及合作者提出利用电压原位控制铁酸铋异质结构中的多铁磁振子自旋力矩,从而实现可重构逻辑存储器。目前相关研究成果已经以“电压调控多铁磁振子力矩实现可重构逻辑存储器”(Voltage control of multiferroic magnon torque for reconfigurable logic-in-memory)为题,在线发表在《自然·通讯》(Nature Communications)上。

图1 多铁性磁振子自旋力矩器件的工作原理

据悉,内存计算利用能够在同一设备内同时执行信息存储和逻辑运算的非易失性存储器,有望在显著降低能耗的同时增强人工智能传输,而该过程不可避免地会产生焦耳热。

近期该研究发现,磁振子可以在亚铁磁和反铁磁绝缘体中传输自旋而不涉及电荷运动,在作为信息载体处理和传输信息时不产生明显的热耗散,是开发低耗散自旋逻辑-存储设备的有效途径。非相干磁振子可以在直流电路中被电(或者热)激发,使其与当前的半导体技术兼容。另一方面,在实际应用中,通过施加栅极电压来实现磁振子逻辑运算也十分重要。然而,目前在室温下操纵磁振子流传输的技术主要依赖于通过施加磁场来重新调整磁性序或调节磁畴结构。

该研究将多铁性材料与磁振子存储器相结合进行电路设计,利用多铁性材料实现对磁振子力矩的非易失性调控,并提出了一种栅极电压调控可重构磁振子逻辑存储器。该逻辑存储器包括多个位于同一个电流通道上的铁磁/多铁性铁酸铋BiFeO3存储单元。通过在电流通道中施加电流脉冲,可以在多铁性材料中产生非相干磁振子流,并通过磁振子力矩将自旋信息并行地、非易失性地写入多个存储单元。通过原位施加栅极电压脉冲翻转铁电极化,实现了对磁振子自旋传输的非易失性控制。

研究团队进一步提出并演示了一种基于多铁性磁振子自旋力矩的可重构逻辑存储器。这赋予了该逻辑存储器在不改变电路拓扑的情况下,可以被重构实现16种布尔代数运算的能力。该器件减少了中间计算参数复制的必要性,显著降低了内存区域开销和功耗,并消除了断电后重新加载数据的需要。这些特点凸显了多铁性磁振子器件在低功耗存内计算方面的潜力。

图2 室温下基于磁振子力矩的信息写入

图3 室温下原位非易失性电压调控磁振子力矩

图4 基于多铁性磁振子力矩的可重构逻辑存储器

该论文清华大学集成电路学院副教授南天翔、材料学院副教授易迪和教授林元华为通讯作者,清华大学集成电路学院博士后柴亚红、博士后梁宇晗、2022级博士生肖灿诚为论文共同第一作者。其他重要合作者还包括清华大学集成电路学院教授吴华强、副教授唐建石,材料学院教授谷林、副教授马静,物理系教授于浦、副教授江万军,高等研究院博士后李博,中国科学院物理所副研究员张庆华等。

封面图片来源:拍信网