分享一个以前调试的ADF4350设计笔记,可输出0dB本振信号。网上有很多成功的设计案例,但是调试的时候会遇到很多其他问题,所以只能在设计的时候考虑全面。ADF4350具有一个集成电压控制振荡器(VCO),其基波输出频率范围为2200-4400MHz。此外,利用1/2/4/8/16分频电路,用户可以产生低至137.5 MHz的RF输出频率。对于要求隔离的应用,RF输出级可以实现静音。静音功能既可以通过引脚控制,也可以通过软件控制。同时提供辅助RF输出,且不用时可以关断。

一、原理图设计

电路图设计可以参考官网设计,这边放一张我设计的原理图,但是实际中往往用不到4个本振信号。如果不想用差分输出也可以端接50欧姆电阻,如果幅度小的话直接串个耦合电容接个放大器即可。另外2200 MHz至4400 MH是直接合成的,其他分频均有谐波分量较高的情况。

这里要注意一下:

1.有源晶振输入电平在0.7V-AVDD之间(1/2AVDD偏置),所以在晶振电源端有个分压电路(R17,R16),另外提醒一下TCXO有两种输出方式:CMOS和clipped sine两种类型的,本振的话还是选clipped sine比较理想,CMOS的话谐波比较大,会抬升本振源的底噪。

2.对于环路滤波的选择个人感觉ADIPLLsim工具是真的好,选好芯片,输出频率范围,鉴相频率,环路滤波器种类设置好,确定环路带宽,滤波器就出来了,然后微调把理想电容电阻换成实际的就可以了。(有个小技巧,就是参考评估板上面的环路滤波器进行配置,懒的配的话,上面电路的值也是可以用的,环路滤波器带宽大点是比较容易锁定的,后续锁定后可以再慢慢调试)

3. 看官网参考程序CE拉高就可以了,其他直接单片机用模拟SPI口写就好(CLK,DATA,LE),LD锁相指示灯亮就锁定了,还有个小技巧是如果锁相环出不来频率的话,第一步看看晶体有没有频率输出(示波器显示的话波形不好看不要紧,只要频率对,幅度在范围内就好,和你的示波器带宽有关);第二步再用示波器去抓取SPI波形,看看时序是不是和写的一样的;第三步,在前面两步良好的话用示波器探针点MUXOUT,看N和R分频情况(剩下自己分析吧,没啥东西了。。)---这个时候就体现出TP点的重要性了。

4.配置还是官网给的软件Anolog devices ADF435X software 简洁明了,六个寄存器(R0-R5)一目了然。

我的配置程序(网上大神分享的,注释可能不对。。。。)

/*-------------------------------------868MHz------------------------------

Reference frequency: 25MHz;Output frequency: 200MHz;VCO frequency: 3200MHz;Prescaler: 8/9;

Output divider: 16;VCO channel spacing frequency: 1600KHz;PFD frequency: 10MHz;

INT: 320;FRAC: 0;MOD: 6;R: 1;Clk Div: 80;Phase: 1

--------------------------------------------------------------------------*/

buf[3] = 0x00;

buf[2] = 0x58;

buf[1] = 0x00; //write communication register 0x00580005 to control the progress

buf[0] = 0x05; //to write Register 5 to set digital lock detector

WriteToADF4350(4,buf);

buf[3] = 0x00;

buf[2] = 0xAD; //(DB23=1)The signal is taken from the VCO directly;(DB22-20:4H)the RF divider is 16; (DB19-12:50H)R is 80

buf[1] = 0x00; //(DB11=0)VCO powerd up;

buf[0] = 0x6C; //(DB5=1)RF output is enabled; (DB43=3H)Output power level is 5

WriteToADF4350(4,buf);

buf[3] = 0x00;

buf[2] = 0x00;

buf[1] = 0x04; //(DB14-3:96H)clock divider value is 150.

buf[0] = 0xB3;

WriteToADF4350(4,buf);

buf[3] = 0x0C;

buf[2] = 0x00; //(DB6=1)set PD polarity is positive; (DB7=1)LDP is 6nS;

buf[1] = 0x4E; //(DB8=0)enable fractional-N digital lock detect;

buf[0] = 0x42; //(DB12-9:7H)set Icp 2.50 mA;

WriteToADF4350(4,buf);

//(DB23-14:1H)R counter is 1

buf[3] = 0x08;

buf[2] = 0x00;

buf[1] = 0x80; //(DB14-3:6H)MOD counter is 6;

buf[0] = 0x69; //(DB26-15:6H)PHASE word is 1,

neither the phase resync

WriteToADF4350(4,buf);

//nor the spurious optimization

functions are being used

buf[3] = 0x00; //(DB27=1)prescaler value is 8/9

buf[2] = 0x42;

buf[1] = 0x80;

buf[0] = 0x38; //(DB14-3:0H)FRAC value is 0;

WriteToADF4350(4,buf);

//(DB30-15:140H)INT value is 320;

二. 单片机的选型

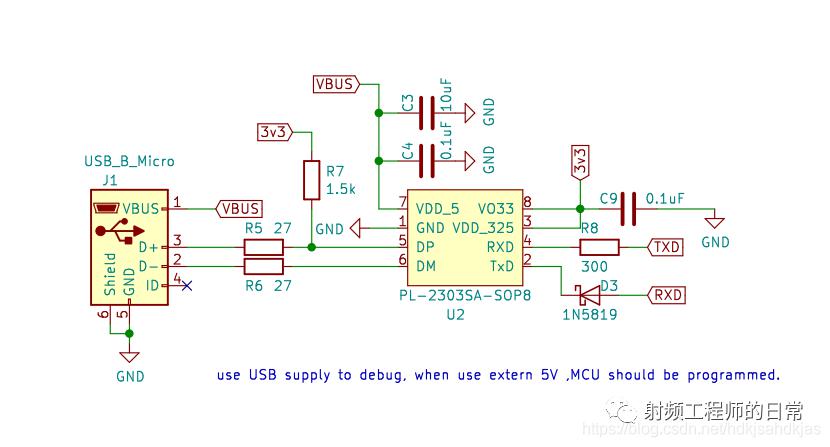

单片机直接选的STC15的SOP16封装的,主要就16个脚,搭个最小系统板就解决了,比较方便的是还不要外部晶振和复位电路;下载串口选用的是USB转TTL,没遇到什么问题。但是STC单片机下载的时候需要注意的是重新上电,可以在单片机电源端加一个开关,注意开关不能把USB串口的电断了。另外再填一个坑,就是使用stc-isp-15xx-v6.85M或者某些版本下载hex文件的时候,必须把波特率改成4800或者14400这些波特率,因为对于PL2303串口存在些bug,反正就是不行就换下波特率。其他的大家自己注意吧。

这里放一张USB转串口的图,个人觉得这款芯片比较好。

三. 关于layout

低速板逻辑控制部分比较placement和Layout比较容易,走线通了就好,射频部分线还是越短越好,电容或电感就近打孔下地,电感不平行放,另外Sub1GHz的应用根据你自己的产品走线,注意基本的射频规则就可以了。记录一下,后面有时间再看看。