一、

本文引用地址:DDR的电源可以分为三类:

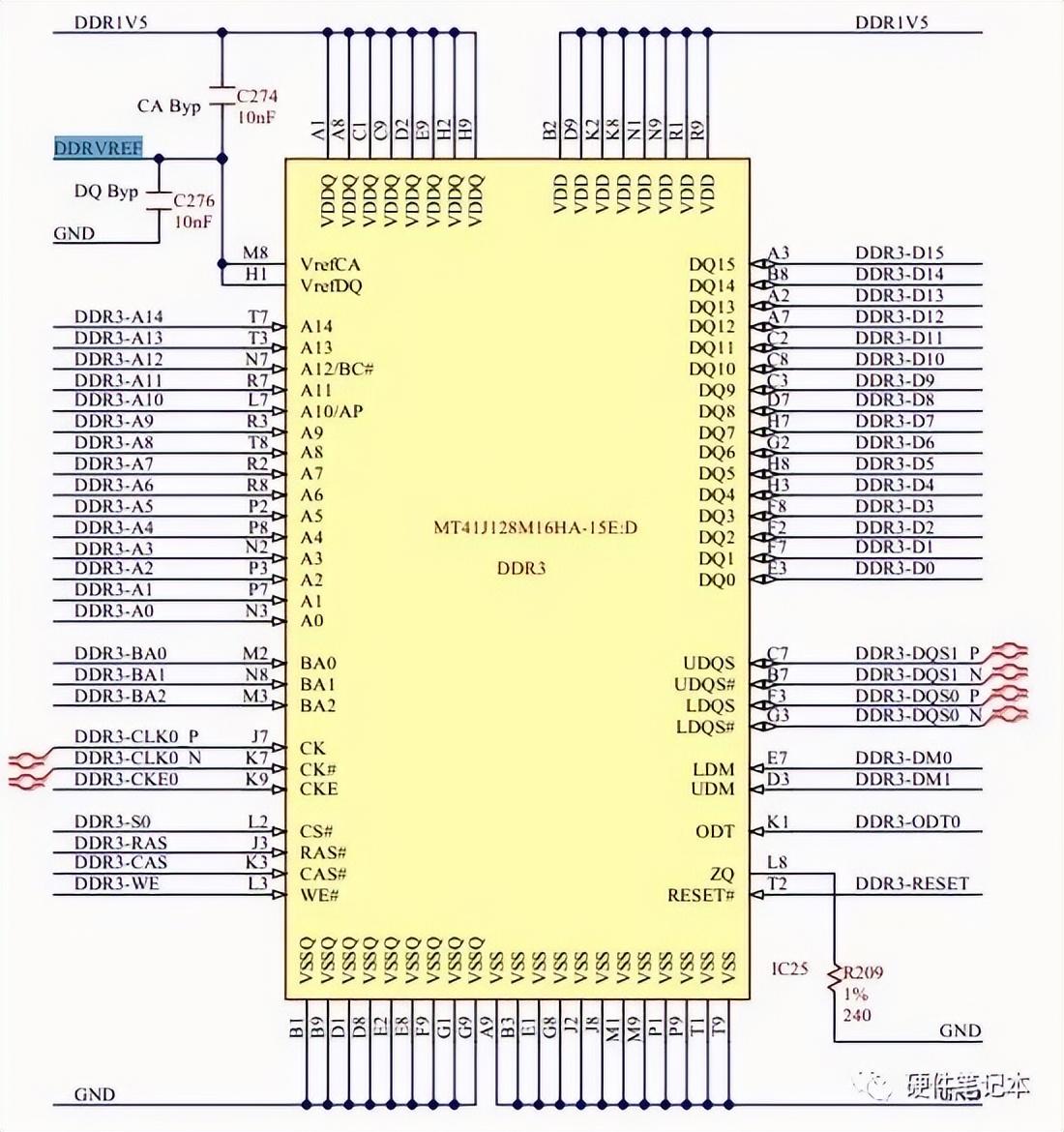

1.1 主电源VDD和VDDQ

主电源的要求是VDDQ=VDD,VDDQ是给IO

buffer供电的电源,VDD是给但是一般的使用中都是把VDDQ和VDD合成一个电源使用。有的芯片还有VDDL,是给DLL供电的,也和VDD使用同一电源即可。

电源设计€€时,需要考虑电压,电流是否满足要求,电源的上电顺序和电源的上电时间,单调性等。

电源电压的要求一般在±5%以内。

电流需要根据使用的不同芯片,及芯片个数等进行计算。由于DDR的电流一般都比较大,所以PCB设计时,如果有一个完整的电源平面铺到管脚上,是最理想的状态,并且在电源入口加大电容储能,每个管脚上加一个100nF~10nF的小电容滤波。

1.2 参考电源Vref

参考电源Vref要求跟随VDDQ,并且Vref=VDDQ/2,所以可以使用电源芯片提供,也可以采用电阻分压的方式得到。由于Vref一般电流较小,在几个mA~几十mA的数量级,所以用电阻分压的方式,即节约成本,又能在布局上比较灵活,放置的离Vref管脚比较近,紧密的跟随VDDQ电压,所以建议使用此种方式。需要注意分压用的电阻在100~10K均可,需要使用1%精度的电阻。

Vref参考电压的每个管脚上需要加10nF的点容滤波,并且每个分压电阻上也并联一个电容较好。

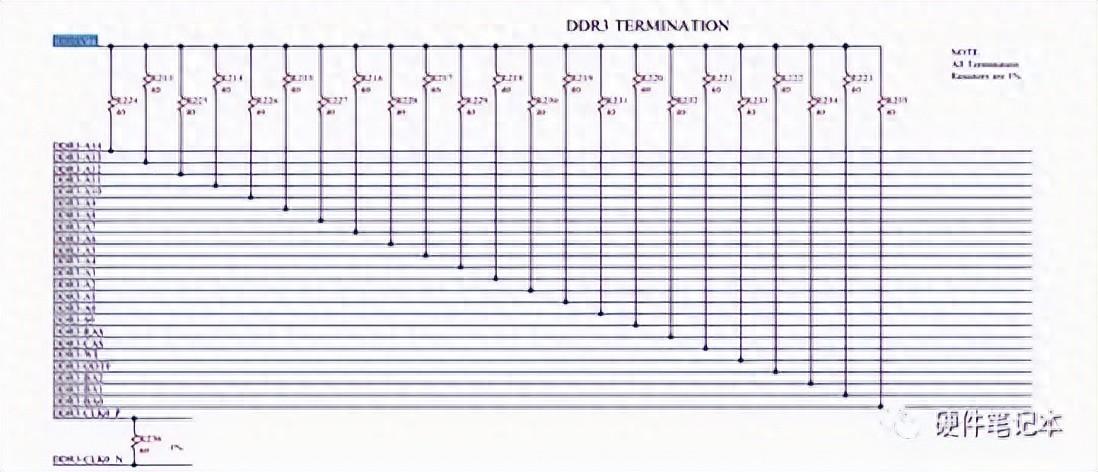

1.3 用于匹配的电压VTT(Tracking Termination Voltage)

VTT为匹配电阻上拉到的电源,VTT=VDDQ/2。DDR的设计中,根据拓扑结构的不同,有的设计使用不到VTT,如控制器带的DDR器件比较少的情况下。如果使用VTT,则VTT的电流要求是比较大的,所以需要走线使用铜皮铺过去。并且VTT要求电源即可以提供电流,又可以灌电流(吸电流)。一般情况下可以使用专门为DDR设计的产生VTT的电源芯片来满足要求(曾经使用过程中用了简单的线性稳压器也没发现出现什么问题,这种方式还是不建议的!)。

而且,每个拉到VTT的电阻旁一般放一个10Nf~100nF的电容,整个VTT电路上需要有uF级大电容进行储能。

一般情况下,DDR的数据线都是一驱一的拓扑结构,且ddr2和ddr3内部都有ODT做匹配,所以不需要拉到VTT做匹配即可得到较好的信号质量。而地址和控制信号线如果是多负载的情况下,会有一驱多,并且内部没有ODT,其拓扑结构为走T点的结构,所以常常需要使用VTT进行信号质量的匹配控制。

从上面简单的介绍可以看到 ,用来匹配的电源VTT是需要SINK/SOURCE的,这就和我介绍的题目扯上关系啦,现在我们的工业级产品中全部使用TI的TPS51200,电路简单实用,低成本,详细的介绍还是多参考一下TPS51200的datasheet。

下面图片是在相关设计的示例,仅供参考。

TPS51200

二、拉电流source和灌电流sink

2.1 拉电流灌电流名词解释

一个重要的前提:灌电流和拉电流是针对端口而言的,而且都是针对IC的输出端口。名词解释——灌:注入、填充,由外向内、由虚而实。渴了,来一大杯鲜榨橙汁,一饮而尽,饱了,这叫“灌”。灌电流(sink current) ,对一个端口而言,如果电流方向是向其内部流动的则是“灌电流”,比如一个IO通过一个电阻和一个LED连接至VCC,当该IO输出为逻辑0时能不能点亮LED,去查该器件手册中sink current参数。名词解释——拉:流出、排空,由内向外,由实而虚。一大杯鲜橙汁喝了,过会儿,憋的慌,赶紧找卫生间,一阵“大雨”,舒坦了,这叫“拉”。拉电流(sourcing current),对一个端口而言,如果电流方向是向其外部流动的则是“拉电流”,比如一个IO通过一个电阻和一个LED连至GND,当该IO输出为逻辑1时能不能点亮LED,去查该器件手册中sourcing current参数。

2.2 概念

拉电流和灌电流是衡量电路输出驱动能力(注意:拉、灌都是对输出端而言的,所以是驱动能力)的参数,这种说法一般用在数字电路中。这里首先要说明,芯片手册中的拉、灌电流是一个参数值,是芯片在实际电路中允许输出端拉、灌电流的上限值(允许最大值)。而下面要讲的这个概念是电路中的实际值。由于数字电路的输出只有高、低(0,1)两种电平值,高电平输出时,一般是输出端对负载提供电流,其提供电流的数值叫“拉电流”;低电平输出时,一般是输出端要吸收负载的电流,其吸收电流的数值叫“灌(入)电流”。

对于输入电流的器件而言:灌入电流和吸收电流都是输入的,灌入电流是被动的,吸收电流是主动的。如果外部电流通过芯片引脚向芯片内‘流入’称为灌电流(被灌入);反之如果内部电流通过芯片引脚从芯片内‘流出’称为拉电流(被拉出)

2.3 为什么能够衡量输出驱动能力

当逻辑门输出端是低电平时,灌入逻辑门的电流称为灌电流,灌电流越大,输出端的低电平就越高。由三极管输出特性曲线也可以看出,灌电流越大,饱和压降越大,低电平越大。然而,逻辑门的低电平是有一定限制的,它有一个最大值UOLMAX。在逻辑门工作时,不允许超过这个数值,TTL逻辑门的规范规定UOLMAX ≤0.4~0.5V。所以,灌电流有一个上限。

当逻辑门输出端是高电平时,逻辑门输出端的电流是从逻辑门中流出,这个电流称为拉电流。拉电流越大,输出端的高电平就越低。这是因为输出级三极管是有内阻的,内阻上的电压降会使输出电压下降。拉电流越大,输出端的高电平越低。然而,逻辑门的高电平是有一定限制的,它有一个最小值UOHMIN。在逻辑门工作时,不允许超过这个数值,TTL逻辑门的规范规定UOHMIN ≥2.4V。所以,拉电流也有一个上限。

可见,输出端的拉电流和灌电流都有一个上限,否则高电平输出时,拉电流会使输出电平低于UOHMIN;低电平输出时,灌电流会使输出电平高于UOLMAX。所以,拉电流与灌电流反映了输出驱动能力。(芯片的拉、灌电流参数值越大,意味着该芯片可以接更多的负载,因为,例如灌电流是负载给的,负载越多,被灌入的电流越大)

由于高电平输入电流很小,在微安级,一般可以不必考虑,低电平电流较大,在毫安级。所以,往往低电平的灌电流不超标就不会有问题。用扇出系数来说明逻辑门来驱动同类门的能力,扇出系数No是低电平最大输出电流和低电平最大输入电流的比值。在集成电路中, 吸电流、拉电流输出和灌电流输出是一个很重要的概念。拉即泄,主动输出电流,是从输出口输出电流。灌即充,被动输入电流,是从输出端口流入吸则是主动吸入电流,是从输入端口流入吸电流和灌电流就是从芯片外电路通过引脚流入芯片内的电流,区别在于吸收电流是主动的,从芯片输入端流入的叫吸收电流。灌入电流是被动的,从输出端流入的叫灌入电流。

拉电流是数字电路输出高电平给负载提供的输出电流,灌电流时输出低电平是外部给数字电路的输入电流,它们实际就是输入、输出电流能力。吸收电流是对输入端(输入端吸入)而言的;而拉电流(输出端流出)和灌电流(输出端被灌入)是相对输出端而言的。