如今,电路板设计人员面临着多种 保护选择。设计人员通常会受到某些限制的限制,例如他/她的应用可以承受的寄生电容量或电路板必须通过的所需 级别。通常,这些限制不会将可用的 设备数量缩小到可管理的列表。本白皮书将为设计人员提供指导,帮助他/她选择 ESD 器件,从而地实现成功的设计。

本文引用地址:如今,电路板设计人员面临着多种 ESD 保护选择。设计人员通常会受到某些限制的限制,例如他/她的应用可以承受的寄生电容量或电路板必须通过的所需 ESD 级别。通常,这些限制不会将可用的 ESD 设备数量缩小到可管理的列表。本白皮书将为设计人员提供指导,帮助他/她选择 ESD 器件,从而地实现成功的设计。

选择合适的 ESD 器件

如今,电路板设计人员面临着多种 ESD 保护选择。设计人员通常会受到某些限制的限制,例如他/她的应用可以承受的寄生电容量或电路板必须通过的所需 ESD 级别。通常,这些限制不会将可用的 ESD 设备数量缩小到可管理的列表。本白皮书将为设计人员提供指导,帮助他/她选择 ESD 器件,从而地实现成功的设计。

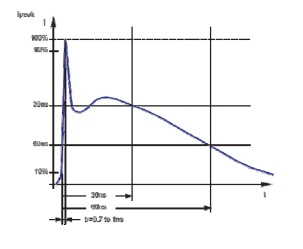

在讨论选择标准之前,让我们回顾一下一些基本的 ESD 拓扑及其典型的“开启”特性。(注:本文中引用的 ESD 威胁/脉冲是由 IEC61000-4-2 标准定义的,如图 1 所示。)

背景

目前市场上有多种类型的 ESD 抑制器件。示例包括 MLV(多层压敏电阻)、聚合物 ESD 抑制器以及硅二极管或阵列。为简单起见,本文将仅关注硅器件,因为它们的性能在 ESD 钳位能力方面往往更为优越。尽管如此,下文讨论的要点可以普遍适用于任何 ESD 设备,无论其技术如何。

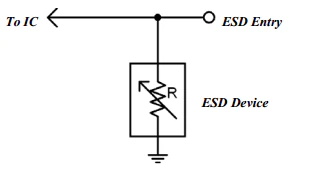

两种常见的硅保护器件是 TVS/齐纳二极管(图 2)和二极管/??轨夹(图 3),它们均旨在在 ESD 事件期间提供通向 GND 的低电阻分流路径。(两者之间的主要区别在于每个结构将添加到受保护的 I/O 上的寄生电容量。)

每种结构均旨在引导正负 ESD 脉冲远离受保护的 IC。对于正瞬变,图 2 中的 TVS/齐纳二极管将在达到电压 VZ(通常为 6-8V)后“开启”,并向 GND 提供电阻分流。同样,当达到电压 VF +VZ(通常为 6-8V)时,图 3 中的二极管阵列将引导正电流通过“上部”二极管并进入内部 TVS 器件。对于负 ESD 脉冲,两种结构的行为相同,即当超出 -VF(通常为 0.6-0.8V)或受保护总线的二极管压降低于 GND 时,它们都会导通。牢记这一基本理解,让我们检查 ESD 供应商在其器件数据表中通常给出的电气特性。