华为意大利研究中心与瑞士苏黎世理工学院系统集成实验室联合发表了一篇论文《Towards a RISC-V Open Platform for Next-generation Automotive ECUs》透露出华为或许正在开发下一代基于RISC-V的车载MCU,论文发表于2023年7月。目前,华为海思已有两款基于RISC-V的芯片,分别是Hi3731v110和Hi3861,其中前者是一款全球模拟电视用芯片,后者就近似MCU。海思目前还在开发数据中心用RISC-V芯片,可能是AI加速器。

与华为同样思路的还有瑞萨,瑞萨是全球第一大MCU厂家,也是RISC-V MCU投入力度最大的厂家。早在2021年,瑞萨就有RH850/U2B 汽车MCU采用RISC-V内核的DR1000C

CPU IP,这款IP来自日本丰田关联公司电装旗下的NSITEXE公司(成立于2017年,最初是电装的一个实验室,后从电装剥离)。

瑞

萨RH850/U2B内部框架

图片来源:Renesas

DR1000C内部框架图

DR1000C主要是加入了矢量计算单元。图片来源:NISTEXE

除了RH850/U2B,瑞萨还有众多32/64 bit的基于RISC-V内核的MCU,包括非车载领域的RZ/Five系列(AX45MP@1.0GHz,附带SIMD的FPU),语音HMI的R9A06G150,三相电机控制R9A02G020。

简单介绍一下RISC-V。RISC-V中,RISC指的是精简指令集架构。指令集架构(Instruction Set Architecture)是指一种类型CPU中用来计算和控制计算机系统的一套指令的集合。

指令集架构主要规定了指令格式、寻址访存(寻址范围、寻址模式、寻址粒度、访存方式、地址对齐等)、数据类型、寄存器。

指令集通常包括三大类主要指令类型:运算指令、分支指令和访存指令。此外,还包括架构相关指令、复杂操作指令和其他特殊用途指令。因此,一种CPU执行的指令集架构不仅决定了CPU所要求的能力,而且也决定了指令的格式和CPU的结构。X86架构和ARMv8架构就是指令集架构的范畴。指令集架构依其复杂性可被分类为复杂指令集架构(CISC,Complex Instruction Set Computer)和精简指令集架构(RISC,Reduced Instruction Set Computer)两大类。发展至今,CISC和RISC的界限已变得模糊,二者互吸收了各自的优点,变得你中有我,我中有你。

2010 年,RISC构思在加州大学伯克利分校启动,是一个用于开发芯片处理器的免费、非专有平台。RISC的发源也是在伯克利,但RISC不是开源的。

2015年,RISC-V基金会成立,旨在建立一个基于RISC-V ISA的开放、协作的软硬件创新者社区。该基金会是一家由其成员控制的非营利公司,负责指导开发以推动 RISC-V ISA 的初步应用。

2020年3月,RISC-V基金会迁往瑞士,解决了受地缘政治干扰的风险。RISC-V是开源的,这意味着 RISC-V 是免许可和免版税的。RISC-V允许用户免费使用新指令扩展ISA并创新RISC-V处理器的微架构,而当前汽车业内主流的ARM架构,要求用户支付版税。这使得RISC-V迅速受到众多厂商的欢迎。

当前主流的ARM 需要 IP 核许可批准,ARM的商品一是指令集,二是内核架构。不过ARM的内核架构自然要用ARM的指令集,买了ARM的内核架构自然就包含ARM指令集,或者也可以单独设计物理架构,而只使用ARM的指令集,如苹果一直以来都是如此。而高通、华为等则是直接买架构。

ARM指令集的费用为100万美元到1000万美元之间。此外,如果您想更改设计中的任何内容,将需要另外付费,当然可以花上千万美元一次性买断内核架构,这就不需要另外付费。另外每生产一块芯片,ARM都要收取1-3%芯片价格的费用。ARM有大约60%的收入来自版税,40%的收入来自IP授权。2023财年ARM的版税收入只有16.8亿美元,仅占芯片价值的1.7%。不过版税的优点在于一次开发,一生收税,旧芯片能带来持续收入流。2023财年中,ARM约46%的版税收入来自1990-2012年间发布的产品 。

RISC-V 是简化ISA自下而上构建的,可以处理最新的计算工作负载。而RISC-V与拥有数十年历史且背负着遗留的指令专有架构(X86和ARM)有很大不同。X86和ARM已经持续运行了超30年,为应对新应用,指令集变得越来越庞大,效率越来越低,ARM早已不是当年那个纯粹的精简指令。

最重要的是X86和ARM都是封闭的,厂家想要更改指令集完全不可能。在强调互联互通的消费类电子领域,指令集由一家独立公司完全掌控是优势;但在汽车领域是缺点,汽车是嵌入式领域,不用考虑互联互通,各品牌之间完全不兼容是正常的,比如特斯拉的自然不会兼容比亚迪的软件系统。也就是说,整车厂要掌握指令集才能做出自己的特色和体系,而这一点ARM和X86永远无法提供,而目前ARM几乎垄断汽车产业,这样就造成了汽车芯片高度雷同,头部厂家市场占有率极高。要打破这种现象,就必须使用RISC-V。

华为的研究工作刚开始,目前还是基于FPGA的研究。华为使用AMD旗下Xilinx的Zynq Ultrascale+ FPGA,这款FPGA有4核ARM Cortex-A53,每核心有L1缓存32KiB,L2缓存1MiB,运行频率1.2GHz,还有一个用于实时任务的ARM Cortex-R5F,RISC-V采用CVA6架构。这种设计可以对比RISC-V和ARM之间的性能差别。

图片来源:《Towards a RISC-V Open Platform for Next-generation Automotive ECUs》

软件架构如上图,非安全苛刻任务采用无人驾驶领域常见的ROS2,中间件采用DDS(数据分发服务),DDS负责管理分布式系统的数据和通信。DDS中间件协议基于对象管理组织®(OMG)标准化的发布-订阅模式。DDS已集成到各种关键的汽车平台生态合作体系中,例如AUTOSAR Adaptive和ROS2。DDS提供低延迟数据连接、可靠性和可扩展的以数据为中心的通信。

此外,DDS附带了一组丰富的内置服务质量(QoS)策略,可控制DDS行为,如资源消耗和通信可靠性。面向资源极度受限环境的DDS通过使用OMG DDS-XRCE协议实现。这是客户端到代理协议,意味着DDS-XRCE客户端节点通过外部代理节点与DDS进行网络通信。DDS-XRCE非常适合为物联网设备开发轻量级DDS应用。实时操作系统采用企业版ERIKA,这是一款免专利的汽车OSEK/VDX认证的硬实时操作系统(RTOS)。

ERIKA主要特性

图片来源:《Towards a RISC-V Open Platform for Next-generation Automotive ECUs》

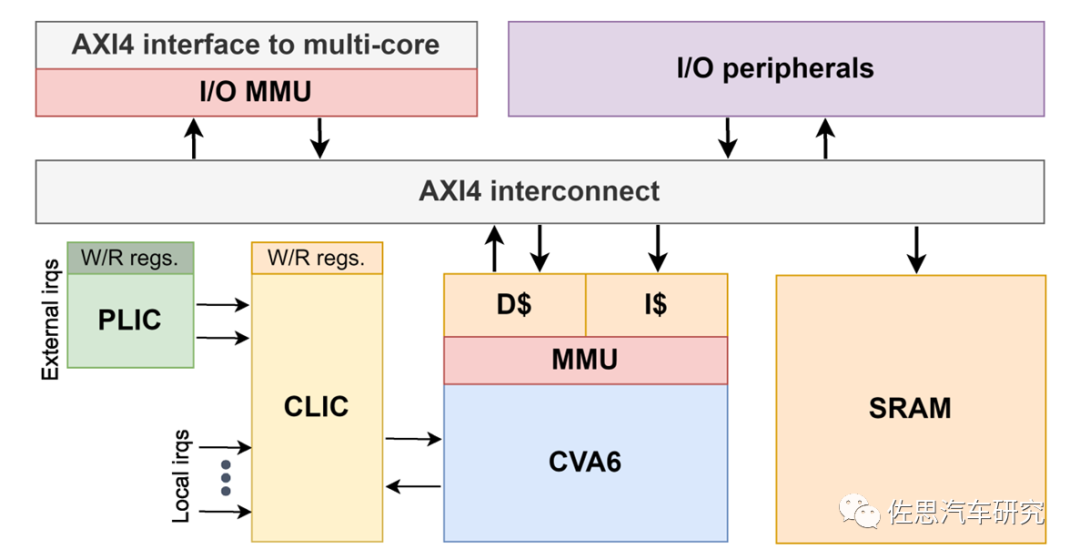

CVA6 MCU结构

图片来源:《Towards a RISC-V Open Platform for Next-generation Automotive ECUs》

CVA6架构

CVA6是一颗具备6级流水、单发射、顺序执行的64bit RISC-V CPU,不仅实现了RV64IMAFDC(RV64GC)指令,也实现了RISC-V三种特权等级,因此具备运行Linux系统的能力。CVA6是苏黎世理工学院与意大利博洛尼亚大学联合的OPENHW机构维护的开源硬件IP。顺便说一句,博洛尼亚大学是全球最古老的大学,成立于公元1088年,目前在意大利排名第五。

CVA6实现了RISC-V的三种特权模式,分别是机器模式(M-Machine Mode)、监督模式(S-Supervisor Mode)、用户模式(U-User Mode);具备ITLB、DTLB、PTW实现虚拟地址到物理地址的快速翻译;具备可灵活配置的4路组相连L1ICache与L1DCache。官方(即OPENHW)基于22nm-FDSOI流片,运行频率可达1.7GHZ。

CVA6核心部分仅具有L1Cache,为了提高流水线效率,L1Cache又分为ICache、DCache。

L1ICache的默认配置是:

cache size:16Kib;

cache lines:128bit;

Associativity:Four-way set;

Replacement policies:使用LFSR进行随机替换。

CVA6仅具有L1Cache,但结合Princeton开源的OpenPiton,可以拓展L2Cache。

CLINTCVA6、Cortex-R5和Cortex-A53的RTOS性能对比

图片来源:《Towards a RISC-V Open Platform for Next-generation Automotive ECUs》

上图,RTOS下表现,RISC-V的CVA6全面胜出。

2023年8月,汽车行业四巨头和挪威NORDIC半导体公司联合投资建立一家致力于RISC-V的芯片公司,算是后知后觉者了。

图片来源:《Towards a RISC-V Open Platform for Next-generation Automotive ECUs》

Zonal或者说SOA时代,对MCU的运算要求越来越高,同时还要应对苛刻的功能安全以及复杂的操作系统、中间件和虚拟机,ARM的CORTEX-R系列已明显力不从心,RISC-V将是未来高性能汽车MCU的首选。