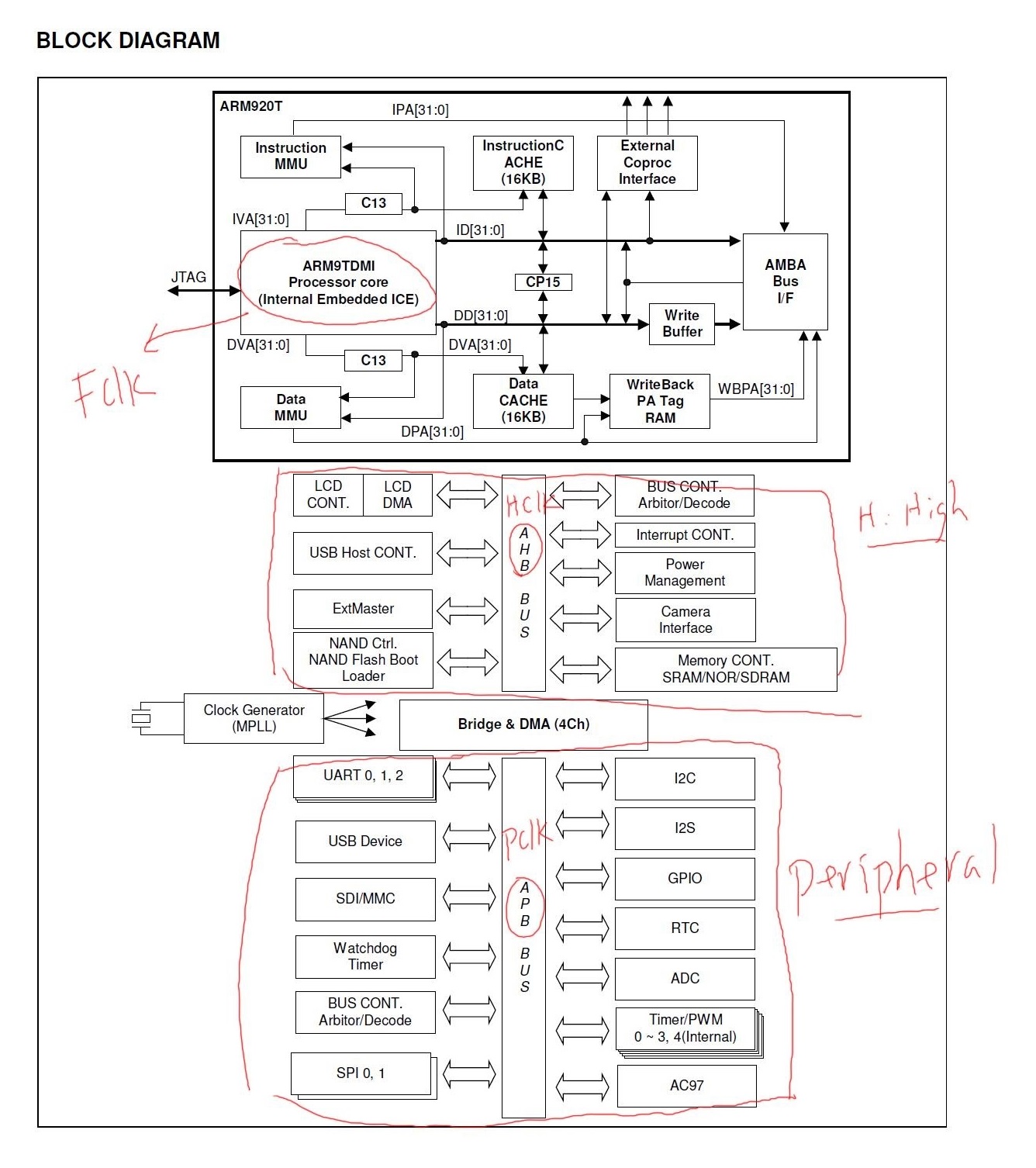

1.总线框架

下图是2440的总线框架,其中有AHB(Advanced High performance Bus)高速总线,APB(Advanced Peripheral Bus)外围总线。

不同总线对应不同的时钟。

SOC FCLK AHB HCLK APB PCLK

其中:

1.使用AHB总线的有:LCD控制器、usb控制器、中断控制器、内存控制器等...

2.使用APB总线的有:i2c、spi、timer、gpio、adc等...具体上图。

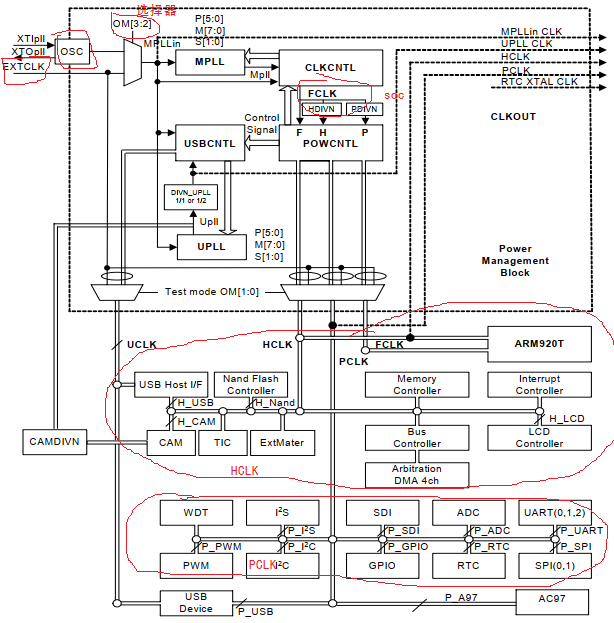

2.时钟框架

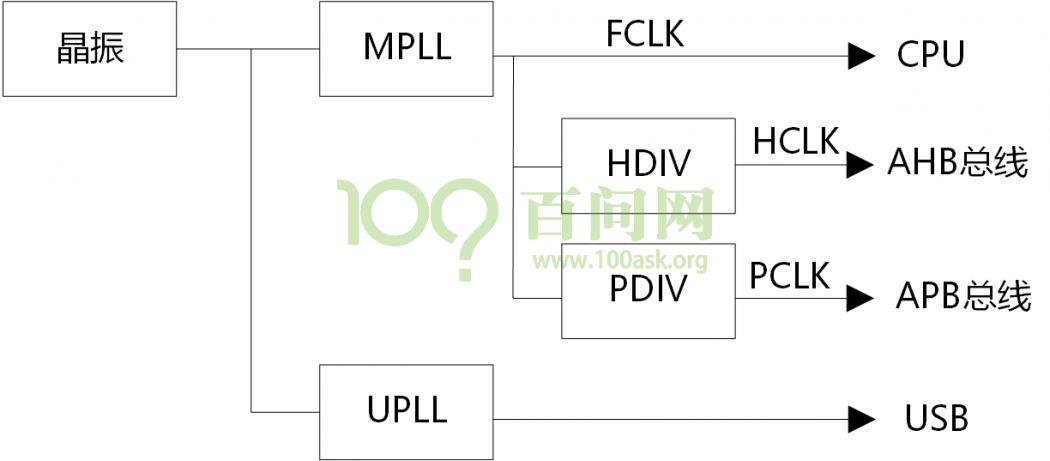

下图表示2440 Soc的时钟框图:

下面从细节上讲解时钟体系:

1.如何选择时钟源:

s3c2440时钟源有2个,一个是OSC,一个是外部时钟EXTCLK,上面的时钟框图有标记,当然大家也可以查看手册“Figure 7-1. Clock Generator Block Diagram”。

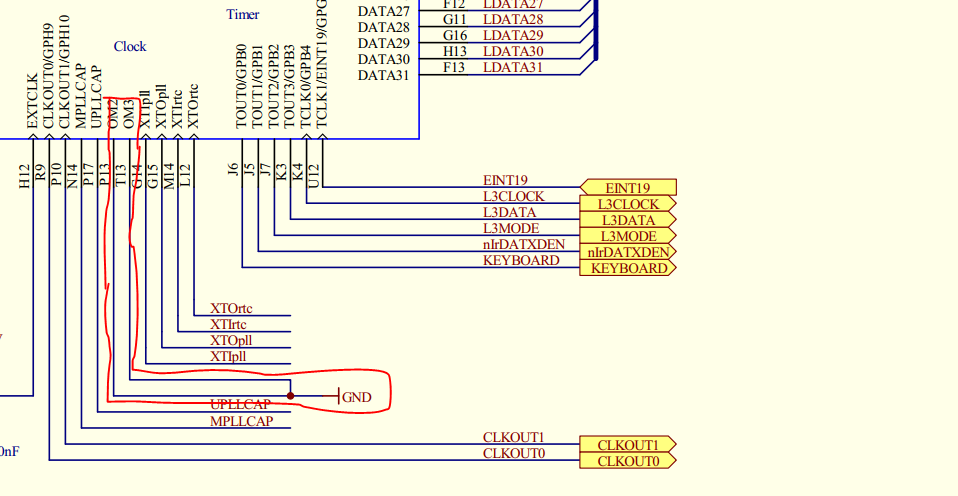

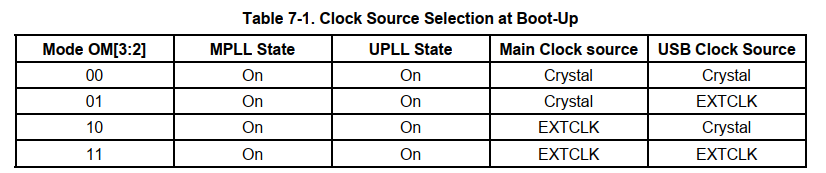

那么如何选择是OSC还是EXTCLK呢?

打开原理图,OM3,OM2的引脚接地,那么OM[3,2]=00.所以根据手册“Table 7-1. Clock Source Selection at Boot-Up”可知时钟源为OSC晶振。

2.如何得到HCLK,PCLK,UCLK?

先了解下PLL, DIV

PLL:用锁相环进行倍频DIV:用分频器进行分频

如下图:

生成的MPLL(Main PLL)和UPLL(USB PLL),MPLL直接提供给FCLK,通过HDIVN分频给HCLK,通过PDIVN分频给PCLK,再传给下面的各个设备。

osc经过UPLL(USB PLL)得到UCLK。