随着全球各地的陆续放开,各种线下活动也逐渐恢复。今年,第 68 届年度 IEEE 国际电子器件会议 (IEDM) 全面恢复,来自世界各地的近 1500 名工程师汇聚一堂,在旧金山一起讨论半导体行业的最新发展内容。

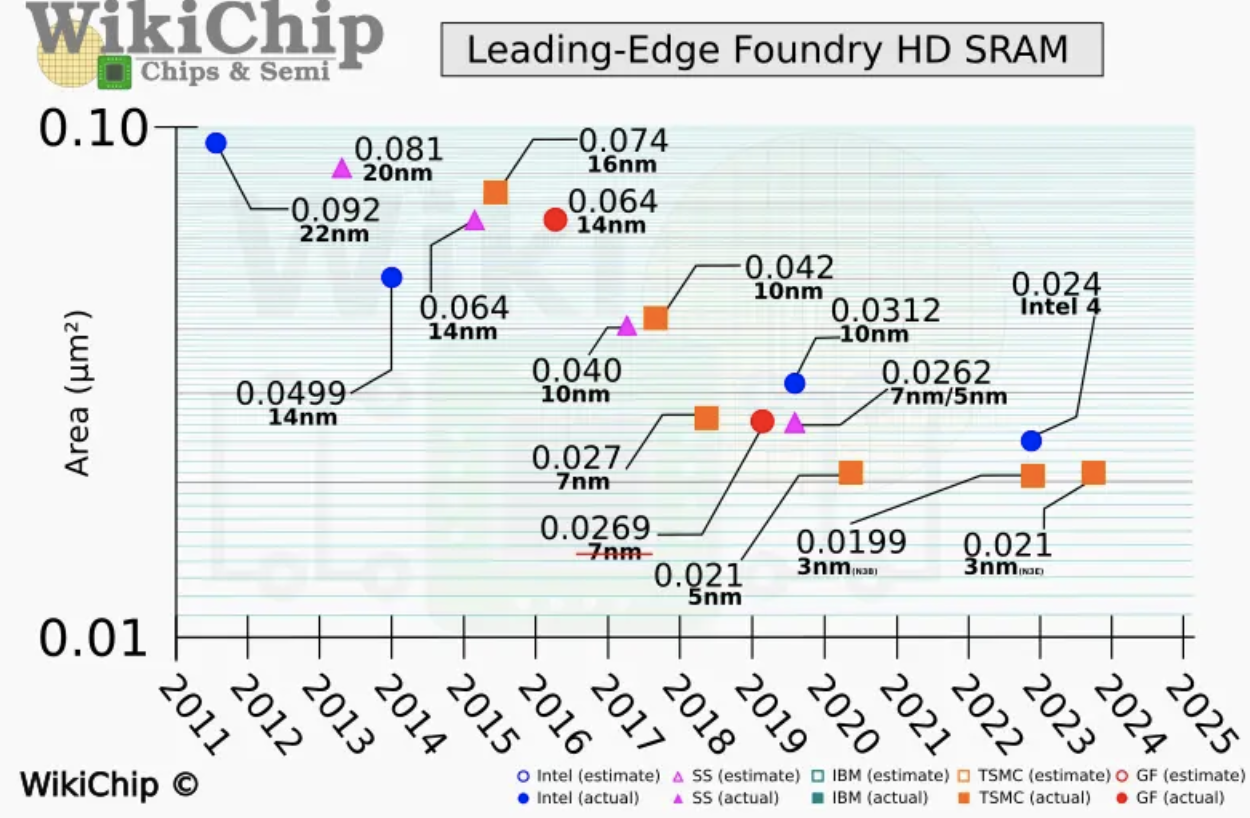

wikichip 从台积电的那篇论文中发现,虽然逻辑电路仍在或多或少地沿着历史轨迹前行,但 SRAM 这方面的路线似乎已经完全崩溃。

台积电在今年早些时候正式推出其 N3 技术时表示,与 N5 相比,新节点的逻辑密度将提高 1.6 倍和 1.7 倍,但他们没有明说的是,与 N5 相比,新技术的 HD SRAM 密度几乎没有任何变化,总体提升聊胜于无,这可能意味着采用新一代 3nm 工艺的 CPU、GPU 成本更高,终端产品也会更贵。

在此次 IEEE 顶会上,台积电谈到了 3nm 基础版 (N3B) 节点以及 3nm 增强型 (N3E) 的部分数据。简单来说,N3E 是 N3B 稍微“廉价”一些的版本,放在最终芯片上可以说相比性能更注重的是功耗控制方面。

有趣的是,对于新的 N3E 节点,高密度 SRAM 位单元尺寸并没有缩小,依然是 0.021 µm²,这与 N5 节点的位单元大小完全相同。但你要知道,N3B 实装了 SRAM 缩放,其单元大小仅有 0.0199µm²,相比上一个版本缩小了 5%。

就粗略地估算一下,N3E 的内存密度(ISO-assist circuit overhead)大约为 31.8 Mib / mm²。

作为对比,英特尔的 Intel 4(原 7nm)将 SRAM 位元尺寸从 0.0312µm² 缩小到了 0.024µm²。当然,目前 Intel 7 (以前称为 10nm Enhanced superin) 大约为 27.8 Mib / mm²,相比起来还是落后于台积电的 HD SRAM 密度。

此外,WikiChip 还回顾了 Imec 的一次演示,PPT 显示在带有叉形晶体管的“超过 2nm 节点”上 SRAM 密度约为 60 Mib / mm²。不过这种工艺技术还需要数年时间,目前芯片行业从业者将不得不开发英特尔和台积电上述 SRAM 密度的半导体。

那么各位可能会问了,这所谓的 SRAM 跟我有什么关系呢?

实际上呢,现代 CPU、GPU 和 SoC 在处理大量数据时都将大量 SRAM 用于各种缓存,因为直接从内存中获取数据效率极低,尤其是对于各种人工智能 (AI) 和机器学习 (ML) 工作负载而言,但是现在大家智能手机中 SoC 的通用处理器、图形芯片和应用处理器都带有不少的缓存,甚至桌面级 AMD Ryzen 9 7950X 带有 81MB 的缓存,而 Nvidia AD102 至少用了 123MB 的 SRAM 缓存。

假设在 TSMC N16 上有一个 100 亿晶体管的芯片,其中 40% 是 SRAM,60% 是逻辑晶体管,假设其芯片面积约为 255mm²,其中 45mm²(或 17.6%) 为 SRAM,而将完全相同的芯片缩小到 N5 将变成一个 56mm² 的芯片,再进一步缩小到 N3 将变成一个 44mm² 的芯片,但 N5 和 N3E 中使用的 SRAM 的面积都是 12.58mm²,这将占据芯片面积的近 30%。

当然,你可能很难感受到这个变化,但对于一些 AI 硬件来说,其架构要求 SRAM 覆盖芯片的很大的百分比,这些工程师将比其他工程师感触更深。

着眼于未来,各行各业对缓存 SRAM 的需求只会增加,而这就导致一时半会很难减少 SRAM 占用的芯片面积,也无法实现与 N5 节点明显的成本收益。从本质上来讲,这意味着高性能处理器的芯片尺寸将会增加,这也会导致它们的成本进一步增加。例如大家经常吐槽的英伟达 RTX 40 系列,其 GPU 芯片就是因为从三星 8nm 直接跳到了最新的台积电 4N 工艺才出现成本大幅提高的情况,但如此来看,哪怕是下一代 RTX 50 系列产品恐怕也很难再回归到之前的“低价”水平了。

从成本角度来看,要想削弱 SRAM 带来的影响的最显著的方法便是采用小芯片设计,并将较大的缓存分解到更便宜的节点上的独立芯片中,也就是 AMD 在其 3D V-Cache 处理器中采取的方案。另一种方法是使用替代内存技术,如 eDRAM 或 FeRAM 作为缓存,不过各种缓存也是各有优势。

无论如何,在 3nm 及以上使用基于 FinFET 的节点减缓 SRAM 缩放速度似乎是未来几年芯片设计人员面临的主要挑战,而对各位而言可能出现的影响就是终端产品涨价,例如搭载 A17 芯片的苹果 iPhone 15 Pro 系列。